# DUAL 3-INPUT 3-OUTPUT | 10210 HIGH PERFORMANCE GATES | 10211

10212

ADVANCE INFORMATION TO BE ANNOUNCED

10210 B. F. 10211 B. F 10212 B. F: -30 to +85°C

DIGITAL 10.000 SERIES ECL

#### DESCRIPTION

The 10210/10211/10212 are designed to drive up to six transmission lines simultaneously. The multiple outputs of these devices also allow the wire-"OR"ing of several levels of gating for minimization of gate and package count.

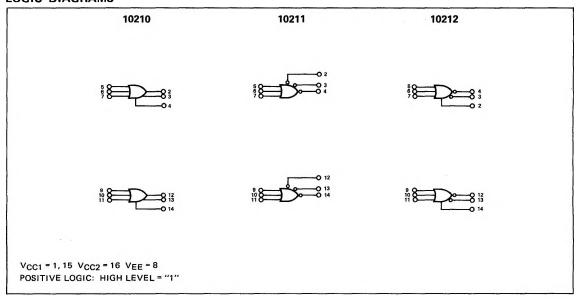

Three logic functions are available:

10210 - Triple OR outputs

10211 - Triple NOR outputs

10212 - Two NOR/One OR Outputs

The 10210/10211/10212 are high performance versions of the 10110/10111/10112.

The ability to control three parallel lines with minimum propagation delay from a single point makes the 10210/10211/10212 particularly useful in clock distribution applications where minimum clock skew is desired. The 10212 is particularly useful as a clock amplifier on a board using clock signals with both polarities.

## **TEMPERATURE RANGE**

−30 to +85°C Operating Ambient

#### PACKAGE TYPES

- B: 16-Pin Silicone Dip

- F: 16-Pin CERDIP

#### **FEATURES**

- FAST PROPAGATION DELAY = 1.7 ns TYP. (ALL OUTPUTS LOADED)

- POWER DISSIPATION = 150 mW/PACKAGE TYP. (NO LOAD)

- VERY HIGH FANOUT CAPABILITY CAN DRIVE SIX 50  $\Omega$  LINES

- INTERNAL 50 kΩ PULLDOWN RESISTORS

- OPEN EMITTERS FOR BUSSING AND LOGIC **CAPABILITY**

# **ELECTRICAL CHARACTERISTICS**

Conditions;  $T_A = 25^{\circ}C$ ,  $V_{EE} = -5.2 \text{ V} \pm 1\%$

1. IE = 38 mA dc max.

2.  $I_{inH} = 425 \,\mu\text{A} \,\text{dc} \,\text{max}$ .

Conditions:  $T_A = 25^{\circ}C$ ,  $V_{CC} = +2.0 \text{ V} \pm 1\%$ , VEE = -3.2 V  $\pm 1\%$ , 50  $\Omega$  loads

3.  $t_{pd} = 1.7 \text{ ns typ.}$

4.  $t_r$ ,  $t_f = 1.5$  ns typ. (20% to 80%)

### LOGIC DIAGRAMS