2527-N • 2528-N • 2529-N

### **DESCRIPTION**

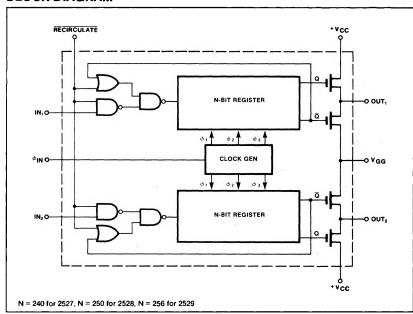

The 2527 240-bit, 2528 250-bit, and the 2529 256-bit recirculating static shift registers consist of enhancement mode p-channel silicon gate MOS devices integrated on a single monolithic chip.

### **TRUTH TABLE**

| RECIRCULATE | INPUT | FUNCTION       |

|-------------|-------|----------------|

| 0           | 0     | Recirculate    |

| 0           | 1     | Recirculate    |

| 1           | 0     | "0" is written |

| 1           | 1     | "1" is written |

### "0" = 0V; "1" = +5V

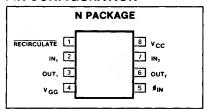

# **PIN CONFIGURATION**

# **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**1

|                  | PARAMETER                                                                                                                                                                      | RATING                                     | UNIT          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------|

| TA<br>TSTG<br>PD | Temperature range <sup>2</sup> Operating Storage Power dissipation at T <sub>A</sub> = 70° C Data and clock input voltages and supply voltages with respect to V <sub>CC</sub> | 0 to 70<br>-65 to 150<br>535<br>0.3 to -20 | °C<br>mW<br>V |

# DUAL 240-BIT STATIC SHIFT REGISTER (240X2) DUAL 250-BIT STATIC SHIFT REGISTER (250X2) DUAL 256-BIT STATIC SHIFT REGISTER (256X2)

2527-N • 2528-N • 2529-N

# DC ELECTRICAL CHARACTERISTICS $T_A = 0^{\circ} \text{C}$ to $70^{\circ} \text{C}$ , $V_{CC} = 5V \pm 5\%$ , $V_{GG} = -12V \pm 5\%$ unless otherwise specified.

| PARAMETER  |                       |                                                                            |          | LIMITS |      |    |

|------------|-----------------------|----------------------------------------------------------------------------|----------|--------|------|----|

|            |                       | TEST CONDITIONS                                                            | Min Typ  | Max    | UNIT |    |

|            | Input voltage3        |                                                                            |          |        |      | V  |

| $V_{IL}$   | Low                   |                                                                            |          |        | 0.6  | l  |

| ViH        | High                  |                                                                            | 3.4      |        | 5.3  | ł  |

| VILC       | Clock low             |                                                                            | 1        |        | 0.6  |    |

| VIHC       | Clock high            |                                                                            | 3.4      | 1      | 5.3  |    |

|            | Output voltage        |                                                                            |          |        |      | V  |

| Vol        | Low                   | $I_{OL} = 1.6 mA$                                                          |          |        | 0.5  | l  |

| Vон        | High                  | $I_{OH} = 100 \mu A$                                                       | 3.8      |        |      |    |

| lu         | Input load current    | V <sub>IN</sub> = 5.5V, T <sub>A</sub> = 25°C                              |          | 10     | 500  | nA |

| ILC        | Clock leakage current | $V_{ILC} = OV, T_A = 25^{\circ}C$                                          |          | 10     | 500  | nA |

| IGG        | Supply current        | Continuous operation, $T_A = 25^{\circ}C$ , $f = 1.5MHz$ ,<br>Outputs open |          | 28     | 35   | mA |

|            | Capacitance           | At 1MHz, V <sub>AC</sub> = 25mV p-p                                        | <b>†</b> |        |      | pF |

| CIN        | Input                 | VIN = VCC                                                                  |          |        | 5    | '  |

| $C_{\phi}$ | Clock                 | $V_{\phi} = V_{CC}$                                                        |          |        | 5    |    |

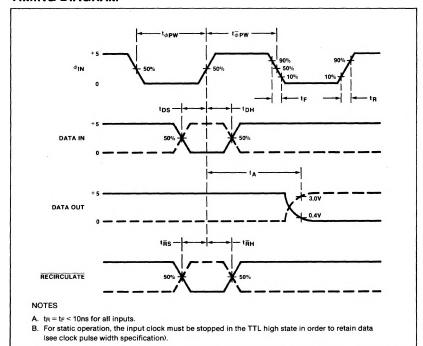

AC ELECTRICAL CHARACTERISTICS  $T_A = 0$ °C to 70°C,  $V_{CC} = 5V \pm 5\%$ ,  $V_{GG} = -12V + 5\%$ ,

Input rise and fall times = 10ns, Output load = 1TTL gate.

| PARAMETER         |                                                | TO FROM            | EPOM .             | TEST CONDITIONS         | LIMITS     |     |           |      |

|-------------------|------------------------------------------------|--------------------|--------------------|-------------------------|------------|-----|-----------|------|

|                   |                                                |                    | FROM               | TEST CONDITIONS         | Min        | Тур | Max       | UNIT |

| Freq.             | Clock rep rate                                 |                    |                    | See timing diagram note | dc         | 2.5 | 1.5       | MHz  |

| tøpw<br>tøpw      | Pulse width Clock Clock                        |                    | ,                  |                         | 0.2<br>0.2 | 0.1 | 100<br>dc | μS   |

| t <sub>R,tF</sub> | Clock pulse transition                         |                    |                    |                         |            |     | 1         | μS   |

| tos<br>toн        | Setup and hold time<br>Setup time<br>Hold time | φin<br>Data in     | Data in<br>øin     |                         | 50<br>70   |     |           | ns   |

| trs<br>trh        | Setup time<br>Hold time                        | φin<br>Recirculate | Recirculate<br>øin |                         | 50         |     |           |      |

| tA                | Delay time                                     | Data out           | Clock              | I <sub>OL</sub> = 1.6mA | 1          | 330 | 450       | ns   |

### NOTES

- 1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

- 2. For operating at elevated temperatures the device must be derated based on a +150°C maximum junction temperature and a thermal resistance of 150° C/W junction to ambient.

- 3. Guaranteed input levels are stated for worst case conditions including a  $\pm 5\%$  variation in V<sub>CC</sub> and a temperature variation of  $0^{\circ}$  C to  $+70^{\circ}$  C. Actual input requirements with respect to  $V_{CC}$  are  $V_{IH} = V_{CC}$ 1.85V and VIL = VCC - 4.15V.

- 4. All inputs are protected against static charge.

- 5. Parameters are valid over operating temperature range unless specified.

- 6. All voltage measurements are referenced to ground.

- 7. Manufacturer reserves the right to make design and process changes and improvements.

- 8. Typical values are at +25°C and typical supply voltages.

| BULL ALA BUT ATATIA BUILDE | NEATATER JATAVAL        |

|----------------------------|-------------------------|

| THIAL 74H-KIL STATIL SHIFT | =:43(~L~==:4==:1:1: =4= |

| DUAL LAV DIL SIATIV SITIL  | HEUIVIEN (LTVAL)        |

|                            | BEALATER INFAURS        |

|                            |                         |

| DUAL 250-BIT STATIC SHIFT  | REGISTER (ZJUAZ)        |

|                            |                         |

| MILE 256 RIT STATIC SHIFT  | DEPICIED PILEVIL        |

|                            | REUID ER IZJUAZI        |

2527 2528

2527-N • 2528-N • 2529-N

# **TIMING DIAGRAM**