## 54/7489 54LS/74LS89

### 64-BIT RANDOM ACCESS MEMORY

(With Open-Collector Outputs)

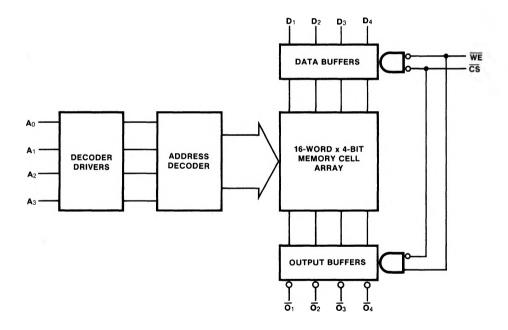

**DESCRIPTION** — The '89 a high speed, low power 64-bit Random Access Memory organized as a 16-word by 4-bit array. Address inputs are buffered to minimize loading, and addresses are fully decoded on-chip. Outputs are open-collector type and are in the off (HIGH) state when both the Chip Select (CS) and Write Enable (WE) are HIGH. For all other combinations of CS and WE the outputs are active, presenting the complement of either the stored data (READ mode) or the information present on the D inputs.

- OPEN-COLLECTOR OUTPUTS FOR WIRED-AND APPLICATIONS

- BUFFERED INPUTS MINIMIZE LOADING

- ADDRESS DECODING ON-CHIP

- DIODE CLAMPED INPUTS MINIMIZE RINGING

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                             | PKG<br>TYPE |  |

|--------------------|-----|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------|--|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{C to} +125^{\circ}\text{C}$ |             |  |

| Plastic<br>DIP (P) | Α   | 7489PC, 74LS89PC                                                                         |                                                                                            | 9B          |  |

| Ceramic<br>DIP (D) | Α   | 7489DC, 74LS89DC                                                                         | 5489DM, 54LS89DM                                                                           | 7B          |  |

| Flatpak<br>(F)     | Α   | 7489FC, 74LS89FC                                                                         | 5489FM, 54LS89FM                                                                           | 4L          |  |

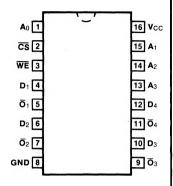

# CONNECTION DIAGRAM PINOUT A

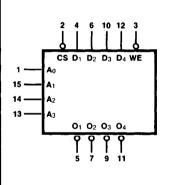

#### LOGIC SYMBOL

V<sub>CC</sub> = Pin 16 GND = Pin 8

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                   | DESCRIPTION                     | <b>54/74 (U.L.)</b><br>HIGH/LOW | 54/74LS (U.L.)<br>HIGH/LOW |  |

|---------------------------------------------|---------------------------------|---------------------------------|----------------------------|--|

| A <sub>0</sub> — A <sub>3</sub>             | Address Inputs                  | 1.0/1.0                         | 0.5/0.013                  |  |

| A <sub>0</sub> — A <sub>3</sub><br>CS<br>WE | Chip Select Input (Active LOW)  | 1.0/1.0                         | 0.5/0.013                  |  |

| WE                                          | Write Enable Input (Active LOW) | 1.0/1.0                         | 0.5/0.013                  |  |

| D1 — D4<br>Ō1 — Ō4                          | Data Inputs                     | 1.0/1.0                         | 0.5/0.013                  |  |

| $\overline{O}_1 - \overline{O}_4$           | Inverted Data Outputs           | OC*/7.5                         | OC*/10                     |  |

|                                             | · ·                             |                                 | (5.0)                      |  |

\*OC - Open Collector

#### **FUNCTION TABLE**

| INPUTS |     | OPERATION             | CONDITION OF OUTPUTS                                     |  |  |  |

|--------|-----|-----------------------|----------------------------------------------------------|--|--|--|

| cs     | WE  | 0, 2,                 |                                                          |  |  |  |

| L      | J I | Write<br>Read         | Complement of Data Inputs<br>Complement of Selected Word |  |  |  |

| H      | Η   | Inhibit Entry<br>Hold | Undetermined<br>(Off) HIGH                               |  |  |  |

H = HIGH Voltage Level L = LOW Voltage Level

#### LOGIC DIAGRAM

#### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER                    | 54/74       | 54/74LS    | UNITS | CONDITIONS                                         |

|--------|------------------------------|-------------|------------|-------|----------------------------------------------------|

|        | T ANAMETER                   | Min Max     | Min Max    |       |                                                    |

| Іон    | Output HIGH Current          | 20          | 20         | μΑ    | V <sub>CC</sub> = Min, V <sub>OH</sub> = 5.5 V     |

| VoL    | Output LOW Voltage XM, XC XC | 0.4<br>0.45 |            | ٧     | I <sub>OL</sub> = 12 mA<br>I <sub>OL</sub> = 16 mA |

|        |                              |             | 0.4<br>0.5 | ٧     | IOL = 8.0 mA<br>IOL = 16 mA                        |

| Icc    | Power Supply Current         | 105         | 40         | mA    | V <sub>CC</sub> = Min, $\overline{CS}$ = Gnd       |

| Co     | Off-State Output Capacitano  | e 4.0*      | 4.0*       | pF    | V <sub>O</sub> = 2.4 V, f = 1 MHz                  |

## AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

|              |                                                    | 54/74    | 54/74LS                            | UNITS | CONDITIONS                                  |

|--------------|----------------------------------------------------|----------|------------------------------------|-------|---------------------------------------------|

| SYMBOL       | PARAMETER                                          |          | $C_L = 15 pF$<br>$R_L = 2 k\Omega$ |       |                                             |

|              |                                                    | Min Max  | Min Max                            |       |                                             |

| tPLH<br>tPHL | Propagation Delay<br>CS to On                      | 50<br>50 | 10*<br>10*                         | ns    | Figs. 3-2, 3-5<br>'89 has 600 Ω to Gnd      |

| tPLH<br>tPHL | Propagation Delay A <sub>n</sub> to O <sub>n</sub> | 60<br>60 | 37*<br>37*                         | ns    | Figs. 3-2, 3-20<br>'89 has 600 Ω to Gnd     |

| trec         | Recovery Time<br>WE to On                          | 70       | 30°                                | ns    | Figs. 3-2, 3-4, 3-5<br>'89 has 600 Ω to Gnd |

## AC OPERATING REQUIREMENTS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$

| SYMBOL                                   | PARAMETER                                                       | 54/74      | 54/74LS    | UNITS   | CONDITIONS       |

|------------------------------------------|-----------------------------------------------------------------|------------|------------|---------|------------------|

|                                          | TANAME IEN                                                      | Min Max    | Min Max    | 0.11.10 |                  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>D <sub>n</sub> to WE                  | 40<br>40   | 25*<br>25* | ns      | Fig. 3-13        |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>An to WE                              | 0          | 10*<br>10* | ns      | Fig. 3-21        |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>D <sub>n</sub> or A <sub>n</sub> to WE | 5.0<br>5.0 | 0.<br>0.   | ns      | Figs. 3-13, 3-21 |

| t <sub>w</sub> (L)                       | WE Pulse Width LOW                                              | 40         | 25*        | ns      | Fig. 3-21        |

<sup>\*</sup>Typical Value