# 54ABT16646

54ABT16646 16-Bit Transceivers and Registers with TRI-STATE Outputs

Literature Number: SNOS053A

# 54ABT16646

# 16-Bit Transceivers and Registers with TRI-STATE® Outputs

# **General Description**

The 'ABT16646 consists of bus transceiver circuits with TRI-STATE, D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal registers. Data on the A or B bus will be clocked into the registers as the appropriate clock pin goes to a high logic level. Control  $\overline{\text{OE}}$  and direction pins are provided to control the transceiver function. In the transceiver mode, data present at the high impedance port may be stored in either the A or the B register or in both. The select controls can multiplex stored and real-time (transparent mode) data. The direction control determines which bus will receive data when the enable control  $\overline{\text{OE}}$  is Active LOW. In the isolation mode (control  $\overline{\text{OE}}$  HIGH), A data may be stored in the B register and/or B data may be stored in the A register.

# **Features**

- Independent registers for A and B buses

- Multiplexed real-time and stored data

- A and B output sink capability of 48 mA, source capability of 24 mA

- Guaranteed latchup protection

- High impedance glitch free bus loading during entire power up and power down cycle

- Nondestructive hot insertion capability

- Standard Microcircuit Drawing (SMD) 5962-9450202

# **Ordering Code**

| Military        | Package<br>Number | Package Description |

|-----------------|-------------------|---------------------|

| 54ABT16646W-QML | WA56A             | 56-Lead Cerpack     |

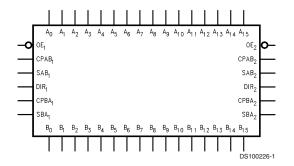

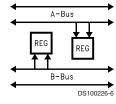

# **Logic Symbol**

| Pin Names                             | Description             |

|---------------------------------------|-------------------------|

| A <sub>0</sub> -A <sub>15</sub>       | Data Register A Inputs/ |

|                                       | TRI-STATE Outputs       |

| B <sub>0</sub> -B <sub>15</sub>       | Data Register B Inputs/ |

|                                       | TRI-STATE Outputs       |

| CPAB <sub>n</sub> , CPBA <sub>n</sub> | Clock Pulse Inputs      |

| SAB <sub>n</sub> , SBA <sub>n</sub>   | Select Inputs           |

| ŌĒ <sub>n</sub>                       | Output Enable Input     |

| DIR                                   | Direction Control Input |

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

# **Connection Diagram**

# Pin Assignment for Cerpack

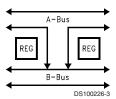

Real Time Transfer A-Bus to B-Bus

FIGURE 1.

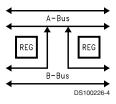

Real Time Transfer B-Bus to A-Bus

FIGURE 2.

Storage from Bus to Register

FIGURE 3.

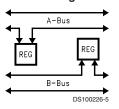

# Transfer from Register to Bus

FIGURE 4.

# **Function Table**

|                 |                  | Inj               | outs              |                  |                  | Data I/O (Note 1) |                  | Output Operation Mode                          |

|-----------------|------------------|-------------------|-------------------|------------------|------------------|-------------------|------------------|------------------------------------------------|

| ŌE <sub>1</sub> | DIR <sub>1</sub> | CPAB <sub>1</sub> | CPBA <sub>1</sub> | SAB <sub>1</sub> | SBA <sub>1</sub> | A <sub>0-7</sub>  | B <sub>0-7</sub> |                                                |

| Н               | Χ                | H or L            | H or L            | Χ                | Х                |                   |                  | Isolation                                      |

| Н               | Χ                | N                 | Χ                 | Χ                | Χ                | Input             | Input            | Clock An Data into A Register                  |

| Н               | Χ                | Χ                 | N                 | Χ                | Χ                |                   |                  | Clock Bn Data Into B Register                  |

| L               | Н                | Х                 | Х                 | L                | Х                |                   |                  | An to Bn—Real Time (Transparent Mode)          |

| L               | Н                | N                 | Χ                 | L                | Χ                | Input             | Output           | Clock An Data to A Register                    |

| L               | Н                | H or L            | Χ                 | Н                | Χ                |                   |                  | A Register to Bn (Stored Mode)                 |

| L               | Н                | N                 | Χ                 | Н                | Χ                |                   |                  | Clock An Data into A Register and Output to Bn |

| L               | L                | Х                 | Х                 | Х                | L                |                   |                  | Bn to An—Real Time (Transparent Mode)          |

| L               | L                | Χ                 | N                 | Χ                | L                | Output            | Input            | Clock Bn Data into B Register                  |

| L               | L                | Χ                 | H or L            | Χ                | Н                |                   |                  | B Register to An (Stored Mode)                 |

| L               | L                | Χ                 | N                 | Χ                | Н                |                   |                  | Clock Bn into B Register and Output to An      |

H = HIGH Voltage Level

X = Immaterial

L = LOW Voltage Level

N = LOW-to-HIGH Transition.

Note 1: The data output functions may be enabled or disabled by various signals at the  $\overline{\text{OE}}$  and DIR inputs. Data input functions are always enabled; i.e., data at the bus pins will be stored on every LOW-to-HIGH transition of the appropriate clock inputs. Also applies to data I/O (A and B: 8-15) and #2 control pins.

# Logic Diagram TO 7 OTHER CHANNELS TO 7 OTHER CHANNELS DIR<sub>1</sub> — CPBA<sub>1</sub> — CPAB<sub>1</sub> — SBA<sub>1</sub> SAB1.

10V

# **Absolute Maximum Ratings** (Note 2)

Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ Ambient Temperature under Bias  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

Junction Temperature under Bias

Ceramic -55°C to +175°C

$V_{\text{CC}}$  Pin Potential to

Voltage Applied to Any Output

in the Disable or

Power-Off State -0.5 V to +5.5 V in the HIGH State  $-0.5 \text{V to } \text{V}_{\text{CC}}$

Current Applied to Output

in LOW State (Max) twice the rated  $I_{OL}$  (mA) DC Latchup Source Current -500 mA

Over Voltage Latchup (I/O)

# Recommended Operating Conditions

Free Air Ambient Temperature

Military  $-55^{\circ}$ C to  $+125^{\circ}$ C

Supply Voltage

Military +4.5V to +5.5V Minimum Input Edge Rate  $(\Delta V/\Delta t)$  Data Input 50 mV/ns Enable Input 20 mV/ns Clock Input 100 mV/ns

**Note 2:** Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 3: Either voltage limit or current limit is sufficient to protect inputs.

# **DC Electrical Characteristics**

| Symbol                             | Parameter                         | Parameter ABT16646 Units |     | Units | V <sub>cc</sub> | Conditions |                                                   |

|------------------------------------|-----------------------------------|--------------------------|-----|-------|-----------------|------------|---------------------------------------------------|

|                                    |                                   | Min                      | Тур | Max   | 1               |            |                                                   |

| V <sub>IH</sub>                    | Input HIGH Voltage                | 2.0                      |     |       | V               |            | Recognized HIGH Signal                            |

| V <sub>IL</sub>                    | Input LOW Voltage                 |                          |     | 0.8   | V               |            | Recognized LOW Signal                             |

| V <sub>CD</sub>                    | Input Clamp Diode Voltage         |                          |     | -1.2  | V               | Min        | I <sub>IN</sub> = -18 mA (Non I/O Pins)           |

| V <sub>OH</sub>                    | Output HIGH Voltage 54ABT         | 2.5                      |     |       |                 |            | $I_{OH} = -3 \text{ mA}, (A_n, B_n)$              |

|                                    | 54ABT                             | 2.0                      |     |       |                 |            | $I_{OH} = -24 \text{ mA}, (A_n, B_n)$             |

| $V_{OL}$                           | Output LOW Voltage 54ABT          |                          |     | 0.55  | V               | Min        | $I_{OL} = 48 \text{ mA}, (A_n, B_n)$              |

| $V_{ID}$                           | Input Leakage Test                | 4.75                     |     |       | V               | 0.0        | I <sub>ID</sub> = 1.9 μA, (Non-I/O Pins)          |

|                                    |                                   |                          |     |       |                 |            | All Other Pins Grounded                           |

| I <sub>IH</sub>                    | Input HIGH Current                |                          |     | 5     | μA              | Max        | V <sub>IN</sub> = 2.7V (Non-I/O Pins) (Note 5)    |

|                                    |                                   |                          |     |       |                 |            | V <sub>IN</sub> = V <sub>CC</sub> (Non-I/O Pins)  |

| I <sub>BVI</sub>                   | Input HIGH Current                |                          |     | 7     | μA              | Max        | V <sub>IN</sub> = 7.0V (Non-I/O Pins)             |

|                                    | Breakdown Test                    |                          |     |       |                 |            |                                                   |

| I <sub>BVIT</sub>                  | Input HIGH Current                |                          |     | 100   | μA              | Max        | $V_{IN} = 5.5V (A_n, B_n)$                        |

|                                    | Breakdown Test (I/O)              |                          |     |       |                 |            |                                                   |

| I <sub>IL</sub>                    | Input LOW Current                 |                          |     | -5    | μA              | Max        | V <sub>IN</sub> = 0.5V (Non-I/O Pins) (Note 5)    |

|                                    |                                   |                          |     |       |                 |            | V <sub>IN</sub> = 0.0V (Non-I/O Pins)             |

| I <sub>IH</sub> + I <sub>OZH</sub> | Output Leakage Current            |                          |     | 50    | μA              | 0V-5.5V    | $V_{OUT} = 2.7V (A_n, B_n); \overline{OE} = 2.0V$ |

| $I_{IL} + I_{OZL}$                 | Output Leakage Current            |                          |     | -50   | μA              | 0V-5.5V    | $V_{OUT} = 0.5V (A_n, B_n); \overline{OE} = 2.0V$ |

| Ios                                | Output Short-Circuit Current      | -100                     |     | -275  | mA              | Max        | $V_{OUT} = 0V (A_n, B_n)$                         |

| I <sub>CEX</sub>                   | Output HIGH Leakage Current       |                          |     | 50    | μΑ              | Max        | $V_{OUT} = V_{CC} (A_n, B_n)$                     |

| $I_{ZZ}$                           | Bus Drainage Test                 |                          |     | 100   | μΑ              | 0.0V       | $V_{OUT} = 5.5V (A_n, B_n);$                      |

|                                    |                                   |                          |     |       |                 |            | All Others GND                                    |

| I <sub>CCH</sub>                   | Power Supply Current              |                          |     | 2.0   | mA              | Max        | All Outputs HIGH                                  |

| I <sub>CCL</sub>                   | Power Supply Current              |                          |     | 60    | mA              | Max        | All Outputs LOW                                   |

| I <sub>CCZ</sub>                   | Power Supply Current              |                          |     | 2.0   | mA              | Max        | Outputs TRI-STATE; All Others GND                 |

| I <sub>CCT</sub>                   | Additional I <sub>CC</sub> /Input |                          |     | 2.5   | mA              | Max        | $V_I = V_{CC} - 2.1V$                             |

|                                    |                                   |                          |     |       |                 |            | All Other Outputs at V <sub>CC</sub> or GND       |

| I <sub>CCD</sub>                   | Dynamic I <sub>CC</sub> No Load   |                          |     |       |                 |            | Outputs Open                                      |

|                                    | (Note 5)                          |                          |     | 0.23  | mA/MHz          | Max        | OE, DIR, and SEL = GND,                           |

|                                    |                                   |                          |     |       |                 |            | Non-I/O = GND or V <sub>CC</sub> (Note 4)         |

|                                    |                                   |                          |     |       |                 |            | One Bit toggling, 50% duty cycle                  |

|                                    |                                   |                          |     |       | 1               | 1          |                                                   |

# **DC Electrical Characteristics** (Continued)

Note 4: For 8-bit toggling,  $I_{CCD}$  < 1.4 mA/MHz.

Note 5: Guaranteed but not tested.

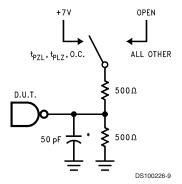

| Sym-<br>bol      | Parameter                                    | Min | Max  | Units | V <sub>cc</sub> | Conditions                             |

|------------------|----------------------------------------------|-----|------|-------|-----------------|----------------------------------------|

|                  |                                              |     |      |       |                 | $C_L = 50 \text{ pF}, R_L = 500\Omega$ |

| V <sub>OLP</sub> | Quiet Output Maximum Dynamic V <sub>OL</sub> |     | 1.0  | V     | 5.0             | T <sub>A</sub> = 25°C (Note 6)         |

| V <sub>OLV</sub> | Quiet Output Minimum Dynamic V <sub>OL</sub> |     | -1.5 | V     | 5.0             | T <sub>A</sub> = 25°C (Note 6)         |

Note 6: Max number of outputs defined as (n). n-1 data inputs are driven 0V to 3V. One output at LOW. Guaranteed, but not tested.

# **AC Electrical Characteristics**

|                  |                                                                          | 54 <b>A</b>            | Units |     |

|------------------|--------------------------------------------------------------------------|------------------------|-------|-----|

|                  |                                                                          | T <sub>A</sub> = -55°C |       |     |

| Symbol           | Parameter                                                                | $V_{CC} = 4.5V - 5.5V$ |       |     |

|                  |                                                                          | C <sub>L</sub> =       | 50 pF |     |

|                  |                                                                          | Min                    | Max   |     |

| f <sub>max</sub> | Max Clock Frequency                                                      | 125                    |       | MHz |

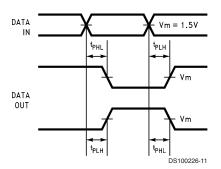

| t <sub>PLH</sub> | Propagation Delay                                                        | 1.0                    | 6.9   | ns  |

| t <sub>PHL</sub> | Clock to Bus                                                             | 1.0                    | 7.7   |     |

| t <sub>PLH</sub> | Propagation Delay                                                        | 1.0                    | 5.8   | ns  |

| t <sub>PHL</sub> | Bus to Bus                                                               | 1.0                    | 7.0   |     |

| t <sub>PLH</sub> | Propagation Delay                                                        | 1.0                    | 7.1   | ns  |

| t <sub>PHL</sub> | SBA <sub>n</sub> or SAB <sub>n</sub> to A <sub>n</sub> to B <sub>n</sub> | 1.0                    | 7.2   |     |

| t <sub>PZH</sub> | Enable Time                                                              | 1.0                    | 6.4   | ns  |

| $t_{PZL}$        | $\overline{OE}_n$ to $A_n$ or $B_n$                                      | 1.0                    | 6.5   |     |

| t <sub>PHZ</sub> | Disable Time                                                             | 1.0                    | 7.6   | ns  |

| $t_{PLZ}$        | $\overline{OE}_n$ to $A_n$ or $B_n$                                      | 1.0                    | 6.5   |     |

| t <sub>PZH</sub> | Enable Time                                                              | 1.0                    | 6.4   | ns  |

| $t_{PZL}$        | DIR <sub>n</sub> to A <sub>n</sub> or B <sub>n</sub>                     | 1.0                    | 6.7   |     |

| t <sub>PHZ</sub> | Disable Time                                                             | 1.0                    | 8.1   | ns  |

| $t_{PLZ}$        | DIR <sub>n</sub> to A <sub>n</sub> or B <sub>n</sub>                     | 1.0                    | 7.1   |     |

# **AC Operating Requirements**

| Symbol             | Parameter           | $T_{A} = -55^{\circ}($ $V_{CC} = 4$ $C_{L} =$ | Units |    |

|--------------------|---------------------|-----------------------------------------------|-------|----|

|                    |                     | Min                                           | Max   |    |

| t <sub>S</sub> (H) | Setup Time, HIGH    | 4.0                                           |       | ns |

| t <sub>S</sub> (L) | or LOW Bus to Clock |                                               |       |    |

| t <sub>H</sub> (H) | Hold Time, HIGH     | 0.5                                           |       | ns |

| $t_H(L)$           | or LOW Bus to Clock |                                               |       |    |

| t <sub>W</sub> (H) | Pulse Width,        | 4.3                                           |       | ns |

| $t_W(L)$           | HIGH or LOW         |                                               |       |    |

# Capacitance

| Symbol                    | Symbol Parameter   |    | Units | Conditions                          |

|---------------------------|--------------------|----|-------|-------------------------------------|

|                           |                    |    |       | T <sub>A</sub> = 25°C               |

| C <sub>IN</sub>           | Input Capacitance  | 5  | pF    | V <sub>CC</sub> = 0V (non I/O pins) |

| C <sub>I/O</sub> (Note 7) | Output Capacitance | 11 | pF    | $V_{CC} = 5.0V (A_n, B_n)$          |

# Capacitance (Continued)

Note 7:  $C_{I/O}$  is measured at frequency, f = 1 MHz, per MIL-STD-883B, Method 3012.

# **AC Loading**

<sup>\*</sup>Includes jig and probe capacitance

FIGURE 5. Standard AC Test Load

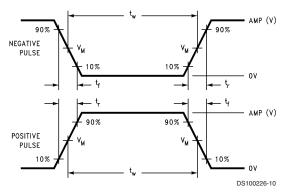

FIGURE 6.  $V_M = 1.5V$ Input Pulse Requirements

| Ampli-<br>tude | Rep.<br>Rate | t <sub>w</sub> | t <sub>r</sub> | t <sub>f</sub> |

|----------------|--------------|----------------|----------------|----------------|

| 3V             | 1 MHz        | 500 ns         | 2.5 ns         | 2.5 ns         |

FIGURE 7. Test Input Signal Requirements

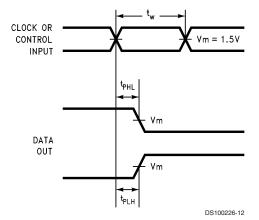

FIGURE 8. Propagation Delay Waveforms for Inverting and Non-Inverting Functions

FIGURE 9. Propagation Delay, Pulse Width Waveforms

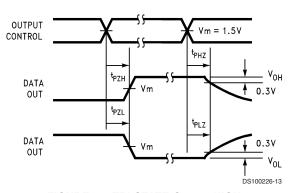

FIGURE 10. TRI-STATE Output HIGH and LOW Enable and Disable Times

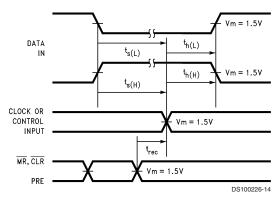

FIGURE 11. Setup Time, Hold Time and Recovery Time Waveforms

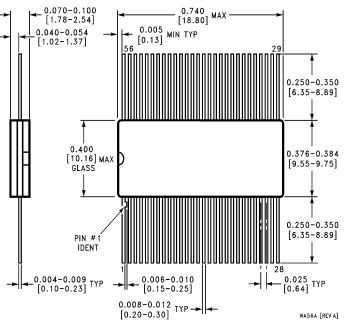

# Physical Dimensions inches (millimeters) unless otherwise noted

56-Lead Cerpack NS Package Number WA56A

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products | Applications |

|----------|--------------|

|----------|--------------|

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic logic.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors <u>www.ti.com/omap</u>

Wireless Connectivity www.ti.com/wirelessconnectivity

TI E2E Community Home Page e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated