## 54LS/74LS563

### OCTAL D-TYPE LATCH

(With 3-State Outputs)

**DESCRIPTION** — The '563 is a high speed octal latch with buffered common Latch Enable (LE) and buffered common Output Enable (OE) inputs.

This device is functionally indentical to the 'LS573, but has inverted outputs. For truth tables, discussion of operations and ac and dc specifications, please refer to the 'LS373 data sheet, but note that the data to output delays are 5.0 ns longer for the 'LS563 than for the 'LS373.

- INPUTS AND OUTPUTS ON OPPOSITE SIDES OF PACKAGE ALLOWING EASY INTERFACE WITH MICROPROCESSORS

- USEFUL AS INPUT OR OUTPUT PORT FOR MICROPROCESSORS

- FUNCTIONALLY IDENTICAL TO 'LS573

- INPUT CLAMP DIODES LIMIT HIGH SPEED TERMINATION EFFECTS

- FULLY TTL AND CMOS COMPATIBLE

**ORDERING CODE:** See Section 9

| PKGS               | PIN<br>OUT | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                              | PKG  |  |

|--------------------|------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|--|

|                    |            | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{C to} + 125^{\circ}\text{C}$ | TVDE |  |

| Plastic<br>DIP (P) | A          | 74LS563PC                                                                                |                                                                                             | 9Z   |  |

| Ceramic<br>DIP (D) | A          | 74LS563DC                                                                                | 54LS563DM                                                                                   | 4E   |  |

| Flatpak<br>(F)     | A          | 74LS563FC                                                                                | 54LS563FM                                                                                   | 4F   |  |

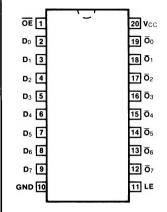

# CONNECTION DIAGRAM PINOUT A

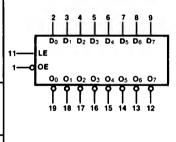

### LOGIC SYMBOL

V<sub>CC</sub> = Pin 20 GND = Pin 10

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                   | DESCRIPTION                              | <b>54/74LS (U.L.)</b><br>HIGH/LOW |

|---------------------------------------------|------------------------------------------|-----------------------------------|

| D <sub>0</sub> — D <sub>7</sub>             | Data Inputs                              | 0.5/0.25                          |

| LE<br>OE<br>O <sub>0</sub> — O <sub>7</sub> | Latch Enable Input (Active HIGH)         | 0.5/0.25                          |

| ŌĒ                                          | 3-State Output Enable Input (Active LOW) | 0.5/0.25                          |

| Ō₀ — Ō <sub>7</sub>                         | 3-State Latch Outputs                    | 65/15                             |

|                                             |                                          | (25)/(7.5)                        |