# **54/74177**PRESETTABLE BINARY COUNTER

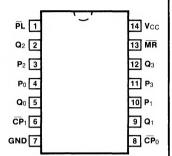

# CONNECTION DIAGRAM PINOUT A

**DESCRIPTION** — The 1777 is a presettable modulo-16 ripple counter partitioned into divide-by-two and divide-by-eight sections, with a separate clock input for each section. In the counting mode, state changes are initiated by the falling edge of the clock. A LOW signal on the Master Reset ( $\overline{\text{MR}}$ ) input overrides all other inputs and forces the outputs LOW. A LOW signal on the Parallel Load ( $\overline{\text{PD}}$ ) input overrides the clocks and causes the Q outputs to assume the state of their respective Parallel Data ( $\overline{\text{Pn}}$ ) inputs. For detail specifications, please refer to the '176 data sheet.

## **ORDERING CODE:** See Section 9

| PKGS               | PIN<br>OUT | COMMERCIAL GRADE                                                                        | MILITARY GRADE                                                                                          | PKG  |  |  |

|--------------------|------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|--|--|

|                    |            | $V_{CC} = +5.0 \text{ V} \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to} + 70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C} \text{ to } +125^{\circ} \text{ C}$ | TYPE |  |  |

| Plastic<br>DIP (P) | Α          | 74177PC                                                                                 |                                                                                                         | 9A   |  |  |

| Ceramic<br>DIP (D) | Α          | 74177DC                                                                                 | 54177DM                                                                                                 | 6A   |  |  |

| Flatpak<br>(F)     | Α          | 74177FC                                                                                 | 54177FM                                                                                                 | 31   |  |  |

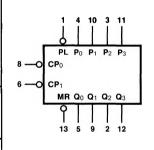

# LOGIC SYMBOL

V<sub>CC</sub> = Pin 14 GND = Pin 7

# INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                | DESCRIPTION                                   | <b>54/74 (U.L.)</b><br>HIGH/LOW |  |

|------------------------------------------|-----------------------------------------------|---------------------------------|--|

| EP <sub>0</sub><br>EP <sub>1</sub><br>MR | ÷2 Section Clock Input (Active Falling Edge)  | 2.0/3.0                         |  |

| P <sub>1</sub>                           | ÷8 Section Clock Input (Active Falling Edge)  | 2.0/2.0                         |  |

| ЛR                                       | Asynchronous Master Reset Input (Active LOW)  | 2.0/2.0                         |  |

| P <sub>0</sub> — P <sub>3</sub>          | Parallel Data Inputs                          | 1.0/1.0                         |  |

| Σ.                                       | Asynchronous Parallel Load Input (Active LOW) | 1.0/1.0                         |  |

| $Q_0 - Q_3$                              | Flip-flop Outputs*                            | 20/10                           |  |

\*Qo is guaranteed to drive CP1 in addition to the full rated load.

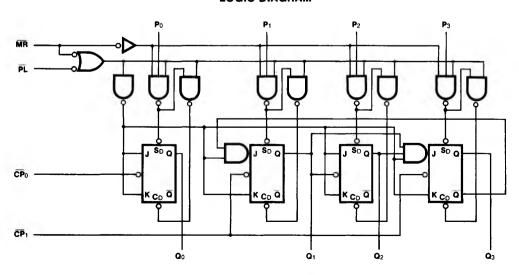

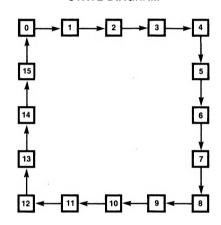

**FUNCTIONAL DESCRIPTION**—The '177 is an asynchronously presettable binary ripple counter partitioned into divide-by-two and divide-by-eight sections. In the counting modes, state changes are initiated by the HIGH-to-LOW transition of the clock signals. State changes of the Q outputs, however, do not occur simultaneously because of the internal ripple delays. When using external logic to decode the  $Q_n$  outputs, designers should bear in mind that the unequal delays can lead to decoding spikes and thus a decoded signal should not be used as a clock or strobe. The  $\overline{CP_0}$  input serves the  $Q_0$  flip-flop while the  $\overline{CP_1}$  input  $\overline{CP_1}$  input. With the input frequency connected to  $\overline{CP_0}$  and with  $Q_0$  driving  $\overline{CP_1}$ , the '177 forms a straightforward modulo-16 counter, with  $Q_0$  the least significant output and  $Q_3$  the most significant output.

The '177 has an asynchronous active LOW Master Reset input  $(\overline{MR})$  which overrides all other inputs and forces all outputs LOW. The counters are also asynchronously presettable. A LOW on the Parallel Load input  $(\overline{PL})$  overrides the clock inputs and loads the data from Parallel Data  $(P_0 - P_3)$  inputs into the flip-flops. While  $\overline{PL}$  is LOW, the counters act as transparent latches and any change in the  $P_0$  inputs will be reflected in the outputs.

### **MODE SELECT TABLE**

|    | INPL | JTS | RESPONSE                        |

|----|------|-----|---------------------------------|

| MR | PL   | CP  | 1.25. 5.152                     |

| L  | х    | Х   | Qn forced LOW                   |

| H  | L    | Х   | P <sub>n</sub> → Q <sub>n</sub> |

| Н  | н    | _ر_ | Count Up                        |

H = HIGH Voltage Level L = LOW Voltage Level

X = Immaterial

#### STATE DIAGRAM

# LOGIC DIAGRAM