## 54/7495A 54LS/74LS95B

4-BIT RIGHT/LEFT SHIFT REGISTER

**DESCRIPTION** — The '95 is a 4-bit shift register with serial and parallel synchronous operating modes. The serial shift right and parallel load are activated by separate clock inputs which are selected by a mode control input. The data is transferred from the serial or parallel D inputs to the Q outputs synchronous with the HIGH-to-LOW transition of the appropriate clock input.

- SYNCHRONOUS, EXPANDABLE SHIFT RIGHT

- SYNCHRONOUS SHIFT LEFT CAPABILITY

- SYNCHRONOUS PARALLEL LOAD

- SEPARATE SHIFT AND LOAD CLOCK INPUTS

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                               | PKG        |

|--------------------|-----|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------|

| PKGS               | ОПТ | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{ C to} +125^{\circ}\text{ C}$ | TYPE       |

| Plastic<br>DIP (P) | Α   | 7495APC, 74LS95BPC                                                                       |                                                                                              | 9A         |

| Ceramic<br>DIP (D) | Α   | 7495ADC, 74LS95BDC                                                                       | 5495ADM, 54LS95BDM                                                                           | 6 <b>A</b> |

| Flatpak<br>(F)     | Α   | 7495AFC, 74LS95BFC                                                                       | 5495AFM, 54LS95BFM                                                                           | 31         |

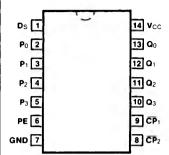

# CONNECTION DIAGRAM PINOUT A

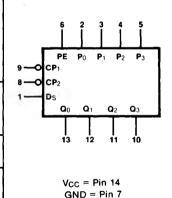

#### LOGIC SYMBOL

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                          | DESCRIPTION                                | <b>54/74 (U.L.)</b><br>HIGH/LOW | <b>54/74LS (U.L.)</b><br>HIGH/LOW |

|------------------------------------|--------------------------------------------|---------------------------------|-----------------------------------|

| CP <sub>1</sub><br>CP <sub>2</sub> | Serial Clock Input (Active Falling Edge)   | 1.0/1.0                         | 0.5/0.25                          |

| CP <sub>2</sub>                    | Parallel Clock Input (Active Falling Edge) | 1.0/1.0                         | 0.5/0.25                          |

| Ds                                 | Serial Data Input                          | 1.0/1.0                         | 0.5/0.25                          |

| P <sub>0</sub> — P <sub>3</sub>    | Parallel Data Inputs                       | 1.0/1.0                         | 0.5/0.25                          |

| PE                                 | Parallel Enable Input (Active HIGH)        | 2.0/2.0                         | 1.0/0.5                           |

| $Q_0 - Q_3$                        | Parallel Outputs                           | 20/10                           | 10/5.0                            |

|                                    |                                            |                                 | (2.5)                             |

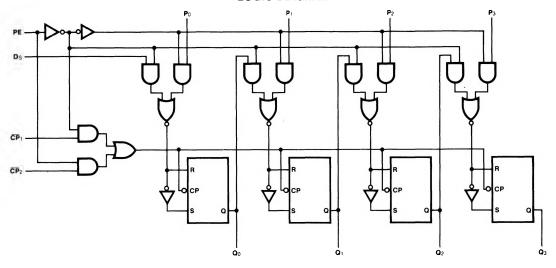

**FUNCTIONAL DESCRIPTION** — The '95 is a 4-bit shift register with serial and parallel synchronous operating modes. It has a Serial (D<sub>S</sub>) and four Parallel (P<sub>0</sub> — P<sub>3</sub>) Data inputs and four Parallel Data outputs (Q<sub>0</sub> — Q<sub>3</sub>). The serial or parallel mode of operation is controlled by a Parallel Enable input (PE) and two Clock inputs,  $\overline{CP}_1$  and  $\overline{CP}_2$ . The serial (right-shift) or parallel data transfers occur synchronous with the HIGH-to-LOW transition of the selected clock input.

When PE is HIGH,  $\overline{CP}_2$  is enabled. A HIGH-to-LOW transition on enabled  $\overline{CP}_2$  transfers parallel data from the  $P_0-P_3$  inputs to the  $Q_0-Q_3$  outputs. When PE is LOW,  $\overline{CP}_1$  is enabled. A HIGH-to-LOW transition on enabled  $\overline{CP}_1$  transfers the data from Serial input ( $D_S$ ) to  $Q_0$  and shifts the data in  $Q_0$  to  $Q_1$ ,  $Q_1$  to  $Q_2$ , and  $Q_2$  to  $Q_3$  respectively (right-shift). A left-shift is accomplished by externally connecting  $Q_3$  to  $P_2$ ,  $Q_2$  to  $P_1$ , and  $Q_1$  to  $P_0$ , and operating the '95 in the parallel mode (PE=HIGH). For normal operation, PE should only change states when both Clock inputs are LOW. However, changing PE from LOW to HIGH while  $\overline{CP}_2$  is HIGH, or changing PE from HIGH to LOW while  $\overline{CP}_1$  is HIGH and  $\overline{CP}_2$  is LOW will not cause any changes on the register outputs.

#### **MODE SELECT TABLE**

| OPERATING     | INPUTS    |        |                 |                            |                            | OUTPUTS                       |                                                                 |                                           |                          |

|---------------|-----------|--------|-----------------|----------------------------|----------------------------|-------------------------------|-----------------------------------------------------------------|-------------------------------------------|--------------------------|

| MODE          | PE        | CP₁    | CP <sub>2</sub> | Ds                         | Pn                         | Q <sub>0</sub>                | Q <sub>1</sub>                                                  | Q <sub>2</sub>                            | Q <sub>3</sub>           |

| Shift         | L         | l<br>l | X<br>X          | l<br>h                     | X<br>X                     | ЬH                            | <b>q</b> o<br><b>q</b> o                                        | <b>Q</b> 1<br><b>Q</b> 1                  | <b>q</b> 2<br><b>q</b> 2 |

| Parallel Load | Н         | X      | l               | Х                          | рn                         | <b>p</b> o                    | P1                                                              | p <sub>2</sub>                            | <b>p</b> 3               |

| Mode Change   | 7575 7575 |        | L L H H H H     | x<br>x<br>x<br>x<br>x<br>x | x<br>x<br>x<br>x<br>x<br>x | No<br>Und<br>Und<br>No<br>Und | Char<br>Char<br>Char<br>deter<br>deter<br>Char<br>deter<br>Char | nge<br>nge<br>mine<br>mine<br>nge<br>mine | d                        |

I = LOW Voltage Level one set-up time prior to the HIGH-to-LOW clock transition. h = HIGH Voltage Level one set-up time prior to the HIGH-to-LOW clock transition.  $p_n$  = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the HIGH-to-LOW clock transition.

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

#### **LOGIC DIAGRAM**

### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER            | 54/74 |     | 54/74LS |     | UNITS | CONDITIONS            |  |

|--------|----------------------|-------|-----|---------|-----|-------|-----------------------|--|

| 0,     | 7.4                  | Min   | Мах | Min     | Max | 00    |                       |  |

| lcc    | Power Supply Current |       | 63  |         | 21  | mA    | V <sub>CC</sub> = Max |  |

## AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

|              |                                                                           | 54/74                                            | 54/74LS                |       |                |  |

|--------------|---------------------------------------------------------------------------|--------------------------------------------------|------------------------|-------|----------------|--|

| SYMBOL       | PARAMETER                                                                 | C <sub>L</sub> = 15 pF<br>R <sub>L</sub> = 400 Ω | C <sub>L</sub> = 15 pF | UNITS | CONDITONS      |  |

|              |                                                                           | Min Max                                          | Min Max                |       |                |  |

| fmax         | Maximum Shift Frequency                                                   | 25                                               | 30                     | MHz   | Figs. 3-1, 3-9 |  |

| tPLH<br>tPHL | Propagation Delay<br>CP <sub>1</sub> or CP <sub>2</sub> to Q <sub>n</sub> | 27<br>32                                         | 27<br>27               | ns    | Figs. 3-1, 3-9 |  |

## AC OPERATING REQUIREMENTS: VCC = +5.0 V, TA = +25°C

| SYMBOL               | PARAMETER                                  | 54       | 54/74 |          | 74LS | UNITS  | CONDITIONS   |

|----------------------|--------------------------------------------|----------|-------|----------|------|--------|--------------|

|                      |                                            | Min      | Max   | Min      | Мах  | 0.11.0 | 001121110110 |

| ts (H)<br>ts (L)     | Setup Time HIGH or LOW<br>Ds or Pn to CPn  | 15<br>15 |       | 20<br>20 |      | ns     | Fig. 3-7     |

| th (H)               | Hold Time HIGH or LOW<br>Ds or Pn to CPn   | 0        |       | 10<br>10 |      | ns     | Fig. 3-7     |

| tw (H)               | CPn Pulse Width HIGH                       | 20       |       | 20       |      | ns     | Fig. 3-9     |

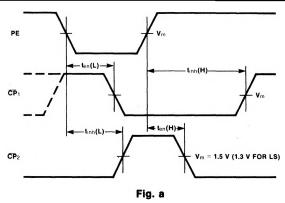

| t <sub>en</sub> (L)  | Enable Time LOW<br>PE to CP <sub>1</sub>   | 15       |       | 25       |      | ns     | Fig. a       |

| t <sub>inh</sub> (H) | Inhibit Time HIGH<br>PE to CP <sub>1</sub> | 5.0      |       | 20       |      | ns     | Fig. a       |

| t <sub>en</sub> (H)  | Enable Time HIGH<br>PE to CP <sub>2</sub>  | 15       |       | 25       |      | ns     | Fig. a       |

| t <sub>inh</sub> (L) | Inhibit Time LOW<br>PE to CP <sub>2</sub>  | 5.0      |       | 20       |      | ns     | Fig. a       |