# 54/74165 54LS/74LS165

### 8-BIT PARALLEL-TO-SERIAL CONVERTER

**DESCRIPTION** — The '165 is an 8-bit parallel load or serial-in register with complementary outputs available from the last stage. Parallel inputing occurs asynchronously when the Parallel Load ( $\overrightarrow{PL}$ ) input is LOW. With  $\overrightarrow{PL}$  HIGH, serial shifting occurs on the rising edge of the clock; new data enters via the Serial Data (Ds) input. The 2-input OR clock can be used to combine two independent clock sources, or one input can act as an active LOW clock enable.

#### **ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                             | MILITARY GRADE                                                                                 | PKG  |

|--------------------|-----|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ} \text{ C to } +70^{\circ} \text{ C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C to} +125^{\circ} \text{ C}$ | TYPE |

| Plastic<br>DIP (P) | A   | 74165PC, 74LS165PC                                                                           |                                                                                                | 9B   |

| Ceramic<br>DIP (D) | A   | 74165DC, 74LS165DC                                                                           | 54165DM, 54LS165DM                                                                             | 6B   |

| Flatpak<br>(F)     | А   | 74165FC, 74LS165FC                                                                           | 54165FM, 54LS165FM                                                                             | 4L   |

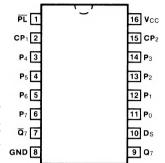

# CONNECTION DIAGRAM PINOUT A

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                         | DESCRIPTION                                   | <b>54/74 (U.L.)</b><br>HIGH/LOW | <b>54/74LS (U.L.)</b><br>HIGH/LOW |

|-----------------------------------|-----------------------------------------------|---------------------------------|-----------------------------------|

| CP <sub>1</sub> , CP <sub>2</sub> | Clock Pulse Inputs (Active Rising Edge)       | 1.0/1.0                         | 0.5/0.25                          |

| Ds                                | Serial Data Input                             | 1.0/1.0                         | 0.5/0.25                          |

| Ds<br>PL                          | Asynchronous Parallel Load Input (Active LOW) | 2.0/2.0                         | 1.5/0.75                          |

| $P_0 - P_7$                       | Parallel Data Inputs                          | 1.0/1.0                         | 0.5/0.25                          |

| Q <sub>7</sub>                    | Serial Output From Last Stage                 | 20/10                           | 10/5.0                            |

|                                   |                                               |                                 | (2.5)                             |

| Q <sub>7</sub>                    | Complementary Output                          | 20/10                           | 10/5.0<br>(2.5)                   |

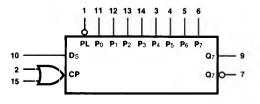

#### LOGIC SYMBOL

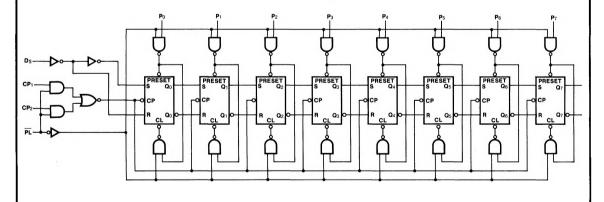

V<sub>CC</sub> = Pin 16 GND = Pin 8 **FUNCTIONAL DESCRIPTION** — The '165 contains eight clocked master/slave RS flip-flops connected as a shift register with auxiliary gating to provide overriding asynchronous parallel entry. Parallel data enters when the  $\overline{PL}$  signal is LOW. The parallel data can change while  $\overline{PL}$  is LOW provided that the recommended setup and hold times are observed.

For clocked operation,  $\overline{PL}$  must be HIGH. The two clock inputs perform identically; one can be used as a clock inhibit by applying a HIGH signal. To avoid double clocking, however, the inhibit signal should only go HIGH while the clock is HIGH. Otherwise, the rising inhibit signal will cause the same response as a rising clock edge. The flip-flops are edge-triggered for serial operations. The serial input data can change at any time, provided only that the recommended setup and hold times are observed, with respect to the rising edge of the clock.

**TRUTH TABLE**

|     |   | CP CONTENTS |                |                |                |                |                |                | RESPONSE       |                |                |

|-----|---|-------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| PL  | 1 | 2           | Q              | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | Q <sub>4</sub> | Q <sub>5</sub> | Q <sub>6</sub> | Q <sub>7</sub> |                |

| L   | Х | Х           | P <sub>0</sub> | P <sub>1</sub> | P <sub>2</sub> | Рз             | P4             | P <sub>5</sub> | P <sub>6</sub> | P <sub>7</sub> | Parallel Entry |

| H I | L | 5           | Ds             | $Q_0$          | $Q_1$          | $Q_2$          | Qз             | Q4             | Q <sub>5</sub> | $Q_6$          | Right Shift    |

| H I | Н | 5           | Q <sub>0</sub> | Q <sub>1</sub> | $Q_2$          | $Q_3$          | Q4             | Q <sub>5</sub> | $Q_6$          | $Q_7$          | No Change      |

| H   |   | L           | Ds             | $Q_0$          | Q <sub>1</sub> | $Q_2$          | Q <sub>3</sub> | Q4             | $Q_5$          | $Q_6$          | Right Shift    |

| Н   | 5 | Н           | Q <sub>0</sub> | $Q_1$          | $Q_2$          | $Q_3$          | Q4             | $Q_5$          | Q <sub>6</sub> | Q <sub>7</sub> | No Change      |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

### LOGIC DIAGRAM

| DC CHARACTERISTICS O |

|----------------------|

|----------------------|

| SYMBOL<br>los | PARAMETER                       |    | 54         | 54/74 54/74LS |     | UNITS | CONDITIONS |                                                                                                |

|---------------|---------------------------------|----|------------|---------------|-----|-------|------------|------------------------------------------------------------------------------------------------|

|               |                                 |    | Min        | Max           | Min | Max   | 0.11.10    | CONDITIONS                                                                                     |

|               | Output Short<br>Circuit Current | XM | -20<br>-18 | -55<br>-55    |     |       | mA         | V <sub>CC</sub> = Max                                                                          |

| lcc           | Power Supply Current            |    |            | 63            |     | 36    | mA         | V <sub>CC</sub> = Max, PL = \<br>P <sub>n</sub> = \_ CP <sub>1</sub> , CP <sub>2</sub> = 4.5 V |

## AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{C}$ (See Section 3 for waveforms and load configurations)

| SYMBOL       |                                                                          | 54/74                                            | 54/74LS                | UNITS | CONDITIONS      |

|--------------|--------------------------------------------------------------------------|--------------------------------------------------|------------------------|-------|-----------------|

|              | PARAMETER                                                                | C <sub>L</sub> = 15 pF<br>R <sub>L</sub> = 400 Ω | C <sub>L</sub> = 15 pF |       |                 |

|              |                                                                          | Min Max                                          | Min Max                |       |                 |

| fmax         | Maximum Clock Frequency                                                  | 20                                               | 30                     | MHz   | Figs. 3-1, 3-8  |

| tpLH<br>tpHL | Propagation Delay PL to Q <sub>7</sub> or Q <sub>7</sub>                 | 31<br>40                                         | 30<br>30               | ns    | Figs. 3-1, 3-16 |

| tPLH<br>tPHL | Propagation Delay<br>CP <sub>1</sub> to Q <sub>7</sub> or Q <sub>7</sub> | 24<br>31                                         | 30<br>30               | ns    | Figs. 3-1, 3-8  |

| tPLH<br>tPHL | Propagation Delay<br>P7 to Q7                                            | 17<br>36                                         | 25<br>30               | ns    | Figs. 3-1, 3-5  |

| tpLH<br>tpHL | Propagation Delay<br>P7 to Q7                                            | 27<br>27                                         | 30<br>25               | ns    | Figs. 3-1, 3-4  |

## AC OPERATING REQUIREMENTS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{ C}$

| SYMBOL                                   | PARAMETER                                                                                   | 54       | 54/74 |            | 74LS | UNITS  | CONDITIONS |

|------------------------------------------|---------------------------------------------------------------------------------------------|----------|-------|------------|------|--------|------------|

|                                          |                                                                                             | Min      | Max   | Min        | Max  | 5.0.75 | CONDITIONS |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>Pn to PL                                                          | 10<br>10 |       | 10<br>10   |      | ns     | Fig. 3-13  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>Pn to PL                                                           | 0        |       | 5.0<br>5.0 |      | ns     |            |

| t <sub>s</sub> (H)                       | Setup Time HIGH or LOW<br>Ds to CPn                                                         | 20<br>20 |       | 10<br>10   |      | ns     |            |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>Ds to CPn                                                          | 0        |       | 5.0<br>5.0 |      | ns     | Fig. 3-6   |

| ts (H)                                   | Setup Time HIGH<br>CP <sub>1</sub> to CP <sub>2</sub> or CP <sub>2</sub> to CP <sub>1</sub> | 30       |       | 30         |      | ns     |            |

| tw (H)                                   | CPn Pulse Width HIGH                                                                        | 25       |       | 20         |      | ns     | Fig. 3-8   |

| t <sub>w</sub> (L)                       | PL Pulse Width LOW                                                                          | 15       |       | 15         |      | ns     |            |

| trec                                     | Recovery Time PL to CPn                                                                     | 45       |       | 15         |      | ns     | Fig. 3-16  |