## ADC0801/2/3/4/5-1

## CMOS 8-BIT A/D CONVERTERS

### Preliminary

#### DESCRIPTION

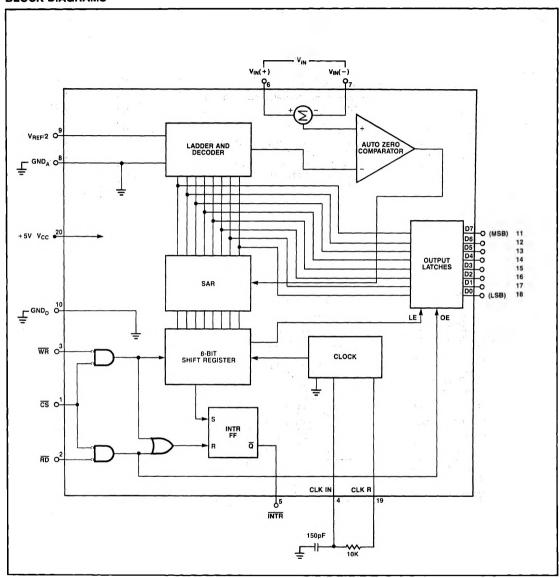

The ADC0801 family is a series of five CMOS 8-bit successive approximation A/D converters using a resistive ladder and capacitive array together with an auto-zero comparator. These converters are designed to operate with microprocessor controlled buses using a minimum of external circuitry. The three-state output data lines can be connected directly to the data bus.

The differential analog voltage input allows for increased common-mode rejection and provides a means to adjust the zero scale offset. Additionally, the voltage reference input provides a means of encoding small analog voltages to the full 8 bits of resolution.

### **FEATURES**

- · Compatible with most microprocessors

- Differential inputs

- Three-state outputs

- Logic levels TTL and MOS compatible

- Can be used with internal or external clock

- Analog input range 0V to V<sub>CC</sub>

- Single 5V supply

- Guaranteed specification with 1MHz clock

#### **APPLICATIONS**

- Transducer to microprocessor interface

- Digital thermometer

- Digitally-controlled thermostat

- Microprocessor-based monitoring and control systems

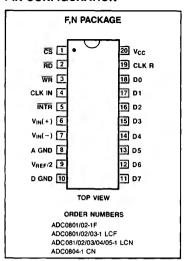

#### PIN CONFIGURATION

## **ABSOLUTE MAXIMUM RATINGS**

|                   | SYMBOL & PARAMETER                                 | RATING                         | UNIT |

|-------------------|----------------------------------------------------|--------------------------------|------|

| V <sub>cc</sub>   | Supply Voltage                                     | 6.5                            | ٧    |

|                   | Logic Control Input Voltages                       | -0.3 to + 16                   | ٧    |

|                   | All Other Input Voltages                           | -0.3 to (V <sub>CC</sub> +0.3) | ٧    |

| T <sub>A</sub>    | Operating Temperature Range<br>ADC0801/02-1 F      | -55 to +125                    | °C   |

|                   | ADC0801/02/03-1 LCF                                | -40 to +85                     | °C   |

| l                 | ADC0801/02/03/04/05-1 LCN                          | -40 to +85                     | °C   |

|                   | ADC0804-1 CN                                       | 0 to +70                       | °C   |

| T <sub>STG</sub>  | Storage Temperature                                | -65 to +150                    | °C   |

| T <sub>SOLD</sub> | Lead Soldering Temperature (10 seconds)            | 300                            | °C   |

| PD                | Package Power Dissipation at T <sub>A</sub> = 25°C | 875                            | mW   |

# CMOS 8-BIT A/D CONVERTERS

# Preliminary

## **BLOCK DIAGRAMS**

## Preliminary

DC ELECTRICAL CHARACTERISTICS  $V_{CC} = 5.0V$ ,  $f_{CLK} = 1$ MHz,  $T_{MIN} \le T_A \le T_{MAX}$ , unless otherwise specified.

| SYMBOL & PARAMETER                                       | TEST CONDITIONS                                                                              | AD    | C0801/2/3 | /4/5                     | 11611            |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------|-------|-----------|--------------------------|------------------|--|

| OTHEODE & FAMILIE                                        |                                                                                              | Min   | Тур       | Max                      | TINU             |  |

| ADC0801<br>Relative Accuracy Error (Adjusted)            | Full Scale Adjusted                                                                          |       |           | 0.25                     | LSE              |  |

| ADC0802<br>Relative Accuracy Error (Unadjusted)          | $\frac{V_{REF}}{2} = 2.500 V_{DC}$                                                           |       |           | 0.50                     | LSE              |  |

| ADC0803<br>Relative Accuracy Error (Adjusted)            | Full Scale Adjusted                                                                          |       |           | 0.50                     | LSE              |  |

| ADC0804 Relative Accuracy Error (Unadjusted)             | $\frac{V_{REF}}{2} = 2.500 V_{DC}$                                                           |       |           | 1                        | LSE              |  |

| ADC0805 Relative Accuracy Error (Unadjusted)             | $\frac{V_{REF}}{2}$ = has no connection                                                      |       |           | 1                        | LSE              |  |

| V <sub>REF</sub> Input Resistance                        |                                                                                              | 400   | 640       |                          | Ω                |  |

| Analog Input Voltage Range                               |                                                                                              | -0.05 |           | V <sub>CC</sub><br>+0.05 | ٧                |  |

| DC Common Mode Error                                     | Over Analog Input Voltage Range                                                              |       | 1/16      | 1/8                      | LSE              |  |

| Power Supply Sensitivity                                 | $V_{CC} = 5V \pm 10\%^{1}$                                                                   |       |           |                          |                  |  |

| CONTROL INPUTS                                           |                                                                                              |       |           |                          |                  |  |

| V <sub>IH</sub> Logical "1" Input Voltage                | $V_{CC} = 5.25V_{DC}$                                                                        | 2.0   |           | 15                       | V <sub>DC</sub>  |  |

| V <sub>IL</sub> Logical "0" Input Voltage                | $V_{CC} = 4.75V_{DC}$                                                                        | T     |           | 0.8                      | VDO              |  |

| I <sub>IH</sub> Logical "1" Input Current                | $V_{IN} = 5V_{DC}$                                                                           |       | 0.005     | 1                        | μA <sub>D</sub>  |  |

| I <sub>IL</sub> Logical "0" Input Current                | $V_{IN} = 0V_{DC}$                                                                           | -1    | -0.005    |                          | μA <sub>D</sub>  |  |

| CLOCK IN AND CLOCK R                                     |                                                                                              |       |           |                          |                  |  |

| V <sub>T</sub> + Clk In Positive-Going Threshold Voltage |                                                                                              | 2.7   | 3.1       | 3.5                      | V <sub>D</sub>   |  |

| V <sub>T</sub> - Clk In Negative-Going Threshold Voltage |                                                                                              | 1.5   | 1.8       | 2.1                      | V <sub>D</sub>   |  |

| $V_H$ Clk In Hysteresis $(V_{T+}) - (V_{T-})$            |                                                                                              | 0.6   | 1.3       | 2.0                      | V <sub>DC</sub>  |  |

| V <sub>OL</sub> Logical "0" Clk R Output Voltage         | $I_{OL} = 360 \mu A, V_{CC} = 4.75 V_{DC}$                                                   |       |           | 0.4                      | VDO              |  |

| V <sub>OH</sub> Logical "1" Clk R Output Voltage         | $I_{OH} = -360 \mu A$ , $V_{CC} = 4.75 V_{DC}$                                               | 2.4   |           |                          | V <sub>D</sub> C |  |

| DATA OUTPUT AND INTR                                     |                                                                                              |       |           |                          |                  |  |

| V <sub>OL</sub> Logical "0" Output Voltage               |                                                                                              |       |           |                          |                  |  |

| Data Outputs                                             | $I_{OL} = 1.6 \text{mA}, V_{CC} = 4.75 V_{DC}$                                               |       |           | 0.4                      | VDO              |  |

| INTR Outputs                                             | $I_{OL} = 1.0 \text{mA}, V_{CC} = 4.75 V_{DC}$                                               |       |           | 0.4                      | V <sub>DC</sub>  |  |

| V <sub>OH</sub> Logical "1" Output Voltage               | $I_{OH} = -360 \mu A, V_{CC} = 4.75 V_{DC}$                                                  | 2.4   |           |                          | VDO              |  |

|                                                          | $I_{OH} = -10\mu A$ , $V_{CC} = 4.75 V_{DC}$                                                 | 4.5   |           |                          | V <sub>DC</sub>  |  |

| I <sub>OZL</sub> 3-State Output Leakage                  | V <sub>OUT</sub> = OV <sub>DC</sub> , $\overline{CS}$ = Logical "1"                          | -3    |           |                          | μA <sub>D</sub>  |  |

| I <sub>OZH</sub> 3-State Output Leakage                  | V <sub>OUT</sub> = 5V <sub>DC</sub> , $\overline{\text{CS}}$ = Logical "1"                   |       |           | 3                        | μA <sub>D</sub>  |  |

| I <sub>SC</sub> + Output Short Circuit Current           | V <sub>OUT</sub> = O <sub>V</sub> , T <sub>A</sub> = 25°C                                    | 4.5   | 6         |                          | mA <sub>C</sub>  |  |

| I <sub>SC</sub> - Output Short Circuit Current           | $V_{OUT} = V_{CC}, T_A = 25^{\circ}C$                                                        | 9.0   | 16        |                          | mA <sub>□</sub>  |  |

| I <sub>CC</sub> Power Supply Current                     | $f_{CLK} = 1MHz$ , $V_{REF/2} = Open$<br>$\overline{CS} = Logical "1"$ , $T_A = 25^{\circ}C$ |       | 3.0       | 3.5                      | mA               |  |

NOTE

<sup>1.</sup> Analog inputs must remain within the range:  $-0.05 \le V_{IN} \le V_{CC} + 0.05V$ .

# ADC0801/2/3/4/5-1

# **CMOS 8-BIT A/D CONVERTERS**

# Preliminary

### **AC ELECTRICAL CHARACTERISTICS**

|                                     | VMDOL . DADAMETED                 | 70      | FROM        | TEST CONDITIONS                                      | ADC0801/2/3/4/5 |     |       | UNIT   |

|-------------------------------------|-----------------------------------|---------|-------------|------------------------------------------------------|-----------------|-----|-------|--------|

| SYMBOL & PARAMETER  Conversion Time |                                   | TO FROM |             | TEST CONDITIONS                                      | Min Typ         | Тур | Max   |        |

|                                     |                                   |         |             | f <sub>CLK</sub> = 1MHz <sup>1</sup>                 | 66              |     | 73    | μS     |

| f <sub>CLK</sub>                    | Clock Frequency                   |         |             | See Note 1.                                          | 0.1             | 1.0 | 3.0   | MHz    |

|                                     | Clock Duty Cycle                  |         |             | See Note 1.                                          | 40              |     | 60    | %      |

| CR                                  | Free-Running Conversion Rate      |         |             | CS = 0, f <sub>CLK</sub> = 1MHz<br>INTR Tied To WR   |                 |     | 13690 | conv/s |

| tw(WR)L                             | Start Pulse Width                 |         |             | <u>CS</u> = 0                                        | 30              |     |       | ns     |

| t <sub>ACC</sub>                    | Access Time                       | Output  | RD          | <del>CS</del> = 0, C <sub>L</sub> = 100 pF           |                 | 75  | 100   | ns     |

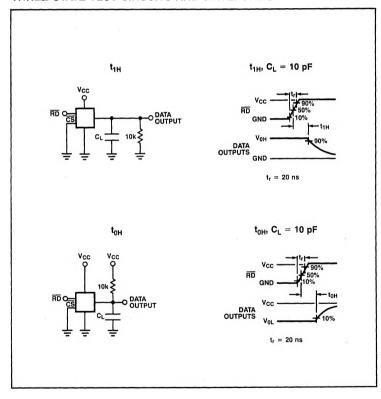

| t <sub>1H</sub> , t <sub>OH</sub>   | Three-State Control               | Output  | RD          | CL = 10 pF, RL = 10K<br>See Three-State Test Circuit |                 | 70  | 100   | ns     |

| t <sub>W1</sub> , t <sub>R1</sub>   | INTR Delay                        | INTR    | WD<br>or RD |                                                      |                 | 100 | 150   | ns     |

| C <sub>IN</sub>                     | Logic Input = Capacitance         |         |             |                                                      |                 | 5   | 7.5   | рF     |

| C <sub>OUT</sub>                    | Three-State Output<br>Capacitance |         |             |                                                      |                 | 5   | 7.5   | pF     |

NOTE:

<sup>1.</sup> Accuracy is guaranteed at f<sub>CLK</sub> =1MHz. Accuracy may degrade at higher clock frequencies.

## ADC0801/2/3/4/5-1

## CMOS 8-BIT A/D CONVERTERS

### Preliminary

#### **FUNCTIONAL DESCRIPTION**

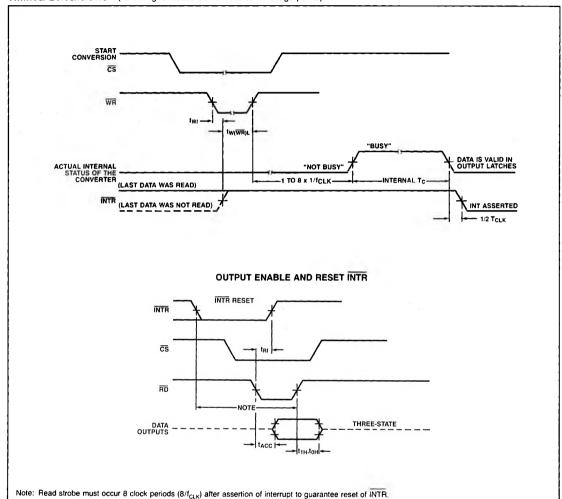

The ADC0801 through ADC0805 series of A/D converters are successive approximation devices with 8-bit resolution and no missing codes. The most significant bit is tested first and after 64 clock cycles a digital 8-bit binary word is transferred to an output latch and the INTR pin goes low, indicating that conversion is complete. A conversion in progress can be interrupted by issuing another start command. The device may be operated in a continuous conversion mode by connecting the INTR and WR pins together and holding the CS pin low. To insure start-up when connected this way, an external WR pulse is required at power-up.

As the  $\overline{\text{WR}}$  input goes low, when  $\overline{\text{CS}}$  is low, the SAR is cleared and remains so as long as these two inputs are low. Conversion begins between 1 and 8 clock periods after at least one of these inputs goes high. As the conversion begins, the  $\overline{\text{INTR}}$  line goes high. Note that the  $\overline{\text{INTR}}$  line will remain low until 1 to 8 clock cycles after either the  $\overline{\text{WR}}$  or the  $\overline{\text{CS}}$  input (or both) goes high.

When the  $\overline{CS}$  and  $\overline{RD}$  inputs are both brought low to read the data, the  $\overline{INTR}$  line will go low and the three-state output latches are enabled.

The digital control lines ( $\overline{CS}$ ,  $\overline{RD}$ , and  $\overline{WR}$ ) operate with standard TTL levels and have been renamed when compared with standard A/D Start and Output Enable labels. For non-microprocessor based applications, the  $\overline{CS}$  pin can be grounded, the  $\overline{WR}$  pin can be interpreted as a  $\overline{START}$  pulse pin, and the  $\overline{RD}$  pin performs the OE (Output Enable) function.

The  $V_{\text{IN}}(-)$  input can be used to subtract a fixed voltage from the input voltage. Because there is a time interval between sampling the  $V_{\text{IN}}(+)$  and the V(-) inputs, it is important that these inputs remain constant, during the entire conversion cycle.

#### THREE-STATE TEST CIRCUITS AND WAVEFORMS

# **CMOS 8-BIT A/D CONVERTERS**

# Preliminary

TIMING DIAGRAMS (All timing is measured from the 50% voltage points)