SBAS124C - DECEMBER 1999 - REVISED DECEMBER 2005

# 12-BIT, 52-kSPS, DATA ACQUISITION SYSTEM WITH ANALOG-TO-DIGITAL CONVERTER, MUX, PGA, AND REFERENCE

### **FEATURES**

- PGA Gains: 1, 2, 4, 5, 8, 10, 16, 20 V/V

- Programmable Input (Up to 4-Channel Differential/Up to 8-Channel Single-Ended or Some Combination)

- 1.15-V, 2.048-V, or 2.5-V Internal Reference

- SPI/DSP Compatible Serial Interface (≤ 20 MHz)

- Throughput Rate: 52 kSamples/sec

- Error Overload Indicator

- Programmable Output 2s Complement/Binary

- 2.7-V to 5.5-V Single Supply Operation

- 4-Bit Digital I/O Via Serial Interface

- Pin-Compatible With ADS7871

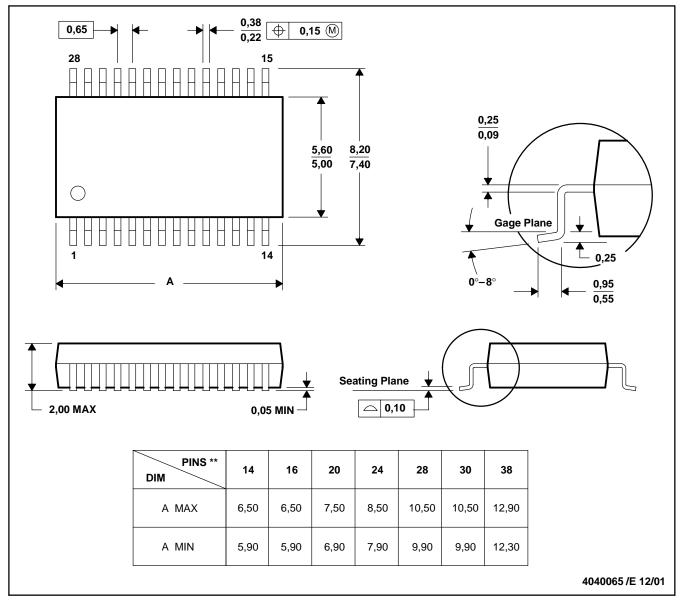

- SSOP-28 Package

#### **APPLICATIONS**

- Portable Battery-Powered Systems

- Low-Power Instrumentation

- Low-Power Control Systems

- Smart Sensor Applications

#### DESCRIPTION

The ADS7870 (US patents 6140872, 6060874) is a complete low-power data acquisition system on a single chip. It consists of a 4-channel differential/8-channel single-ended multiplexer, precision programmable gain amplifier, 12-bit successive approximation analog-to-digital (A/D) converter, and a precision voltage reference.

The programmable-gain amplifier provides high input impedance, excellent gain accuracy, good common-mode rejection, and low noise.

For many low-level signals, no external amplification or impedance buffering is needed between the signal source and the A/D input.

The offset voltage of the PGA is auto-zeroed. Gains of 1, 2, 4, 5, 8, 10, 16, and 20 V/V allow signals as low as 125 mV to produce full-scale digital outputs.

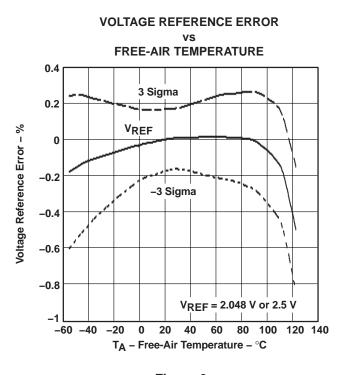

The ADS7870 contains an internal reference, which is trimmed for high initial accuracy and stability vs temperature. Drift is typically 10 ppm/°C. An external reference can be used in situations where multiple ADS7870s share a common reference.

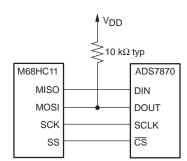

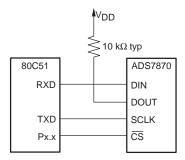

The serial interface allows the use of SPI™, QSPI™, Microwire™, and 8051-family protocols, without glue logic.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

QSPI and SPI are trademarks of Motorola, Inc.

Microwire is a trademark of National Semiconductor Corporation. All other trademarks are the property of their respective owners.

# ORDERING INFORMATION(1)

| PRODUCT     | PACKAGE-LEAD          | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|-------------|-----------------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| A D.0.70.70 | 000D 00 0f Mt         | -                     | 4000 4- + 0500                    | ADS7870            | ADS7870IDB         | Rails, 48                    |

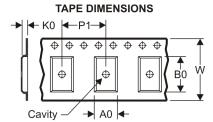

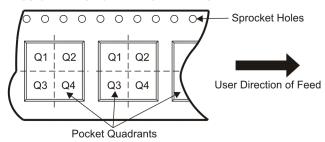

| ADS7870     | SSOP-28 Surface Mount | DB                    | –40°C to +85°C                    | ADS7870            | ADS7870IDBR        | Tape and Reel, 1000          |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI web site at www.ti.com.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

|                    |                             |            |  | UNIT                                   |

|--------------------|-----------------------------|------------|--|----------------------------------------|

| Supply voltage, V  | 'DD                         |            |  | 5.5 V                                  |

|                    | land amount                 | Momentary  |  | 100 mA                                 |

| Analog inputs      | Input current               | Continuous |  | 10 mA                                  |

|                    | Input voltage               |            |  | V <sub>DD</sub> + 0.5 V to GND – 0.5 V |

| Operating free-air | r temperature range,        | ГА         |  | –40°C to 85°C                          |

| Storage temperat   | ure range, T <sub>STG</sub> |            |  | −65°C to 150°C                         |

| Junction tempera   | ture (T <sub>J</sub> max)   | 150°C      |  |                                        |

| Lead temperature   | e, soldering (10 sec)       |            |  | 300°C                                  |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

For the Total System  $^{(1)}$ ,  $-40^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85 $^{\circ}$ C,  $V_{DD}$  = 5 V, BUFIN = 2.5 V (using external reference), 2.5-MHz CCLK and 2.5-MHz SCLK (unless otherwise noted).

| PAF                          | RAMETER                                   | TEST CONDITIONS                                             | MIN                                       | TYP      | MAX                   | UNIT      |

|------------------------------|-------------------------------------------|-------------------------------------------------------------|-------------------------------------------|----------|-----------------------|-----------|

| Analog Input                 |                                           |                                                             | 1                                         |          |                       |           |

| Input voltage (LNx inputs)   |                                           | Linear operation                                            | -0.2                                      |          | V <sub>DD</sub> + 0.2 | V         |

| Input capacitance (2)        |                                           |                                                             |                                           | 4 to 9.7 |                       | pF        |

| (2)                          | Common mode                               |                                                             |                                           | 6        |                       |           |

| Input impedance (2)          | Differential                              |                                                             |                                           | 7        |                       | MΩ        |

| Channel-to-channel cross     | talk                                      | V <sub>I</sub> = 2 V <sub>PP</sub> , 60 Hz (3)              |                                           | 100      |                       | dB        |

| Maximum leakage current      | i                                         |                                                             |                                           | 100      |                       | pA        |

| Static Accuracy              |                                           |                                                             |                                           |          | <u>.</u>              |           |

| Resolution                   |                                           |                                                             |                                           | 12       |                       | Bits      |

| No missing codes             |                                           | G = 1 to 20 V/V                                             | 12                                        |          |                       | Bits      |

| Integral linearity           |                                           | G = 1 to 20 V/V                                             | -2.5                                      | ±2       | 2.5                   | LSB       |

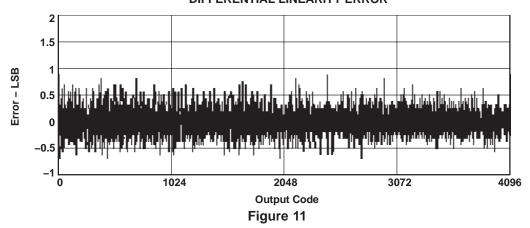

| Differential linearity       |                                           | G = 1 to 20 V/V                                             |                                           | ±0.5     |                       | LSB       |

| Offset error                 |                                           | G = 1 to 20 V/V                                             | -6                                        | ±1       | 6                     | LSB       |

|                              | Ratiometric configuration or              | G = 1 to 10 V/V                                             | -0.2                                      |          | 0.2                   | %FSR      |

|                              | external reference (4)                    | G = 16 and 20 V/V                                           | -0.25                                     |          | 0.25                  | %FSR      |

| Full-scale gain error        |                                           | G = 1 to 10 V/V                                             | -0.35                                     |          | 0.35                  | %FSR      |

|                              | Internal reference                        | G = 16 and 20 V/V                                           | -0.4                                      |          | 0.4                   | %FSR      |

| DC common-mode rejecti       | on ratio, RTI                             | V <sub>I</sub> = -0.2 V to 5.2 V,<br>G = 20 V/V             | 92                                        |          |                       | dB        |

| Power supply rejection rate  | tio, RTI                                  | $V_{DD} = 5 \text{ V} \pm 10\%, \text{ G} = 20 \text{ V/V}$ | V <sub>DD</sub> = 5 V ±10%, G = 20 V/V 86 |          |                       |           |

| Dynamic Characteristics      | 3                                         |                                                             |                                           |          |                       |           |

|                              | Continuous mode                           | One channel                                                 |                                           |          | 52                    |           |

| Throughput rate              | Address mode                              | Different channels                                          |                                           |          | 52                    | ksample/s |

| External clock, CCLK (5)     |                                           |                                                             | 0.1                                       |          | 20                    | MHz       |

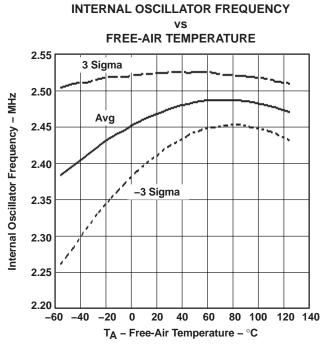

| Internal oscillator frequenc | су                                        |                                                             |                                           | 2.5      |                       | MHz       |

| Serial interface clock, SCI  | LK                                        |                                                             |                                           |          | 20                    | MHz       |

| Data setup time              |                                           |                                                             | 10                                        |          |                       | ns        |

| Data hold time               |                                           |                                                             | 10                                        |          |                       | ns        |

| Digital Inputs               |                                           |                                                             |                                           |          |                       |           |

|                              | Low-level input voltage, V <sub>IL</sub>  |                                                             |                                           |          | 0.8                   | V         |

|                              | I Bala Java Langue volta va 37            | V <sub>DD</sub> ≤ 3.6 V                                     | 2                                         |          |                       | V         |

| Logic levels                 | High-level input voltage, V <sub>IH</sub> | V <sub>DD</sub> > 3.6 V                                     | 3                                         |          |                       | V         |

|                              | Low-level input current, I <sub>IL</sub>  |                                                             |                                           |          | 1                     |           |

|                              | High-level input current, I <sub>IH</sub> |                                                             |                                           |          | 1                     | μΑ        |

<sup>(1)</sup> The specifications for the total system are overall analog input to digital output specifications. The specifications for internal functions indicate the performance of the individual functions in the ADS7870.

<sup>(2)</sup> The ADS7870 uses switched capacitor techniques for the programmable gain amplifier and A/D converter. A characteristic of such circuits is that the input capacitance at any selected LNx pin changes during the conversion cycle.

<sup>(3)</sup> One channel on with its inputs grounded. All other channels off with sinewave voltage applied to their inputs.

<sup>(4)</sup> Ratiometric configuration exists when the input source is configured such that changes in the reference cause corresponding changes in the input voltage. The same accuracy applies when a perfect external reference is used.

<sup>(5)</sup> The CCLK is divided by the DF value specified by the contents of register 3, A/D Control register, bits D0 and D1 to produce DCLK. The maximum value of DCLK is 2.5 MHz.

# **ELECTRICAL CHARACTERISTICS**

For the Total System  $^{(1)}$ ,  $-40^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85 $^{\circ}$ C,  $V_{DD}$  = 5 V, BUFIN = 2.5 V (using external reference), 2.5-MHz CCLK and 2.5-MHz SCLK (unless otherwise noted).

| PA                                  | RAMETER                           | TEST CONDITIONS                                     | MIN                   | TYP     | MAX                   | UNIT   |

|-------------------------------------|-----------------------------------|-----------------------------------------------------|-----------------------|---------|-----------------------|--------|

| Digital Outputs                     |                                   |                                                     |                       |         |                       |        |

| Data coding                         |                                   | Binary 2s complement                                |                       |         |                       |        |

|                                     |                                   | I <sub>SINK</sub> = 5 mA                            |                       |         | 0.4                   | .,     |

|                                     | Low-level output voltage, VOL     | I <sub>SINK</sub> = 16 mA                           |                       | 0.8     |                       | V      |

| Logic levels                        |                                   | ISOURCE = 0.5 mA                                    | V <sub>DD</sub> – 0.4 |         |                       |        |

|                                     | High-level output voltage, VOH    | ISOURCE = 5 mA                                      |                       | 4.6     |                       | V      |

| Leakage current                     |                                   | Hi-Z state, $V_O = 0 V$ to $V_{DD}$                 |                       |         | 1                     | μΑ     |

| Output capacitance                  |                                   |                                                     |                       | 5       |                       | pF     |

| Voltage Reference                   |                                   |                                                     |                       |         |                       |        |

| Bandgap voltage                     | V <sub>REF</sub> = 2.048 V, 2.5 V | Pin 26 used as output, Use internal OSC or external | -0.25                 | ±0.05   | 0.25                  | %FSR   |

| reference                           | V <sub>REF</sub> = 1.15 V         | CCLK as conversion clock                            |                       | 1.15    |                       | V      |

| Output drive                        |                                   |                                                     |                       | ±0.6    |                       | μΑ     |

| Reference Buffer                    |                                   | ·                                                   |                       |         |                       | -      |

| Input voltage, BUFIN                |                                   |                                                     | 0.9                   |         | V <sub>DD</sub> – 0.2 | V      |

| Input impedance, BUFIN              |                                   | At pin 27                                           |                       | 1000  3 |                       | GΩ  pF |

| Input offset                        |                                   |                                                     | -10                   | ±1      | 10                    | mV     |

| Output voltage accuracy v           | s temperature,                    | Pin 28 used as output,                              | -0.25                 | ±0.05   | 0.25                  | %FSR   |

| BUFOUT/REFIN (2) (3)                | •                                 | V <sub>REF</sub> = 2.048 V and 2.5 V                |                       | 10      | 50                    | ppm/°C |

| Output drive, BUFOUT/RE             | FIN                               |                                                     |                       | 20      |                       | mA     |

| Power Supply Requirem               | ents                              |                                                     |                       |         |                       |        |

| Supply voltage                      |                                   |                                                     | 2.7                   |         | 5.5                   | V      |

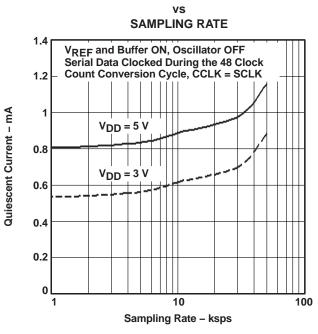

|                                     | 1-kHz Sample rate                 | REF and BUF on, Internal os-<br>cillator on         |                       | 0.45    |                       | mA     |

| Power supply current (2)            | 50-kHz Sample rate                | REF and BUF on, External CCLK                       |                       | 1.2     | 1.7                   | mA     |

|                                     | Power down                        | REF, BUF, Internal oscillator off                   |                       |         | 1                     | μА     |

|                                     | 1-kHz Sample rate                 | REF and BUF on, Internal oscillator on              |                       | 2.25    |                       | mW     |

| Power dissipation (2)               | 50-kHz Sample rate                | REF and BUF on, External CCLK                       |                       | 6       | 8.5                   | mW     |

|                                     | Power down                        | REF and BUF off                                     |                       |         | 5                     | μW     |

| Temperature Range                   | •                                 | •                                                   | •                     |         |                       |        |

| Operating free-air                  |                                   |                                                     | -40                   |         | 85                    | °C     |

| Storage range                       |                                   |                                                     | -65 1t                |         |                       | °C     |

| Thermal resistance, Θ <sub>JA</sub> |                                   |                                                     |                       | 65      |                       | °C/W   |

<sup>(1)</sup> The specifications for the total system are overall analog input to digital output specifications. The specifications for internal functions indicate the performance of the individual functions in the ADS7870.

<sup>(2)</sup> REF and BUF contribute 190 μA and 150 μA (950 μW and 750 μW) respectively. At initial power up the default condition for both REF and BUF functions is power off. They can be turned on under software control by writing a 1 to D3 and D2 of register 7, REF/OSCILLATOR CONTROL register.

<sup>(3)</sup> For  $V_{DD}$  < 3 V,  $V_{REF}$  = 2.5 V is not usable.

# **ELECTRICAL CHARACTERISTICS**

For Internal Functions  $^{(1)}$ ,  $-40^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85 $^{\circ}$ C,  $V_{DD}$  = 5 V, BUFIN = 2.5 V (using external reference), 2.5-MHz CCLK and 2.5-MHz SCLK (unless otherwise noted).

| PARA                        | METER                                    | TEST CONDITIONS                                | MIN TYP                    | MAX UNIT |

|-----------------------------|------------------------------------------|------------------------------------------------|----------------------------|----------|

| Multiplexer                 |                                          |                                                |                            | <u>'</u> |

| On resistance               |                                          |                                                | 100                        | Ω        |

| Off resistance              |                                          |                                                | 1                          | GΩ       |

| Off channel leakage         | On channel = 5.2 V,<br>Off channel = 0 V | V <sub>LNx</sub> = 5.2 V                       | 100                        | рА       |

| current                     | On channel = 0 V,<br>Off channel = 5.2 V |                                                | 100                        | pA       |

| On channel leakage          | On channel = 5.2 V,<br>Off channel = 0 V |                                                | 100                        | pA       |

| current                     | On channel = 0 V,<br>Off channel = 5.2 V |                                                | 100                        | pA       |

| PGA Amplifier               |                                          |                                                |                            |          |

| Input capacitance (2)       |                                          |                                                | 4 to 9.7                   | pF       |

| (2)                         | Common mode                              |                                                | 6                          | MΩ       |

| Input impedance (2)         | Differential                             |                                                | 7                          | MΩ       |

| Offset voltage              | <u> </u>                                 |                                                | 100                        | μV       |

| Small signal bandwidth      |                                          |                                                | 5/Gain                     | MHz      |

| 0                           |                                          | G = 1                                          | 0.3                        | μs       |

| Settling time               |                                          | G = 20                                         | 6.4                        | μs       |

| Analog-To-Digital Con       | verter DC Characteristic                 | s                                              |                            |          |

| Resolution                  |                                          |                                                | 12                         | Bits     |

| Integral linearity error    |                                          |                                                | ±0.5                       | LSB      |

| Differential linearity erro | r                                        |                                                | ±0.5                       | LSB      |

| No missing codes            |                                          |                                                | 12                         | Bits     |

| Offset error                |                                          | REFIN = 2.5 V                                  | ±0.5                       | LSB      |

| Full-scale (gain) error     |                                          |                                                | ±0.02                      | %        |

| Common mode rejection       | n, RTI of A/D                            |                                                | 80                         | dB       |

| Power supply rejection,     | RTI of ADS7870                           | External reference, V <sub>DD</sub> = 5 V ±10% | 60                         | dB       |

| PGA Plus A/D Convert        | ter Sampling Dynamics                    | f <sub>CCLK</sub> = 2.5 MHz, DF = 1            |                            |          |

| Throughput rate             |                                          | 48 CCLK cycles                                 | 52                         | kHz      |

| Conversion time             |                                          | 12 CCLK cycles                                 | 4.8                        | μs       |

| Acquisition time            |                                          | 28 CCLK cycles                                 | 9.6                        | μs       |

| Auto zero time              |                                          | 8 CCLK cycles                                  | 3.2                        | μs       |

| Aperture delay              |                                          | 36 CCLK cycles                                 | 12.8                       | μs       |

| Small signal bandwidth      |                                          |                                                | 5                          | MHz      |

| Step response               |                                          |                                                | 1 Complete Conversion Cycl | е        |

<sup>(1)</sup> The specifications for the total system are overall analog input to digital output specifications. The specifications for internal functions indicate the performance of the individual functions in the ADS7870.

<sup>(2)</sup> The ADS7870 uses switched capacitor techniques for the programmable gain amplifier and A/D converter. A characteristic of such circuits is that the input capacitance at any selected LNx pin changes during the conversion cycle.

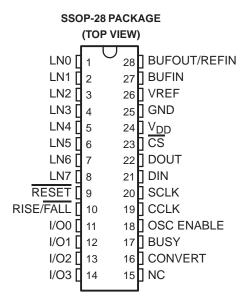

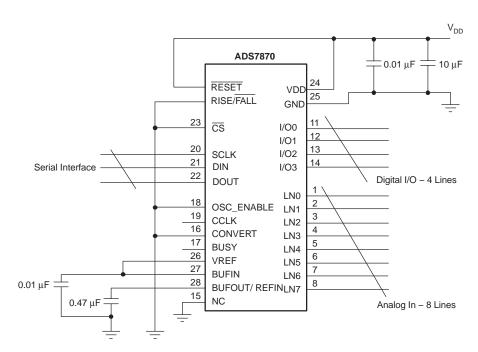

# **PIN ASSIGNMENTS**

# **Terminal Functions**

|       | TERMINAL     |     |                                                                                                                                                                                                                                                                                                                                                                         |

|-------|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.   | NAME         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                             |

| 1–8   | LN0-LN7      | Al  | MUX input lines 0–7                                                                                                                                                                                                                                                                                                                                                     |

| 9     | RESET        | DI  | Master reset, zeros all registers                                                                                                                                                                                                                                                                                                                                       |

| 10    | RISE/FALL    | DI  | Sets the active edge for SCLK. 0 sets SCLK active on falling edge. 1 sets SCLK active on rising edge.                                                                                                                                                                                                                                                                   |

| 11–14 | I/O0-I/O3    | DIO | Digital input or output signal                                                                                                                                                                                                                                                                                                                                          |

| 15    | NC           | -   | No connection or internal function. It is recommended that this pin be tied to ground.                                                                                                                                                                                                                                                                                  |

| 16    | CONVERT      | DI  | 0 to 1 transition starts a conversion cycle.                                                                                                                                                                                                                                                                                                                            |

| 17    | BUSY         | DO  | 1 indicates converter is busy                                                                                                                                                                                                                                                                                                                                           |

| 18    | OSC ENABLE   | DI  | 0 sets CCLK as an input, 1 sets CCLK as an output and turns the oscillator on.                                                                                                                                                                                                                                                                                          |

| 19    | CCLK         | DIO | If OSC ENABLE = 1, then the internal oscillator is output to this pin. If OSC ENABLE = 0, then this is the input pin for an external conversion clock.                                                                                                                                                                                                                  |

| 20    | SCLK         | DI  | Serial data input/output transfer clock. Active edge set by the RISE/FALL pin. If RISE/FALL is low, SCLK is active on the falling edge.                                                                                                                                                                                                                                 |

| 21    | DIN          | DIO | Serial data input. In the 3-wire mode, this pin is used for serial data input. In the 2-wire mode, serial data output appears on this pin as well as the DOUT pin.                                                                                                                                                                                                      |

| 22    | DOUT         | DO  | Serial data output. This pin is driven when $\overline{CS}$ is low and is high impedance when $\overline{CS}$ is high. This pin behaves the same in both 3-wire and 2-wire modes.                                                                                                                                                                                       |

| 23    | <u>CS</u>    | DI  | Chip select. When $\overline{CS}$ is low, the serial interface is enabled. When $\overline{CS}$ is high, the serial interface is disabled, the DOUT pin is high impedance, and the DIN pin is an input. The $\overline{CS}$ pin only affects the operation of the serial interface. It does not directly enable/disable the operation of the signal conversion process. |

| 24    | $V_{DD}$     | -   | Power supply voltage, 2.7 V to 5.5 V                                                                                                                                                                                                                                                                                                                                    |

| 25    | GND          | -   | Power supply ground                                                                                                                                                                                                                                                                                                                                                     |

| 26    | VREF         | AO  | 2.048-/2.5-V on-chip voltage reference                                                                                                                                                                                                                                                                                                                                  |

| 27    | BUFIN        | Al  | Input to reference buffer amplifier                                                                                                                                                                                                                                                                                                                                     |

| 28    | BUFOUT/REFIN | AIO | Output from reference buffer amplifier and reference input to ADC                                                                                                                                                                                                                                                                                                       |

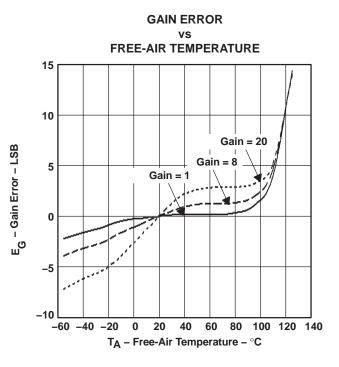

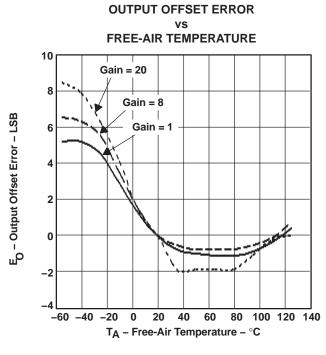

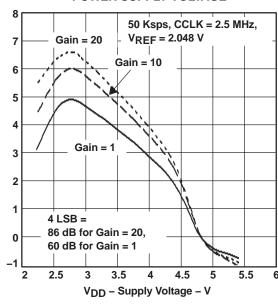

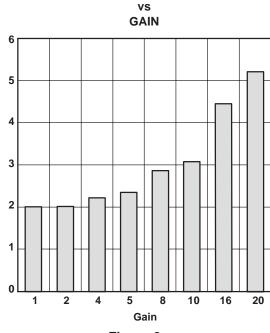

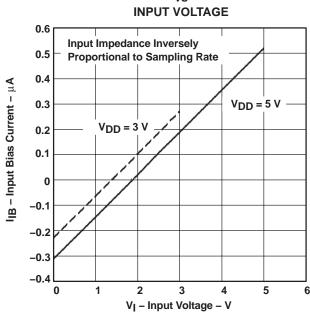

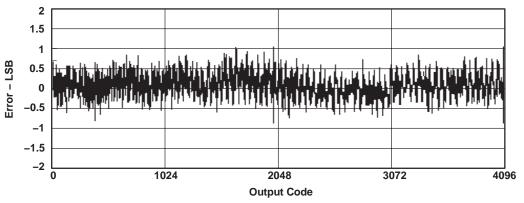

# TYPICAL PERFORMANCE CURVES<sup>†</sup>

Figure 1

Figure 2

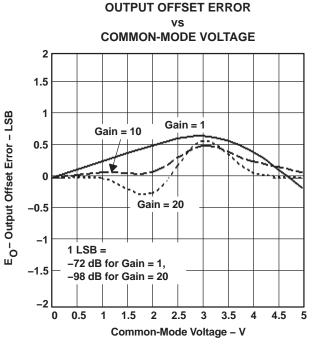

Figure 3

Figure 4

<sup>†</sup> At TA= 25°C, VDD = 5 V, VREF = 2.5 V connected to BUFIN (using internal reference), 2.5 MHz CCLK, and 2.5 MHz SCLK (unless otherwise noted)

Figure 5

**QUIESCENT CURRENT**

Figure 7

# **OUTPUT OFFSET ERROR POWER SUPPLY VOLTAGE**

E<sub>O</sub> - Output Offset Error - LSB

Peak-to-Peak Output Noise - LSB

Figure 6

#### **PEAK-TO-PEAK OUTPUT NOISE**

Figure 8

# INPUT BIAS CURRENT vs

Figure 9

## INTEGRAL LINEARITY ERROR

Figure 10

# **DIFFERENTIAL LINEARITY ERROR**

#### **OVERVIEW**

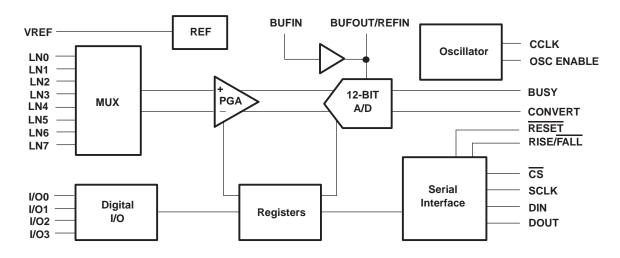

The ADS7870 is a complete data acquisition device composed of an input analog multiplexer (MUX), a programmable gain amplifier (PGA) and an analog-to-digital (A/D) converter. Four lines of digital input/output (I/O) are also provided. Additional circuitry provides support functions including conversion clock, voltage reference, and serial interface for control and data retrieval.

Control and configuration of the ADS7870 are accomplished by command bytes written to internal registers through the serial port. Command register device control includes MUX channel selection, PGA gain, A/D start conversion command, and I/O line control. Command register configuration control includes internal voltage reference setting and oscillator control.

Operational modes and selected functions can be activated by digital inputs at corresponding pins. Pin settable configuration options include SCLK active-edge selection, master reset, and internal oscillator clock enable.

The ADS7870 has eight analog signal input pins, LN0 through LN7. These pins are connected to a network of analog switches (the MUX). The inputs can be configured as 8 single-ended or 4 differential inputs, or some combination.

The four general-purpose digital I/O pins (I/O3 through I/O0) can be made to function individually as either digital inputs or digital outputs. These pins give the user access to four digital I/O pins through the serial interface without having to run additional wires to the host controller.

The programmable gain amplifier (PGA) provides gains of 1, 2, 4, 5, 8, 10, 16, and 20 V/V.

The 12-bit A/D converter in the ADS7870 is a successive approximation type. The default output of the converter is 2s complement format and can be read in a variety of ways depending on the program configuration.

The ADS7870 internal voltage reference can be software configured for output voltages of 1.15 V, 2.048 V, or 2.5 V. The reference circuit is trimmed for high initial accuracy and low temperature drift. A separate buffer amplifier is provided to buffer the high impedance VREF output.

The voltage reference, PGA, and A/D converter use the conversion clock (CCLK) and signals derived from it. CCLK can be either an input or output signal. The ADS7870 can divide the CCLK signal by a constant before it is applied to the A/D converter and PGA. This allows a higher frequency system clock to be used to control the A/D converter operation. Division factors (DF) of 1, 2, 4, and 8 are available. The signal that is actually applied to the PGA and A/D converter is DCLK, where DCLK = CCLK/DF.

The ADS7870 is designed so that its serial interface can be conveniently used with a wide variety of microcontrollers. It has four conventional serial interface pins: SCLK (serial data clock), DOUT (serial data out), DIN (serial data in, which may be set bidirectional in some applications), and  $\overline{CS}$  (chip select function).

The ADS7870 has ten internal user accessible registers which are used in normal operation to configure and control the device (summarized in Figure 15).

#### **FUNCTIONAL DESCRIPTION**

#### Multiplexer

The ADS7870 has eight analog signal input pins, LN0 through LN7. These pins are connected to a network of analog switches (the MUX block in the block diagram). The switches are controlled by four bits in the Gain/Mux register.

LN0 through LN7 can be configured as 8 single-ended inputs or 4 differential inputs or some other combination. Some MUX combination examples are shown in Figure 20. The differential polarity of the input pins can be changed with the M2 bit in the MUX address. This feature allows reversing the polarity of the conversion result without having to physically reverse the input connections to the ADS7870.

For linear operation, the input signal at any of the LN0 through LN7 pins can range between GND - 0.2 V and  $V_{DD}$  + 0.2 V. The polarity of the differential signal can be changed through commands written to the Gain/Mux register, but each line must remain within the linear input common mode voltage range.

Inputs LN0 through LN7 have ESD protection circuitry as the first active elements on the chip. These contain protection diodes connected to VDD and GND that remain reverse biased under normal operation. If input voltages are expected beyond the absolute maximum voltage range, it is necessary to add resistance in series with the input to limit the current to 10 mA or less.

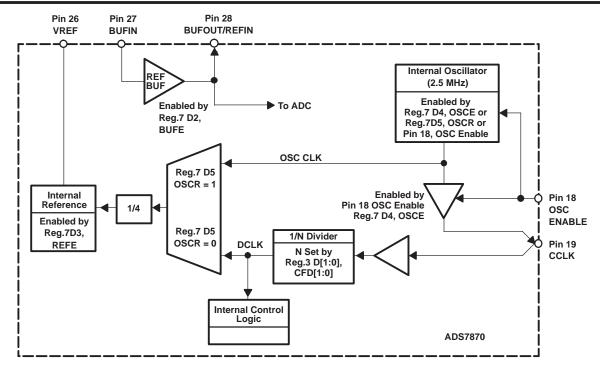

#### **Conversion Clock**

The conversion clock (CCLK) and signals derived from it are used by the voltage reference, the PGA, and the A/D converter. The CCLK pin can be made either an input or an output. For example, one ADS7870 can be made to be the conversion clock master (CCLK is an output), while the others are slaved to it with their CCLK pins all being inputs (by default). This can reduce A/D conversion errors caused by multiple clocks and other systems noise.

When the OSC ENABLE pin is low or zero, the CCLK pin is an input and the ADS7870 relies on an applied external clock for the conversion process. When OSC ENABLE is high or if the OSCE bit D4 in register 7 is set to a one, the internal oscillator and an internal buffer is enabled, making pin 19 an output. Either way the CCLK is sensed internally at the pin so all ADS7870s see the same clock delays. Capacitive loading on the CCLK pin can draw significant current compared with the supply current to the ADS7870 ( $I_{LOAD} = f_{CCLK} \times V_{DD} \times C_{LOAD}$ ).

The internal reference requires a continuous clock and may be supplied by the internal oscillator independently of the system clock driving the CCLK pin. Setting OSCR (bit D5 in register 7) and REFE (bit D3 in register 7) both to one accomplishes this. Figure 12 illustrates all of these relationships.

The ADS7870 utilizes the power saving technique of turning on and off the biasing for the PGA and A/D as needed. This does not apply to the oscillator, reference, and buffer, these run continuously when enabled. The buffer output is high impedance when disabled, so for a low power data logging application the filter capacitor is not discharged when the buffer is turned off, and does not require as much settling time when turned on.

The serial interface clock is independent of the conversion clock and can run faster or slower. If it is desirable to use a faster system clock than the 2.5-MHz nominal rate that the ADS7870 uses then this clock may be divided to a slower rate (1/2, 1/4, 1/8) by setting the appropriate bits in register 3. This clock divider applies equally to an external as well as internal clock to create the internal DCLK for the PGA and A/D conversion cycle.

The ADS7870 has both maximum and minimum DCLK frequency constraints (DCLK = CCLK/DF). The maximum DCLK is 2.5 MHz. The minimum DCLK frequency applied to the PGA, reference, and A/D is 100 kHz.

Figure 12. Block Diagram With Internal and External Clocks and References

## Voltage Reference and Buffer Amplifier

The ADS7870 uses a patented switched capacitor implementation of a band-gap reference. The circuit has curvature correction for drift and can be software configured for output voltages of 1.15 V, 2.048 V, or 2.5 V (default). The internal reference output (VREF) is not designed to drive a typical load; a separate buffer amplifier must be used to supply any load current.

The internal reference buffer (REFBUF) can source many tens of milliamps to quickly charge a filter capacitor tied to its output, but it can only typically sink 200  $\mu$ A. If there is any significant noise on the REFIN pin, then a resistor to ground ( $\geq$  250  $\Omega$ ) would improve the buffers ability to recover from a positive going noise spike. This would, of course, be at the expense of power dissipation.

The temperature compensation of the onboard reference is adjusted with the reference buffer in the circuit. Performance is specified in this configuration.

#### **Programmable Gain Amplifier**

The programmable gain amplifier (PGA) provides gains of 1, 2, 4, 5, 8, 10, 16, and 20 V/V. The PGA is a single supply, rail-to-rail input, auto-zeroed, capacitor based instrumentation amplifier. PGA gain is set by bits G2 through G0 of register 4.

The ability to detect when the PGA outputs are driven to clipping, or nonlinear operation, is provided by the least significant bit of the output data (register 0) being set to one. This result is the logical OR of fault detecting comparators within the ADS7870 monitoring the outputs of the PGA. The inputs are also monitored, for problems, often due to ac common mode or low supply operation and ORed to this OVL bit. Register 2 can be read to determine what fault conditions existed during the conversion. The OVL bit also facilitates a quick test to allow for an auto-ranging application, indicating to the system controller it should try reducing the PGA gain.

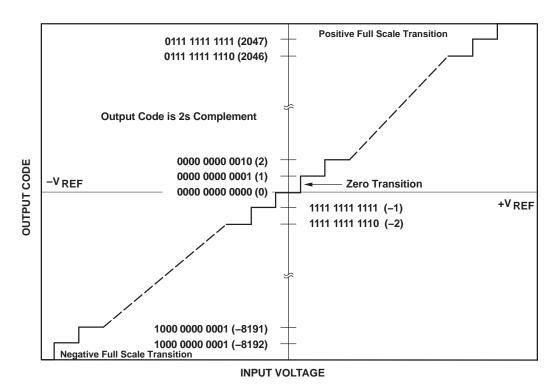

#### A/D Converter

The 12-bit A/D converter in the ADS7870 is a successive approximation type. The output of the converter is 2s complement format and can be read through the serial interface MSB first or LSB first. A plot of output codes vs input voltage is shown in Figure 13. With the input multiplexer configured for differential input, the A/D transfer function is:

$$-2048 \le \text{Code} \le 2047 \, \text{for} \, \frac{-V_{\text{REF}}}{G} \le V_{\text{IN}} \le \frac{V_{\text{REF}} - 1 \, \text{LSB}}{G}$$

(1)

With the input multiplexer configured for single-ended inputs, the A/D transfer function is:

$$0 \le \text{Code} \le 2047 \text{ for } 0 \le V_{IN} \le \frac{V_{REF} - 1 \text{ LSB}}{G}$$

(2)

Figure 13. Output Codes Versus Input Voltage

#### **Conversion Cycle**

A conversion cycle requires 48 DCLKs, where DCLK = CCLK/DF, the divided–down clock. Operation of the PGA requires 36 DCLKs: capture the input signal, auto-zero the PGA, level-shift and amplify the input signal. The period of this cycle makes certain the settling time is sufficient for gain = 20 and (source impedance of 2  $k\Omega$  or less) even if the gain is less than 20. The SAR converter takes the last 12 DCLKs.

For maximum sampling rate the input command and output data must be communicated during this cycle, although this is not recommended for best performance.

During the conversion cycle the internal capacitive load at the selected MUX input changes between 6 pF and 9.7 pF. When the ADS7870 is not converting, the MUX inputs have a nominal 4-pF load capacitance.

The source impedance of the input causes the voltage to vary on the DCLK transitions as the internal capacitors are switched in and out. A 10-nF to 100-nF capacitor across the differential inputs helps filter these glitches and act as an antialias filter in combination with the source impedance. Source impedance greater than 2 k $\Omega$  requires longer settling times and so CCLK should be reduced accordingly.

For minimum power dissipation, the bias needed for each function is turned on, allowed to settle, and run only for the duration required for each conversion. Low rate data logging applications can capitalize on this by utilizing the internal oscillator as needed rather than running a slow system clock.

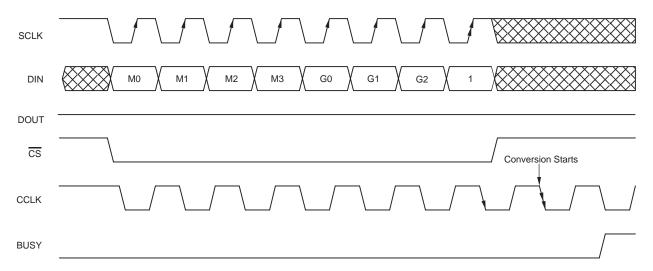

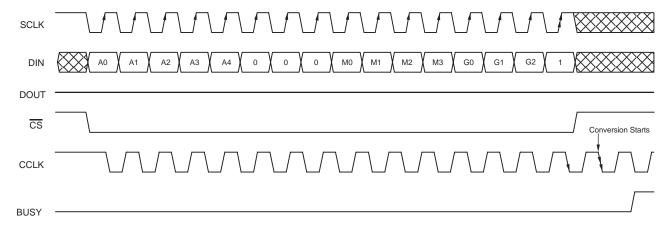

#### Starting an A/D Conversion Cycle

There are four ways to cause the ADS7870 to perform a conversion:

- 1. Send a direct mode instruction.

- 2. Write to register 4 with the CNV bit = 1

- 3. Write to register 5 with the CNV bit = 1

The next conversion queues up, waiting for the current conversion to complete

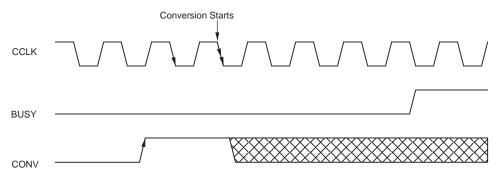

Assert the CONVERT pin (logic high) — A new conversion cycle starts at the second active edge of CCLK.

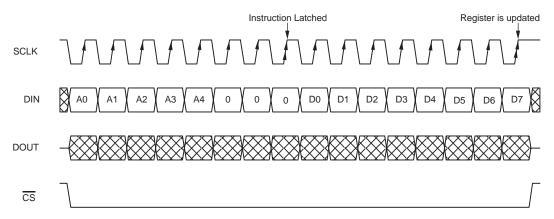

#### Serial Interface

The ADS7870 communicates with microprocessors and other external circuitry through a digital serial port interface. It is compatible with a wide variety of popular microcontrollers and digital signal processors (DSP). These include TI's TMS320, MSC1210, and MSP430 product families. Other vendors products such as Motorola 68HC11, Intel 80C51, and MicroChip PIC Series are also supported.

The serial interface consists of four primary pins, SCLK (serial bit clock), DIN (serial data input), DOUT (serial data output) and  $\overline{\text{CS}}$  (chip select). SCLK synchronizes the data transfer with each bit being transmitted on the falling or rising SCLK edge as determined by the RISE/ $\overline{\text{FALL}}$  pin. SDIN may also be used as a serial data output line.

Additional pins expand the versatility of the basic serial interface and allow it to be used with different microcontrollers. The BUSY pin indicates when a conversion is in progress and may be used to generate interrupts for the microcontroller. The CONVERT pin can be used as a hardware-based method of causing the ADS7870 to start a conversion cycle. The RESET pin can be toggled in order to reset the ADS7870 to the power-on state.

Communication through the serial interface is dependent on the microcontroller providing an instruction byte followed by either additional data (for a write operation) or just additional SCLKs to allow the ADS7870 to provide data (for a read operation). Special operating modes for reducing the instruction byte overhead for retrieving conversion results are available.

Reset of device (RESET), start of conversion (CONVERT), and oscillator enable (OSC ENABLE) can be done by signals to external pins or entries to internal registers. The actual execution of each of these commands is a logical OR function; either pin or register signal TRUE causes the function to execute. The CONVERT pin signal is an edge-triggered event, with a hold time of two CCLK periods for debounce.

### **Operating Modes**

The ADS7870 serial interface operates based on an instruction byte followed by an action commanded by the contents of that instruction. The 8-bit instruction word is clocked into the DIN input. There are two types of instruction bytes that may be written to the ADS7870 as determined by bit D7 of the instruction word (see Figure 14). These two instructions represent two different operating modes. In direct mode (bit D7 = 1), a conversion is started. A register mode (bit D7 = 0) instruction is followed by a read or write operation to the specified register.

|                                |          |     | IN   | STRUCTI | ON BYTE |    |    |    |

|--------------------------------|----------|-----|------|---------|---------|----|----|----|

|                                | D7 (MSB) | D6  | D5   | D4      | D3      | D2 | D1 | D0 |

| Start Conversion (Direct Mode) | 1        | G2  | G1   | G0      | МЗ      | M2 | M1 | M0 |

|                                |          |     |      | OR      |         |    |    |    |

| Read/Write<br>(Register Mode)  | 0        | R/W | 16/8 | A4      | А3      | A2 | A1 | A0 |

#### START CONVERSION INSTRUCTION BYTE (Direct Mode)(1)

| BIT   | SYMBOL | NAME                 | VALUE                                         | FUNCTION                                                                                                                                |

|-------|--------|----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| D7    |        | Mode select          | 1                                             | Starts a conversion cycle (direct mode)                                                                                                 |

| D6-D4 | G2–G0  | PGA gain select      | 000<br>001<br>010<br>011<br>100<br>101<br>110 | PGA Gain = 1 (power up default condition) PGA Gain = 2 PGA Gain = 4 PGA Gain = 5 PGA Gain = 8 PGA Gain = 10 PGA Gain = 16 PGA Gain = 20 |

| D3-D0 | M3-M0  | Input channel select | See Figure 21                                 | Determines input channel selection for the requested conversion, differential or single-ended configuration.                            |

<sup>(1)</sup> The seven lower bits of this byte are also written to register 4, the Gain/Mux register.

#### **READ/WRITE INSTRUCTION BYTE (Register Mode)**

| BIT   | SYMBOL  | NAME              | VALUE         | FUNCTION                                                                     |

|-------|---------|-------------------|---------------|------------------------------------------------------------------------------|

| D7    |         | Mode Select       | 0             | Initiates a read or write operation (register mode)                          |

| D6    | R/W     | Read/Write Select | 0<br>1        | Write operation Read operation                                               |

| D5    | 16/8    | Word Length       | 0<br>1        | 8-Bit word<br>16-Bit word (2 8-bit bytes)                                    |

| D4-D0 | AS4-AS0 | Register Address  | See Figure 15 | Determines the address of the register that is to be read from or written to |

Figure 14. Instruction Byte Addressing

#### **Direct Mode**

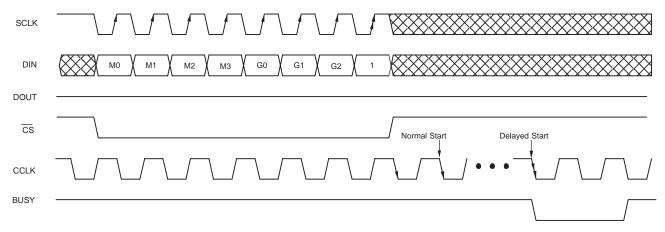

In direct mode a conversion is initiated by writing a single 8-bit instruction byte to the ADS7870 (bit D7 is set to 1). Writing the direct mode command sets the configuration of the multiplexer, selects the gain of the PGA, and starts a conversion cycle. After the last bit of the instruction byte is received, the ADS7870 performs a conversion on the selected input channel with the PGA gain set as indicated in the instruction byte.

The conversion cycle begins on the second falling edge of DCLK after the eighth active edge of SCLK of the instruction byte. When the conversion is complete, the conversion result is stored in the A/D output registers and is available to be clocked out of the serial interface by the controlling device using the READ operation in the register mode.

The structure of the instruction byte for direct mode is shown in Figure 14.

- D7: This bit is set to 1 for direct mode operation

- D6 through D4 (G2 G0): These bits control the gain of the programmable gain amplifier. PGA gains of 1, 2, 4, 5, 8, 10,16, and 20 are available. The coding is shown in Figure 14.

- D3 through D0 (M3 M0): These bits configure the switches that determine the input channel selection.

The input channels may be placed in either differential or single-ended configurations. In the case of differential configuration, the polarity of the input signal is reversible. The coding is shown in Figure 21.

Note that the seven lower bits of this byte are written to register 4, the Gain/Mux register.

All other controllable ADS7870 parameters are values previously stored in their respective registers. These values are either the power-up default values (0) or values that were previously written to one of the control registers in a register mode operation. No additional data is required for a direct mode instruction.

#### Register Mode

In register mode (Bit D7 of the Instruction Byte is 0) a read or write instruction to one of the ADS7870's registers is initiated. All of the user determinable functions and features of the ADS7870 can be controlled by writing information to these registers (see Figure 15). Conversion results can be read from the A/D Output registers.

|    | REGIST | ER AD | DRESS | 6  |             |                |             |       | F    | EGISTER | CONTEN | Т    |       |      |                                      |

|----|--------|-------|-------|----|-------------|----------------|-------------|-------|------|---------|--------|------|-------|------|--------------------------------------|

| A4 | А3     | A2    | A1    | A0 | ADDR<br>NO. | READ/<br>WRITE | D7<br>(MSB) | D6    | D5   | D4      | D3     | D2   | D1    | D0   | REGISTER NAME                        |

| 0  | 0      | 0     | 0     | 0  | 0           | Read           | ADC3        | ADC2  | ADC1 | ADC0    | 0      | 0    | 0     | OVR  | A/D Output Data,<br>LS Byte          |

| 0  | 0      | 0     | 0     | 1  | 1           | Read           | ADC11       | ADC10 | ADC9 | ADC8    | ADC7   | ADC6 | ADC5  | ADC4 | A/D Output Data,<br>MS Byte          |

| 0  | 0      | 0     | 1     | 0  | 2           | Read           | 0           | 0     | VLD5 | VLD4    | VLD3   | VLD2 | VLD1  | VLD0 | PGA Valid Register                   |

| 0  | 0      | 0     | 1     | 1  | 3           | R/W            | 0           | 0     | BIN  | 0       | RMB1   | RBM0 | CFD1  | CFD0 | A/D Control Register                 |

| 0  | 0      | 1     | 0     | 0  | 4           | R/W            | CNV/<br>BSY | G2    | G1   | G0      | М3     | M2   | M1    | MO   | Gain/Mux Register                    |

| 0  | 0      | 1     | 0     | 1  | 5           | R/W            | CNV/<br>BSY | 0     | 0    | 0       | IO3    | IO2  | IO1   | IO0  | Digital I/O State<br>Register        |

| 0  | 0      | 1     | 1     | 0  | 6           | R/W            | 0           | 0     | 0    | 0       | OE3    | OE2  | OE1   | OE0  | Digital I/O Control<br>Register      |

| 0  | 0      | 1     | 1     | 1  | 7           | R/W            | 0           | 0     | OSCR | OSCE    | REFE   | BUFE | R2V   | RBG  | Ref/Oscillator<br>Control Register   |

| 1  | 1      | 0     | 0     | 0  | 24          | R/W            | LSB         | 2W/3W | 8051 | 0       | 0      | 8501 | 2W/3W | LSB  | Serial Interface<br>Control Register |

| 1  | 1      | 1     | 1     | 1  | 31          | Read           | 0           | 0     | 0    | 0       | 0      | 0    | 0     | 1    | ID Register                          |

Figure 15. Register Address Map

The instruction byte (see Figure 14) contains the address of the register for the next read/write operation, determines whether the serial communication is to be done in 8-bit or 16-bit word length, and determines whether the next operation is read-from or written-to the addressed register.

The structure of the instruction byte for register mode is shown in Figure 14.

- D7: This bit is set to 0 for register mode operation.

- D6 (R/W): Bit 6 of the instruction byte determines whether a read or write operation is performed, 1 for a read or 0 for a write.

- D5 (16/8): This bit determines the word length of the read or write operation that follows, 1 for sixteen bits (two eight-bit bytes) or 0 for eight bits.

- D4 through D0 (A4 A0): These bits determine the address of the register that is to be read from or written to. Register address coding and other information are tabulated in Figure 15.

For sixteen-bit operations, the first eight bits is written-to/read-from the address encoded by the instruction byte, bits A4 through A0 (register address). The address of the next eight bits depends upon whether the register address for the first byte is odd or even. If it is even, then the address for the second byte is the register address + 1. If the register address is odd, then the address for the second byte is the register address – 1.

This arrangement allows transfer of conversion results from the two A/D Output Data registers either MS byte first or LS byte first (refer to the section Serial Interface Control Register).

#### Register Summary

A summary of information about the addressable registers is shown in Figure 15. Their descriptions follow, and more detailed information is provided later in the section Internal User-Accessible Registers.

Registers 0 and 1, the A/D Output Data registers, contain the least significant and most significant bits of the A/D conversion result (ADC0 through ADC13). Register 0 also has three fixed zeros (D3, D2, and D1), and a bit to indicate if the internal voltage limits of the PGA have been over ranged (OVR). This is a read only register. Write an 8-bit word to register 0 and the ADS7870 resets.

Register 2, the PGA Valid register, contains information that describes the nature of the problem in the event that the allowable input voltage to the PGA has been exceeded.

Register 3, the A/D Control register, has two test bits (best left set to zero), a bit to convert the output format to straight binary (BIN), an unused bit set to zero, two bits to configure an automatic read back mode of the A/D results (RBM1, RBM0), and two bits that program the frequency divider for the CCLK (CDF1, CDF0).

Register 4, the Gain/Mux register, contains the input channel selection information (M0 through M3) and the programmable gain amplifier gain set bits (G0 through G2).

Register 5, the Digital I/O State register, contains the state of each of the digital I/O pins (I/O3 through I/O0).

In addition, registers 4 and 5 contain a convert/busy bit (CNV/BSY) that can be used to start a conversion via a write instruction or sense when the converter is busy with a read instruction.

Register 6, the Digital I/O Control register, contains the information that determines whether each of the four digital I/O pins is to be an input or an output function (OE3 through OE0). This sets the mode of each I/O pin.

Register 7, the Ref/Oscillator Control register, controls whether the internal oscillator used for the conversion clock is on or off (OSCE), whether the internal voltage reference and buffer are on or off (REFE, BUFE), and whether the reference provides 2.5 V, 2.048 V, or 1.15 V.

Register 24, the Serial Interface Control register, controls whether data is presented MSB or LSB first (LSB bit), whether the serial interface is configured for 2-wire or 3-wire operation (2W/3W bit), and determines proper timing control for 8051-type microprocessor interfaces (8051 bit).

Register 31, the ID register, is read only.

#### Reset

There are three ways to reset.

All register contents and the serial interface are reset on:

- 1. Cycle power. The power down time must be long enough to allow internal nodes to discharge.

- 2. Toggle the RESET pin. Minimum pulse width to reset is 50 ns.

- 3. Write an 8-bit byte to register 0. The ADS7870 does not wait for the data which would normally follow this instruction.

All of these actions set all internal registers to zero, turns off the oscillator, reference, and buffer. Recovery time for the reference is dependent on capacitance on the reference and buffer outputs.

Only the serial interface is reset (and disabled) when the  $\overline{\text{CS}}$  signal is brought high. If  $\overline{\text{CS}}$  is continuously held low, and the ADS7870 is reset by an 8-bit write to register 0 (even if inadvertently) then the next 1 input to DIN is the synchronizing bit for the serial interface. The next active edge of SCLK following this 1 latches in the first bit of the new instruction byte.

For applications where  $\overline{\text{CS}}$  cannot be cycled, and system synchronization is lost, the ADS7870 must be reset by writing 39 zeros and a one. The serial interface is then ready to accept the next command byte. This string length is based on the worst case conditions to ensure that the device is synchronized.

### NOTE:

A noisy SCLK, with excessive ringing, can cause the ADS7870 to inadvertently reset. Sufficient capacitance to correct this problem may be provided by just a scope probe, which would mask this issue during debugging. A  $100-\Omega$  capacitor in series with the SCLK pin is usually sufficient to correct this problem. Since the data is changed on the opposite edge of SCLK, it is usually settled before the active edge of SCLK and would not need its own  $100-\Omega$  resistor, although it would not be detrimental.

### Write Operation

To perform a write operation an instruction byte must first be written to the ADS7870 as described previously (see Figure 14). This instruction determines the target register as well as the word length (8 bits or 16 bits). The  $\overline{CS}$  pin must be asserted (0) prior to the first active SCLK edge (rising or falling depending on the state of the RISE/FALL pin) that latches the first bit of the instruction byte. The first active edge after  $\overline{CS}$  must have the first bit of the instruction byte are latched on the next seven active edges of SCLK.  $\overline{CS}$  must remain low for the entire sequence. Setting  $\overline{CS}$  high resets the serial interface.

When starting a conversion by setting the CNV/BSY bit in the Gain/Mux register and/or the Digital I/O register, the conversion starts on the second falling edge of DCLK after the last active SCLK edge of the write operation.

Figure 16 shows an example of an eight-bit write operation with LSB first and SCLK active on the rising edge. The double arrows indicate the SCLK transition when data is latched into its destination register.

Figure 16. Timing Diagram for an 8-Bit Write Operation

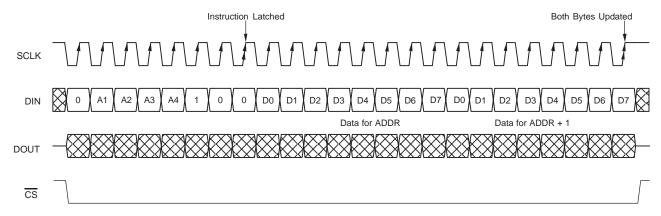

Figure 17 shows an example of the timing for a 16-bit write to an even address with LSB first and SCLK active on the rising edge. Notice that both bytes are updated to their respective registers simultaneously. Also shown is that the address (ADDR) for the write of the second byte is incremented by one since the ADDR in the instruction byte was even. For an odd ADDR, the address for the second byte would be ADDR–1.

Figure 17. Timing Diagram of a 16-Bit Write Operation to an Even Address

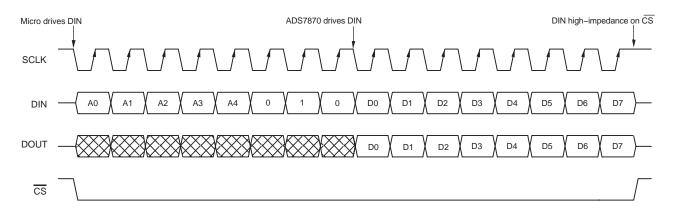

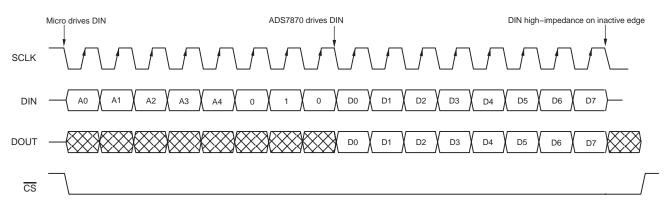

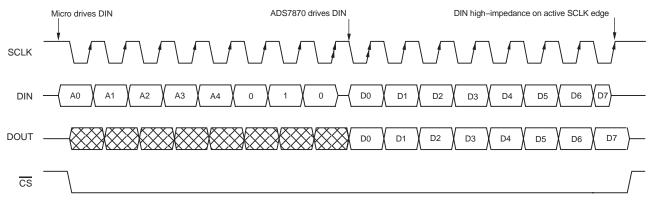

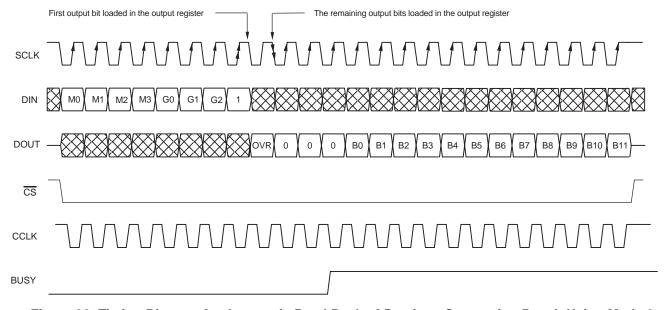

#### **Read Operation**

A read operation is similar to a write operation except that data flow (after the instruction byte) is from the ADS7870 to the host controller. After the instruction byte has been latched (on the eighth active edge of SCLK), the DOUT pin (and the DIN pin if in two-wire mode) begins driving data on the next nonactive edge of SCLK. This allows the host controller to have valid data on the next active edge of SCLK.

The data on DOUT (or DIN) transitions on the nonactive edges of SCLK. The DIN pin (two-wire mode) ceases driving data (return to high impedance) on the nonactive edge of SCLK following the eighth (or sixteenth) active edge of the read data. DOUT is only high impedance when  $\overline{CS}$  is not asserted. With  $\overline{CS}$  high (1), DOUT (or DIN) is forced to high impedance mode. In general, the ADS7870 is insensitive to the idle state of the clock except that the state of SCLK may determine if DIN is driving data or not.

Upon completion of the read operation, the ADS7870 is ready to receive the next instruction byte. Read operations reflect the state of the ADS7870 on the first active edge of SCLK of the data byte transferred.

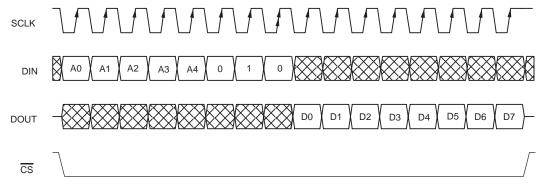

Figure 18 shows an example of an eight-bit read operation with LSB first and SCLK active on the rising edge. The double rising arrows indicate when the instruction is latched.

Figure 18. Timing Diagram for an 8-Bit Read Operation

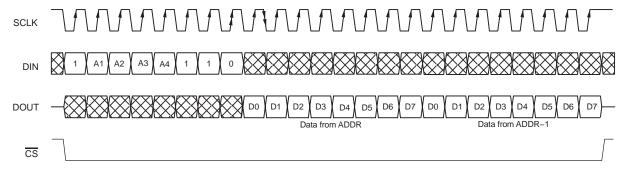

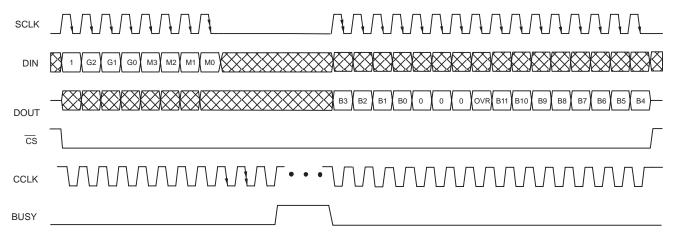

Figure 19 provides an example of a 16-bit read operation from an odd address with LSB first and SCLK active on the rising edge. The address (ADDR) for the second byte is decremented by one since the ADDR in the instruction byte is odd. For an even ADDR, the address for the second byte would be incremented by one.

Figure 19. Timing Diagram for a 16-Bit Read Operation to an Odd Address

### **Multiplexer Addressing**

The last four bits in the instruction byte (during a start conversion instruction) or the Gain/Mux register (ADDR = 4) assign the multiplexer configuration for the requested conversion. The input channels may be placed in either differential or single-ended configurations. For differential configurations, the polarity of the input signal is reversible by the state of M2 (Bit D2). In single-ended mode, all input channels are measured with respect to system ground (pin 25). Figure 20 shows some examples of multiplexer assignments and Figure 21 provides the coding for the input channel selection.

**EXAMPLES OF MULTIPLEXER OPTIONS**

#### Differential and 4 Differential Single-Ended 8 Single-Ended Channel Channel Channel LN0 LN0, LN1 LN0. LN1 LN1 LN2 LN2, LN3 LN2, LN3 LN3 IN4 LN4 LN4, LN5 LN<sub>5</sub> LN5 LN6 LN6 LN6, LN7 LN7 LN7

Figure 20. Examples of Multiplexer Options

| CODING FOR DIFFERENTIAL INPUT CHANNEL SELECT |                            |    |    |     |     |     |     | -   |     | CODII          | NG FC | _  | NGLE-<br>negati |    |       | -     |     | IEL S | ELEC | Г   |     |     |     |

|----------------------------------------------|----------------------------|----|----|-----|-----|-----|-----|-----|-----|----------------|-------|----|-----------------|----|-------|-------|-----|-------|------|-----|-----|-----|-----|

| S                                            | SELECTION BITS INPUT LINES |    |    |     |     |     |     |     | 5   | SELECTION BITS |       |    |                 |    | INPUT | LINES |     |       |      |     |     |     |     |

| М3                                           | M2                         | M1 | MO | LN0 | LN1 | LN2 | LN3 | LN4 | LN5 | LN6            | LN7   | М3 | M2              | M1 | МО    | LN0   | NL1 | LN2   | LN3  | LN4 | LN5 | LN6 | LN7 |

| 0                                            | 0                          | 0  | 0  | +   | -   |     |     |     |     |                |       | 1  | 0               | 0  | 0     | +     |     |       |      |     |     |     |     |

| 0                                            | 0                          | 0  | 1  |     |     | +   | -   |     |     |                |       | 1  | 0               | 0  | 1     |       | +   |       |      |     |     |     |     |

| 0                                            | 0                          | 1  | 0  |     |     |     |     | +   | -   |                |       | 1  | 0               | 1  | 0     |       |     | +     |      |     |     |     |     |

| 0                                            | 0                          | 1  | 1  |     |     |     |     |     |     | +              | -     | 1  | 0               | 1  | 1     |       |     |       | +    |     |     |     |     |

| 0                                            | 1                          | 0  | 0  | -   | +   |     |     |     |     |                |       | 1  | 1               | 0  | 0     |       |     |       |      | +   |     |     |     |

| 0                                            | 1                          | 0  | 1  |     |     | -   | +   |     |     |                |       | 1  | 1               | 0  | 1     |       |     |       |      |     | +   |     |     |

| 0                                            | 1                          | 1  | 0  |     |     |     |     | -   | +   |                |       | 1  | 1               | 1  | 0     |       |     |       |      |     |     | +   |     |

| 0                                            | 1                          | 1  | 1  |     |     |     |     |     |     | -              | +     | 1  | 1               | 1  | 1     |       |     |       |      |     |     |     | +   |

NOTE: Bit M3 selects either differential or single-ended mode. If differential mode is selected, bit M2 determines the polarity of the input channels. Bold items are power-up default conditions.

Figure 21. Multiplexer Addressing

### INTERNAL USER-ACCESSIBLE REGISTERS

The registers in the ADS7870 are eight bits wide. Most of the registers are reserved, the ten user-accessible registers are summarized in the register address map (see Figure 15). Detailed information for each register follows. The default power-on/reset state of all bits in the registers is 0.

### **ADC Output Registers**

The A/D output registers are read only registers located at ADDR = 0 and ADDR = 1 that contain the results of the A/D conversion, ADC11 through ADC0 (see Figure 22). The conversion result is in 2s complement format. The bits can be taken out of the registers MSB (D7) first or LSB (D0) first, as determined by the state of the LSB bits (D7 or D0) in the Serial Interface Control register. The ADDR = 0 register also contains the OVR bit which indicates if the internal voltage limits to the PGA have been exceeded.

#### **ADC OUTPUT REGISTERS**

| ADDR | D7 (MSB) | D6    | D5   | D4   | D3   | D2   | D1   | D0   |

|------|----------|-------|------|------|------|------|------|------|

| 0    | ADC3     | ADC2  | ADC1 | ADC0 | 0    | 0    | 0    | OVR  |

| 1    | ADC11    | ADC10 | ADC9 | ADC8 | ADC7 | ADC6 | ADC5 | ADC4 |

### ADDR = 0 (LS Byte)

| BIT   | SYMBOL        | NAME           | VALUE | FUNCTION                                                                                                                                                                                         |

|-------|---------------|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-D4 | ADC3-<br>ADC0 | A/D Output     | (1)   | Four least significant bits of conversion result                                                                                                                                                 |

| D3-D1 | _             | _              | 0     | These bits are not used and are always 0.                                                                                                                                                        |

| D0    | OVR           | PGA Over-Range | 0     | Valid conversion result An analog over-range problem has occurred in the PGA. Conversion result may be invalid. Details of the type of problem are stored in register 2, the PGA Valid register. |

# ADDR = 1 (MS Byte)

| BIT   | SYMBOL         | NAME       | VALUE | FUNCTION                                         |

|-------|----------------|------------|-------|--------------------------------------------------|

| D7-D0 | ADC11-<br>ADC4 | ADC Output | (1)   | Eight most significant bits of conversion result |

<sup>(1)</sup> Value depends on conversion result.

Figure 22. ADC Output Registers (ADDR = 0 and ADDR = 1)

# **PGA Valid Register**

The PGA Valid register (ADDR = 2) is a read only register that contains the individual results of each of the six comparators for the PGA, VLD5 through VLD0, as shown in Figure 23.

#### **PGA VALID REGISTER**

| ADDR | D7 (MSB) | D6 | D5   | D4   | D3   | D2   | D1   | D0   |

|------|----------|----|------|------|------|------|------|------|

| 2    | 0        | 0  | VLD5 | VLD4 | VLD3 | VLD2 | VLD1 | VLD0 |

#### ADDR = 2

| BIT   | SYMBOL | NAME        | VALUE         | FUNCTION                                                                                                                                                                            |

|-------|--------|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-D6 | _      |             | 0             | These bits are not used and are always 0.                                                                                                                                           |

| D5    | VLD5   | PGA Valid 5 | <b>0</b><br>1 | <ul> <li>0 - Voltage at minus (-) output from the PGA is within its minimum value.</li> <li>1 - Voltage at minus (-) output from the PGA has exceeded its minimum value.</li> </ul> |

| D4    | VLD4   | PGA Valid 4 | <b>0</b><br>1 | 0 – Voltage at minus (–) output from the PGA is within its maximum value.  1 – Voltage at minus (–) output from the PGA has exceeded its maximum value.                             |

| D3    | VLD3   | PGA Valid 3 | <b>0</b><br>1 | 0 – Voltage at minus (–) input to the PGA is within its maximum value.  1 – Voltage at minus (–) input to the PGA has exceeded its maximum value.                                   |

| D2    | VLD2   | PGA Valid 2 | <b>0</b><br>1 | 0 – Voltage at plus (+) output from the PGA is within its minimum value.  1 – Voltage at plus (+) output from the PGA has exceeded its minimum value.                               |

| D1    | VLD1   | PGA Valid 1 | <b>0</b><br>1 | 0 – Voltage at plus (+) output from the PGA is within its maximum value. 1 – Voltage at plus (+) output from the PGA has exceeded its maximum value.                                |

| D0    | VLD0   | PGA Valid 0 | <b>0</b><br>1 | 0 – Voltage at plus (+) input to the PGA is within its maximum value.  1 – Voltage at plus (+) input to the PGA has exceeded its maximum value.                                     |

**Bold** items are power-up default conditions.

Figure 23. PGA Valid Register (ADDR = 2)

### A/D Control Register

The A/D Control register (ADDR = 3) configures the CCLK divider and read back mode option as shown in Figure 24.

#### **ADC CONTROL REGISTER**