# PLL frequency synthesizer for tuners **BU2622S**

The BU2622S is a PLL frequency synthesizer IC designed for use in high-fidelity audio systems, car stereos, and CD radio cassettes. Featuring low power consumption, low superfluous radiation, a frequency measurement counter, and timer output, this chip is ideal for high-performance systems.

#### Applications

Mini components, car stereos, radio cassettes, receivers, and other frequency generating devices

#### ●Features

- Built-in high-speed prescaler can divide 130MHz

VCO

- 2) Low power-consumption (during operation : 6.0mA PLL OFF 300  $\mu$ A Typ.)

- 3) Seven standard frequencies: 50kHz, 25kHz, 12.5kHz, 10kHz, 9kHz, 5kHz, and 1kHz.

- 4) Counter for intermediate frequency detection.

- 5) Unlock detection circuit.

- 6) Six output ports.

- 7) SD input.

- 8) Timer output.

- 9) Serial data input (CE.CK.DA)

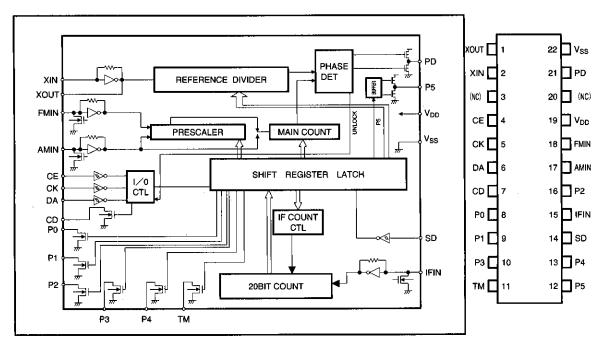

#### Block diagram

# ●Absolute maximum ratings (Ta = 25°C)

| Parameter                | Symbol            | Limits                    | Unit | Conditions                 |

|--------------------------|-------------------|---------------------------|------|----------------------------|

| Supply voltage           | V <sub>DD</sub>   | -0.3~7.0                  | V    | V <sub>DD</sub>            |

| Maximum input voltage 1  | Vini              | -0.3~7.0                  | ٧    | CE, CK, DA, SD             |

| Maximum input voltage 2  | V <sub>IN2</sub>  | -0.3~V <sub>DD</sub> +0.3 | V    | XIN, FMIN, AMIN, IFIN      |

| Maximum output voltage 1 | V <sub>OUT1</sub> | -0.3~10.0                 | V    | Po, P1, P2, P3, P4, TM, CD |

| Maximum output voltage 2 | V <sub>OUT2</sub> | -0.3~V <sub>00</sub> +0.3 | V    | PD, P <sub>5</sub> , XOUT  |

| Maximum output current   | Гоит              | 0~4.0                     | mA   | Po, P1, P2, P3, P4, TM, CD |

| Power dissipation        | Pd                | 450*                      | mW   |                            |

| Operating temperature    | Topr              | -25~75                    | Ç    |                            |

| Storage temperature      | Tstg              | <b>−55∼125</b>            | ొ    |                            |

<sup>\*</sup> When used with Ta at greater than 25 degrees Celsius, derate the power by 4.5 mW for every degree above 25 degrees.

# ● Recommended operating conditions (Ta = 25°C)

| Parameter      | Symbol            | Min. | Тур. | Мах. | Unit |

|----------------|-------------------|------|------|------|------|

| Supply voltage | V <sub>DD</sub> 1 | 4.0  | _    | 6.0  | V    |

### Explanation of terminals

| Pin No. | Symbol          | Terminal name           | Function                                                                                                  | 1/0            |

|---------|-----------------|-------------------------|-----------------------------------------------------------------------------------------------------------|----------------|

| 1       | XOUT            | Crystal oscillation     | For generation of standard frequency and internal clock.                                                  | OUT            |

| 2       | XIN             | terminal                | Connected to 7.2 MHz crystal oscillator.                                                                  | IN             |

| 3       | NC              | Unused terminal         | Not related to the circuits.                                                                              | :              |

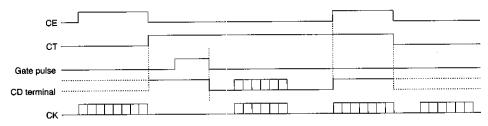

| 4       | CE              | Chip enable             | When CE is H, DA is synchronous with the rise of CK and                                                   |                |

| 5       | CK              | Clock signal            | read to the internal shift register. DA is then latched at the                                            | IN             |

| 6       | DA              | Serial data             | timing of the fall of CE. Also, output data is output from the CD terminal synchronous to the rise of CK. |                |

| 7       | CD              | Count data              | Frequency data and unlock data are output.                                                                |                |

| 8       | P0              |                         |                                                                                                           | ]              |

| 9       | P1              | Output port             | Controlled on the basis of input data.                                                                    | Nch open drain |

| 10      | - P3            | _                       |                                                                                                           |                |

| 11      | TM              | Timer output            |                                                                                                           |                |

| 12      | P5              | Outside                 | Controlled on the book of legat date                                                                      | CMOS/3-state   |

| 13      | P4              | Output port             | Controlled on the basis of input data.                                                                    | Nch open drain |

| 14      | SD              | Input port              |                                                                                                           | IN             |

| 15      | IFIN            | IF input                | Intermediate frequency input                                                                              | IN             |

| 16      | P2              | Output port             | Controlled on the basis of input data.                                                                    | Nch open drai  |

| 17      | AMIN            | AM input                | Local input for AM                                                                                        | IN             |

| 18      | FMIN            | FM input                | Local input for FM                                                                                        | IN             |

| 19      | V <sub>DD</sub> | Power supply            | Power supply, with 4.0V to 6.0V applied voltage.                                                          |                |

| 20      | NC              | Unused terminal         | Not related to circuits.                                                                                  |                |

| 21      | PD              | Phase comparison output | High level when value obtained by dividing local output is                                                | 3-state        |

| 22      | Vss             | GROUND                  | higher than standard frequency. Low level when value is lower. High impedance when value is same.         |                |

ullet Electrical characteristics (unless other specified, Ta = 25  $^{\circ}$ C, V<sub>DD</sub> = 5.0V)

| Parameter                    | Symbol            | Min.                   | Тур.                      | Max.     | Unit | Conditions                       | s                                 |

|------------------------------|-------------------|------------------------|---------------------------|----------|------|----------------------------------|-----------------------------------|

| Supply current 1             | I <sub>DD1</sub>  | =                      | 6.0                       | 10.0     | mA   | FM <sub>IN</sub> =130MHz, 100mVi | rms                               |

| Supply current 2             | lpD2              | _                      | 0.3                       | 1.0      | mA   | No input,, PLL=OFF               |                                   |

| Quiescent circuit current    | V <sub>IH</sub>   | 4.0                    | _                         | _        | V    | CE, CK, DA, SD                   |                                   |

| "H" level input voltage      | Vı∟               | <del></del>            | _                         | 1.0      | V    | CE, CK, DA, SD                   |                                   |

| "L" level input voltage      | 11111             |                        | _                         | 1.0      | μΑ   | CE, CK, DA, SD                   | V <sub>IN</sub> =V <sub>DD</sub>  |

| "H" level input current 1    | I <sub>iH2</sub>  | _                      | 0.3                       |          | μΑ   | XIN                              | V <sub>IN</sub> =V <sub>DD</sub>  |

| "H" level input current 2    | 1 <sub>IH3</sub>  | _                      | 6.0                       | _        | μΑ   | FMIN, AMIN, IFIN                 | V <sub>IN</sub> =V <sub>DD</sub>  |

| "H" level input current 3    | l <sub>IL1</sub>  | -1.0                   | _                         |          | μΑ   | CE, CK, DA, SD                   | V <sub>IN</sub> =V <sub>SS</sub>  |

| "L" level input current 1    | l <sub>IL2</sub>  | _                      | -0.3                      | _        | μA   | XIN                              | V <sub>IN</sub> =V <sub>SS</sub>  |

| "L" level input current 2    | lııs              | _                      | -6.0                      | _        | μA   | FMIN, AMIN, IFIN                 | V <sub>IN</sub> =V <sub>SS</sub>  |

| "L" level input current 3    | V <sub>OL1</sub>  |                        | 0.2                       | 0.5      | V    | Po, P1, P2, P3, P4, TM, CD       | l <sub>0</sub> =1.0mA             |

| "L" level output voltage 1   | l <sub>OFF1</sub> | _                      | _                         | 1.0      | μΑ   | Po, P1, P2, P3, P4, TM, CD       | V <sub>0</sub> =10V               |

| "OFF" level leak current 1   | V <sub>OL2</sub>  | _                      | _                         | 0.3      | V    | FMIN, AMIN, IFIN                 | lo∪т≕0.1mA                        |

| "L" level output voltage 2   | VoH               | V <sub>DD</sub><br>1.0 | V <sub>DD</sub> —<br>0.25 | _        | V    | PD, P <sub>5</sub>               | l <sub>OUT</sub> =-1.0mA          |

| "H" level output voltage     | V <sub>OL4</sub>  | _                      | 0.15                      | 1.0      | V    | PD, P <sub>5</sub>               | lout=1.0mA                        |

| "L" level output voltage     | loff2             |                        | _                         | 100      | nA   | PD                               | V <sub>OUT</sub> =V <sub>DD</sub> |

| "OFF" level leak current 2   | l <sub>OFF3</sub> | -100                   |                           | _        | nA   | PD                               | V <sub>OUT</sub> =V <sub>SS</sub> |

| "OFF" level leak current 3   | R <sub>F1</sub>   |                        | 10                        |          | МΩ   | XIN                              |                                   |

| Internal feedback resistor 1 | R <sub>F2</sub>   |                        | 500                       | <u> </u> | kΩ   | FMIN, AMIN, IFIN                 |                                   |

| Internal feedback resistor 2 | FiNt              | _                      | 7.2                       | _        | MHz  | XIN, sine wave, C coupling       |                                   |

| Input frequency 1            | F <sub>IN2</sub>  | 10                     | _                         | 130      | MHz  | FMIN,sine wave,C coupling        | V <sub>IN</sub> ≕50mVrms          |

| Input frequency 2            | F <sub>IN3</sub>  | 0.5                    | _                         | 30       | MHz  | AMIN,sine wave,C coupling        | V <sub>IN</sub> =70mVrms          |

| Input frequency 3            | F <sub>IN4</sub>  | 0.5                    | _                         | 15       | MHz  | AMIF,sine wave,C coupling        | V <sub>IN</sub> =50mVrms          |

| Input frequency 4            | F <sub>IN5</sub>  | 0.4                    |                           | 16       | MHz  | IFIN,sine wave,C coupling        | V <sub>IN</sub> =70mVrms          |

| Maximum input amplitude      | FINMAX            | -                      | _                         | 1.5      | Vrms | XIN,FMIN,AMIN,IFIN,sine wa       | ve,C coupling                     |

| Minimum pulse width          | TW                |                        | 1.0                       | _        | μs   | CK, DA                           | <del></del>                       |

| Input rise time              | TR                | _                      | _                         | 500      | ns   | CE, CK, DA                       |                                   |

| Input fall time              | TF                |                        |                           | 500      | ns   | CE, CK, DA                       |                                   |

O Not designed for radiation resistance.

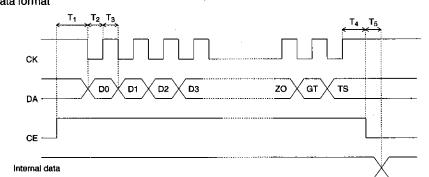

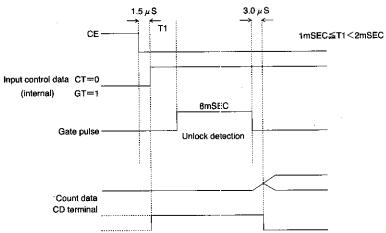

$T_1 \ge 1.5 \,\mu\,\text{SEC}$

$T_2,T_3>0~\mu~SEC$

T<sub>4</sub>>0 μ SEC

$T_5 > 1.5 \,\mu\,\text{SEC}$

\* : (0) is input.

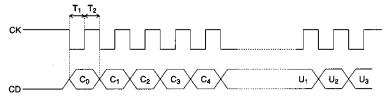

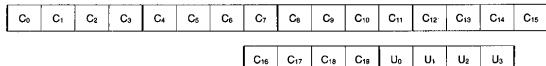

## Output data format CE output is set to LO.

Figures for output assume the presence of pullup resistance.  $T_1,T_2>1~\mu\,{\rm SEC}$  Output data format

← Input done from Co.

Explanation of the data

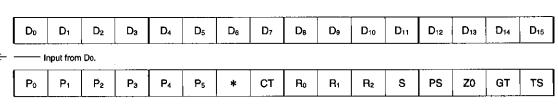

( 1 ) Division data : For  $D_0$  through  $D_{15}$  (When  $S\,=\,1,$  use  $D_4$  through  $D_{15.})$

| D₀     | D <sub>1</sub> | D <sub>2</sub> | D₃      | D₄     | Ð₅      | D <sub>6</sub> | D <sub>7</sub> | D₃ | D <sub>9</sub> | D <sub>10</sub> | D <sub>11</sub> | D <sub>12</sub> | D <sub>13</sub> | D <sub>14</sub> | D <sub>15</sub> |  |

|--------|----------------|----------------|---------|--------|---------|----------------|----------------|----|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|

| Exam   | oles:          |                |         |        |         |                |                |    |                |                 |                 |                 |                 |                 |                 |  |

| Divide | d frequ        | ency =         | 1106 (D | )) ÷2= | 553 (D) | ==229          | (H) S=         | 0  |                |                 |                 |                 |                 |                 |                 |  |

| 1      | 0              | 0              | 1       | 0      | 1       | 0              | 0              | 0  | 1              | 0               | 0               | 0               | 0               | 0               | 0               |  |

| Divide | d frequ        | ency =         | 1107 (D | ) =453 | 3 (H)   | s=             | 1, PS          | =1 |                |                 |                 |                 |                 |                 |                 |  |

| 1      | 1              | 0              | 0       | 1      | 0       | 1              | 0              | 0  | 0              | 1               | 0               | 0               | 0               | 0               | 0               |  |

| Divide | d frequ        | ency = 1       | 926 (D) | =39E   | (H)     | S=1            | , PS=          | 0  |                |                 |                 |                 |                 |                 |                 |  |

| ×      | ×              | ×              | ×       | 0      | 1       | 1              | 1              | 1  | 0              | 0               | 1               | 1               | 1               | 0               | 0               |  |

- (2) CT: Frequency measurement beginning data

- 1: Begins measurement.

- 0 : Resets internal counter, IFIN goes to pull-down.

- (3) Output port control data: Po, P1, P2, P3, P4, P5

- 1: Open drain output ON

- (P5 is LO)

- 2: Open drain output OFF (P5 is HI)

- (4) Z0: Ps is set to high impedance.

- (5) Ro, R1, R2, standard frequency data

|     | Data           |                | Standard frequency |

|-----|----------------|----------------|--------------------|

| R₀  | R <sub>1</sub> | R <sub>2</sub> |                    |

| 0   | 0              | 0              | 25kHz              |

| 0   | 0              | 1              | 12.5kHz            |

| 0   | 1              | 0              | 50kHz              |

| 0   | 1              | 1              | 10kHz              |

| 1   | 0              | 0              | 5kHz               |

| 1   | 0              | 1              | 9kHz               |

| _ 1 | 1              | 0              | 1kHz               |

| 1   | 1              | 1              | * PLL OFF          |

- \* FMIN = pulldown, AMIN = pulldown, PD = high impedance

- (6) S: switch between FMIN and AMIN

- 0:FMIN

- 1: AMIN

- (7) PS: If this bit is set to ON while AMIN is selected, swallow counter division is possible.

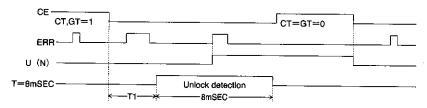

# (8) GT: Frequency measurement time and unlock detection ON/OFF

| СТ | GT. | GT Frequency measurement Unlock |     | Dața output |

|----|-----|---------------------------------|-----|-------------|

| 0  | 0   | OFF                             | OFF | NG          |

| 0  | 1   | OFF                             | ON  | ·           |

| 1  | 0   | ON Gate time = 8 mSEC           | ON  | OK          |

| 1  | 1   | ON Gate time = 16 mSEC          | ON  |             |

(9) TS: Test data

(0) is input

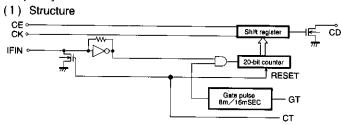

#### Frequency counter

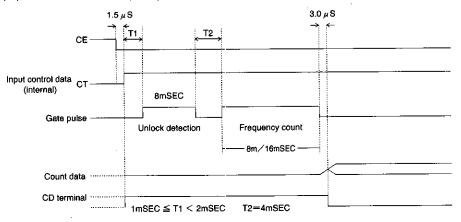

(2) How the frequency counter operates When control data CT equals 1, the 20-bit counter and the amp go into operation. When CT equals 0, amp input goes to pulldown and the counter is reset. Measuring time (gate pulse) is selected (8mSEC/16mSEC) on the basis of control data GT. When control data CT equals 0, the counter is reset.

# (3) Explanation of output data Co: LSB C10: MSB

Unlock detection

When control data GT equals 1, or CT equals 1, the unlock detection circuit goes into operation for 8mSEC. When CT equals 1, the unlock detection circuits stops operating before the frequency counter gate pulse is emitted. When CT equals 0, or GT equals 0, the unlock detection circuit is reset.

1mSEC≨T1<2mSEC

# Explanation of the output data

U0 U1 U2 U3 0 0 0 **ERR** < 1.1  $\mu$  SEC 0 0  $1.1 \,\mu\,\mathrm{SEC}$  < ERR 2.2 µ SEC 2.2 μ SEC < **ERR** < 3.3 μ SEC  $3.3 \,\mu\,\mathrm{SEC}$  < ERR < 4.4 μ SEC 1 1  $4.4 \mu$ SEC < **ERR**

Frequency counter and unlock detection

(1) When CT = 1: Frequency count and unlock detection are carried out.

(2) When CT = 0 and GT = 1: Only unlock detection is carried out.

Explanation of CD terminal

While frequency measurement or unlock detection is in progress, the CD terminal goes to HI. When either of these operations finishes, it goes to LO. When the control data is such that CT == 0 and GT = 0, the SD terminal input is displayed in reverse video.

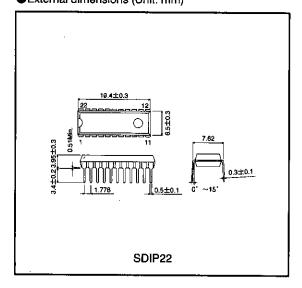

●External dimensions (Unit: mm)

#### **Notes**

- The contents described in this catalogue are correct as of March 1997.

- No unauthorized transmission or reproduction of this book, either in whole or in part, is permitted.

- The contents of this book are subject to change without notice. Always verify before use that the contents are the latest specifications. If, by any chance, a defect should arise in the equipment as a result of use without verification of the specifications, ROHM CO., LTD., can bear no responsibility whatsoever.

- Application circuit diagrams and circuit constants contained in this data book are shown as examples of standard use and operation. When designing for mass production, please pay careful attention to peripheral conditions.

- Any and all data, including, but not limited to application circuit diagrams, information, and various data, described in this catalogue are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO., LTD., disclaims any warranty that any use of such device shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes absolutely no liability in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices; other than for the buyer's right to use such devices

itself, resell or otherwise dispose of the same; no express or implied right or license to

practice or commercially exploit any intellectual property rights or other proprietary rights

owned or controlled by ROHM CO., LTD., is granted to any such buyer.

- The products in this manual are manufactured with silicon as the main material.

- The products in this manual are not of radiation resistant design.

The products listed in this catalogue are designed to be used with ordinary electronic equipment or devices (such as audio-visual equipment, office-automation equipment, communications devices, electrical appliances, and electronic toys). Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers, or other safety devices) please be sure to consult with our sales representatives in advance.

#### Notes when exporting

- It is essential to obtain export permission when exporting any of the above products when it falls under the category of strategic material (or labor) as determined by foreign exchange or foreign trade control laws.

- Please be sure to consult with our sales representatives to ascertain whether any product is classified as a strategic material.