# Servo Signal Processors for CD BU9317K/BU9317KS

The BU9317K and BU9317KS, both single-chip ICs with a double-speed adjustment-free PLL circuit, program servo and signal processing block, are servo signal processors for CD players and are designed for low voltage and low power consumption. These ICs are ideal for compact, low-power-consumption applications.

### Applications

Portable CD players, radio-cassette recorders, mini and component stereos

### Features

- Internal PLL circuit and bit clock sampling with a minimal number of attached components, for EFM data modulation.

- Detects and protects frame synchronization signals.

- Internal servo filters for focusing, tracking and threading. Characteristics are controlled by commands from the controller.

- 4) Serial output pins for subcodes.

- 5) Separate output pins for P codes and Q codes.

- Internal CLV sequencer that automatically sets the CLV mode.

- Internal track jump sequencer, for jumping to the desired track.

- 8) Combines the track jump path with tracking error components for output.

- A single chip with an internal deinterleaving function and channel 1/channel 2 double error detection, correction and flagging processor.

- Signals to DAC devices are output MSB first through SCOMP serial output, for control of interpolation circuit ON/OFF operations for CD-ROM devices.

- 11) Internal 16-Kbit SRAM absorbs jitter of up to  $\pm 4$  frames.

- 12) Double speed playback.

# ●Absolute maximum ratings (Ta=25℃)

| Parameter Power supply voltage |          | Symbol | Limits        | Unit |

|--------------------------------|----------|--------|---------------|------|

|                                |          | Vcc    | 7             | V    |

| Power dissipation              | BU9317K  | D-1    | 900 * 1       | mW   |

|                                | BU9317KS | Pd     | 800 *2        |      |

| Operating temperature          |          | Topr   | <b>-25~75</b> | c    |

| Storage temperature            |          | Tstg   | -55~125       | °C   |

<sup>\*1.</sup> Reduced by 9.0 mW for each increase in Ta of 1.°C over 25°C.

# ●Recommended operating conditions (Ta=25℃)

| Parameter            | Symbol | Min. | Тур. | Max. | Unit |  |

|----------------------|--------|------|------|------|------|--|

| Power supply voltage | Vcc    | 3.0  |      | 5.5  | V    |  |

<sup>\*2.</sup> Reduced by 8.0 mW for each increase in Ta of 1°C over 25°C.

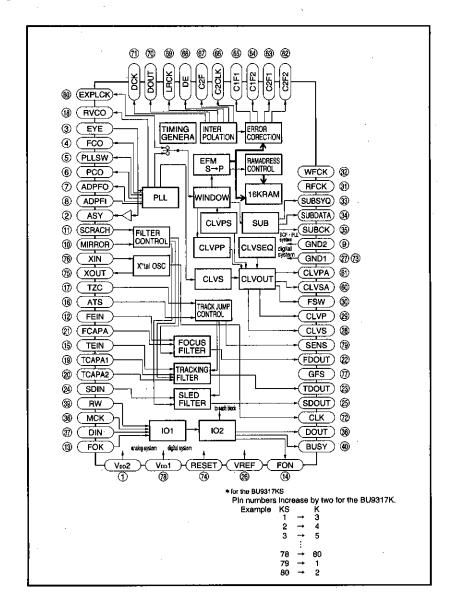

Block diagram

# Pin description

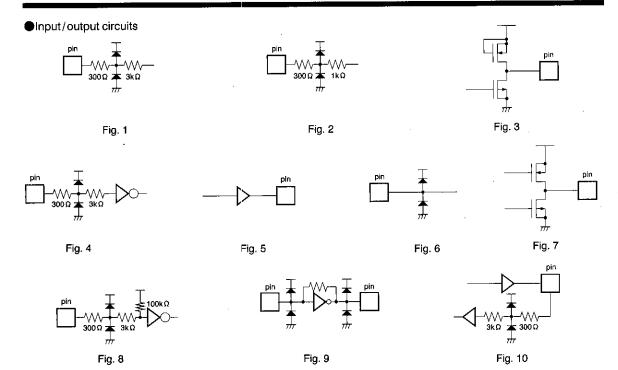

| Pin No. | Pin name | Analog/<br>digital | 1/0 | Function                                                                    | input/output<br>cicuit diagram |

|---------|----------|--------------------|-----|-----------------------------------------------------------------------------|--------------------------------|

| 1 (3)   | Voo2     |                    |     | PLL servo filter block power supply                                         |                                |

| 2 (4)   | ASY      | Digital            | 0   | Output for EFM signal slice level control                                   | Fig.5                          |

| 3 (5)   | EYE      | Digital            | ı   | Input of EFM signals from the RF amplifier                                  | Fig.4                          |

| 4 (6)   | FCO      | Analog             | 0   | Output of PLL frequency comparison error voltage                            | Fig.7                          |

| 5 (7)   | PLLSW    | Digital            | 0   | PLL time constant switching                                                 | Fig.3                          |

| 6 (8)   | PCO      | Analog             | 0   | Output of PLL phase comparison error voltage                                | Fig.7                          |

| 7 (9)   | ADPFO    | Analog             | 0   | PLL adding amplifier output                                                 | Fig.2                          |

| 8 (10)  | ADPFI    | Analog             | 1   | PLL adding amplifier inverted input                                         | Fig.1                          |

| 9 (11)  | GND2     |                    |     | PLL servo filter block ground                                               |                                |

| 10 (12) | MIRROR   | Digital            | 1   | Miller signal input                                                         | Fig.4                          |

| 11 (13) | SCRACH   | Digital            | 1   | Scratch signal input                                                        | Fig.4                          |

| 12 (14) | FEIN     | Analog             | ı   | Focus error signal input                                                    | Fig.1                          |

| 13 (15) | FOK      | Digital            | ı   | Focus OK signal input                                                       | Fig.4                          |

| 14 (16) | FON      | Digital            | 0   | Focus ON signal output                                                      | Fig.5                          |

| 15 (17) | TEIN     | Analog             | ı   | Tracking error signal input                                                 | Fig.1                          |

| 16 (18) | ATS      | Analog             | I   | Anti-shock detection window comparator input                                | Fig.1                          |

| 17 (19) | TZC      | Analog             | 1   | Tracking zero cross comparator input                                        | Fig.1                          |

| 18 (20) | RVCO     | Analog             | 0   | PLL VCO free running resistor                                               | Fig.2                          |

| 19 (21) | TCAPA1   | Analog             | 1/0 | Connecting the tracking servo filter capacitor                              | Fig.6                          |

| 20 (22) | TCAPA2   | Analog             | 1/0 | Connecting the tracking servo filter capacitor                              | Fig.6                          |

| 21 (23) | FCAPA    | Analog             | 1/0 | Connecting the focus servo filter capacitor                                 | Fig.6                          |

| 22 (24) | FDOUT    | Analog             | 0   | Focus drive output                                                          | Fig.2                          |

| 23 (25) | TDOUT    | Analog             | 0   | Tracking drive output                                                       | Fig.2                          |

| 24 (26) | SDIN     | Analog             | ı   | Thread amplifier input                                                      | Fig.1                          |

| 25 (27) | SDOUT    | Analog             | 0   | Thread drive output                                                         | Fig.2                          |

| 26 (28) | VREF     | Analog             | ı   | Bias voltage input                                                          | Fig.6                          |

| 27 (29) | GND1     |                    |     | Digital ground                                                              |                                |

| 28 (30) | CLVS     | Digital            | 0   | Spindle motor drive output and speed control output                         | Fig.7                          |

| 29 (31) | CLVP     | Digital            | 0   | Spindle motor drive output and output for ?rough? control and phase control | Fig.7                          |

| 30 (32) | FSW      | Digital            | 0   | Spindle motor output and filter time constant switching output              | Fig.3                          |

| 31 (33) | RFCK     | Digital            | 0   | Read frame clock output (7.35 kHz crystal)                                  | Fig.5                          |

| 32 (34) | WFCK     | Digital            | 0   | Write frame clock output (7.35 kHz when locked onto crystal)                | Fig.5                          |

| 33 (35) | SUBSYQ   | Digital            | 0   | Subcode synchronization S0 + S1 output                                      | Fig.5                          |

| 34 (36) | SUBDATA  | Digital            | 0   | Subcode serial output                                                       | Fig.5                          |

| 35 (37) | SUBCK    | Digital            | 1   | Subcode readout clock                                                       | Fig.4                          |

| 36 (38) | мск      | Digital            | 1   | Clock for readout of CPU serial data and sub Q code                         | Fig.4                          |

| 37 (39) | DIN      | Digital            | · 1 | CPU serial data input                                                       | Fig.4                          |

| 38 (40) | DOUT     | Digital            | 0   | Serial output of sub Q code and internal status                             | Fig.7                          |

| Pin No.            | Pin name | Analog/<br>digital | 1/0 | Function                                                                                                         | Input/output<br>circuit diagran |  |

|--------------------|----------|--------------------|-----|------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

| 39 (41)            | RW       | Digital            | ı   | Read/write switching and input of the track jump command Data is output from DOUT at "H" and input to DIN at "L" | Fig.4                           |  |

| 40 (42)            | BUSY     | Digital            | 0   | Busy output<br>Linear output of the CLV speed                                                                    | Fig.5                           |  |

| 41~59<br>(43)~(61) | NC       |                    |     |                                                                                                                  |                                 |  |

| 60 (62)            | CLVPA    | Analog             | 0   | Linear output of the CLV phase                                                                                   | Fig.1                           |  |

| 61 (63)            | CLVSA    | Analog             | 0   | Linear output of the CLV speed                                                                                   | Fig.1                           |  |

| 62 (64)            | C2F2     | Digital            | 0   | Channel 2 double error correction flag                                                                           | Fig.5                           |  |

| 63 (65)            | C2F1     | Digital            | 0   | Channel 2 single error correction flag                                                                           | Fig.5                           |  |

| 64 (66)            | C1F2     | Digital            | 0   | Channel 1 double error correction flag                                                                           | Fig.5                           |  |

| 65 (67)            | C1F1     | Digital            | 0   | Channel 1 single error correction flag                                                                           | Fig.5                           |  |

| 66 (68)            | C2CLK    | Digital            | 0   | Strobe signal (f = 176.4 kHz)                                                                                    | Fig.5                           |  |

| 67 (69)            | C2F      | Digital            | 0   | Corrected state output                                                                                           | Fig.5                           |  |

| 68 (70)            | DE       | Digital            | 0   | Strobe signal (f = 88.2 kHz)                                                                                     | Fig.5                           |  |

| 69 (71)            | LRCK     | Digital            | 0   | Strobe signal (f = 44.1 kHz)                                                                                     | Fig.5                           |  |

| 70 (72)            | DOUTA    | Digital            | 0   | Audio data output (2' SCOMP)                                                                                     | Fig.5                           |  |

| 71 (73)            | DOCK     | Digital            | 0   | DOUTA bit clock (f = 2.1168 MHz)                                                                                 | Fig.5                           |  |

| 72 (74)            | CLK      | Digital            | 0   | Clock output (one of four selected with &hE4 command)                                                            | Fig.5                           |  |

| 73 (7Š)            | GND1     |                    |     | Digital ground                                                                                                   |                                 |  |

| 74 (76)            | RESET    | Digital            | ı   | Internal circuit reset (pulled up by internal resistor (100k Ω)                                                  | Fig.8                           |  |

| 75 (77)            | XOUT     | Digital            | 0   | Crystal oscillator circuit output (f = 16.9 MHz)                                                                 | Fig.9                           |  |

| 76 (78)            | XIN      | Digital            | I   | Crystal oscillator circuit input (f = 16.9 MHz)                                                                  | Fig.9                           |  |

| 77 (79)            | GFS      | Digital            | 0   | GFS monitor output (one of four selected with &hE4 command)                                                      | Fig.5                           |  |

| 78 (80)            | VDD1     |                    |     | Digital power supply                                                                                             |                                 |  |

| 79 (1)             | SENS     | Digital            | 0   | Output of status of signal selected with &hE4 command                                                            | Fig.5                           |  |

| 80 (2)             | EXPLCK   | Digital            | 1/0 | PLL output and input of playback clock when attached PLL is in use                                               | Fig.10                          |  |

<sup>\*</sup> BU9317K pin numbers are in parentheses ( ).

# ●Electrical characteristic curves (unless otherwise noted Ta=25°C, Vpp=5V) (BU9317KS)

| Parameter                   | Symbol          | Min. | Тур. | Max.            | Unit | Conditions            | Suitable pins |

|-----------------------------|-----------------|------|------|-----------------|------|-----------------------|---------------|

| Input voltage (high level)  | Vн              | 3.5  | _    | _               | ν.   |                       | *1            |

| Input voltage (low level)   | VIL             |      |      | 0.3             | V    |                       | *1            |

| Output voltage (high level) | Voн             | 4.0  | _    | V <sub>DD</sub> | ٧    | I <sub>OH</sub> =-1mA | *2            |

| Output voltage (low level)  | Vol             | 0    |      | 0.4             | V    | I <sub>OL</sub> =1mA  | *2, 5         |

| Input resistance 1          | V <sub>01</sub> | 80   | 100  | 120             | kΩ   | Between V pp1 pins    | *3            |

| Input resistance 2          | Voz             | 60   | 75   | 90              | kΩ   | Between blas pins     | TZC           |

| Input resistance 3          | Voз             | 180  | 230  | 280             | kΩ   | Between bias pins     | ATS           |

| Input resistance 4          | Vo <sub>4</sub> | 20   | 25   | 30              | kΩ   | Between bias pins     | *6            |

| Input leak current          | lu              | _    |      | ±5              | μΑ   | V₁=0~5.25V            | *1, 2         |

| Output leak current         | llo             |      | _    | ±5              | . μΑ | Vo=0~5.25V            | *4, 5         |

### Suitable pins

- \*1 MIRROR, SCRACH, FOK, SUBCK, MCK, DIN, RW, RESET, EXPLCK, EYE

- \*2 FON, CLVS, CLVP, RFCK, WFCK, SUBSYQ, SUBDATA, DOUT, BUSY, XOUT, SENS, GFS, ASY, C1F1, C1F2, C2F1, C2F2, C2CLK, C2F, DE, LRCK, DOCK, CLK

- \*3 RESET

- \*4 CLVS, CLVP

- \*5 PLLSW, TCAPA2, FSW

- \*6 FEIN, TEIN

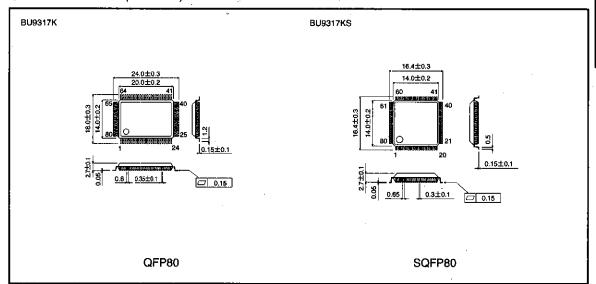

●External dimensions (Units: mm)

# **Notes**

- The contents described in this catalogue are correct as of March 1997.

- No unauthorized transmission or reproduction of this book, either in whole or in part, is permitted.

- The contents of this book are subject to change without notice. Always verify before use that the contents are the latest specifications. If, by any chance, a defect should arise in the equipment as a result of use without verification of the specifications, ROHM CO., LTD., can bear no responsibility whatsoever.

- Application circuit diagrams and circuit constants contained in this data book are shown as examples of standard use and operation. When designing for mass production, please pay careful attention to peripheral conditions.

- Any and all data, including, but not limited to application circuit diagrams, information, and various data, described in this catalogue are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO., LTD., disclaims any warranty that any use of such device shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes absolutely no liability in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices; other than for the buyer's right to use such devices itself, resell or otherwise dispose of the same; no express or implied right or license to practice or commercially exploit any intellectual property rights or other proprietary rights owned or controlled by ROHM CO., LTD., is granted to any such buyer.

- The products in this manual are manufactured with silicon as the main material.

- The products in this manual are not of radiation resistant design.

The products listed in this catalogue are designed to be used with ordinary electronic equipment or devices (such as audio-visual equipment, office-automation equipment, communications devices, electrical appliances, and electronic toys). Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers, or other safety devices) please be sure to consult with our sales representatives in advance.

# Notes when exporting

- It is essential to obtain export permission when exporting any of the above products when it falls under the category of strategic material (or labor) as determined by foreign exchange or foreign trade control laws.

- Please be sure to consult with our sales representatives to ascertain whether any product is classified as a strategic material.