# **CXD2311AR**

# 10-bit 20MSPS Video A/D Converter

## **Description**

The CXD2311AR is a 10-bit CMOS A/D converter for video applications. This IC is ideally suited for the A/D conversion of video signals in TVs, VCRs, camcorders, etc.

#### **Features**

- Resolution: 10-bit ± 1.0 LSB (D.L.E.)

- Maximum sampling frequency: 20MSPS

- Low power consumption: 130mW (at 20MSPS typ.)

(Not including reference current)

- TTL compatible input

- Tri-state TTL compatible output (DVDD = 3.3V)

- · Low input capacitance

- Reference impedance: 280Ω (typ.)

#### **Structure**

Silicon gate CMOS IC

## Absolute Maximum Ratings (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul>           | VDD      | 7                                       | V  |

|----------------------------------------------|----------|-----------------------------------------|----|

| <ul> <li>Reference voltage</li> </ul>        | VRT, VRB | $V_{DD} + 0.5 \text{ to } V_{SS} - 0.5$ | V  |

| <ul> <li>Input voltage (analog)</li> </ul>   | VIN      | $V_{DD} + 0.5 \text{ to } V_{SS} - 0.5$ | V  |

| <ul> <li>Input voltage (digital)</li> </ul>  | VIH, VIL | $V_{DD} + 0.5 \text{ to } V_{SS} - 0.5$ | V  |

| <ul> <li>Output voltage (digital)</li> </ul> | Voн, Vol | $V_{DD} + 0.5 \text{ to } V_{SS} - 0.5$ | V  |

| <ul> <li>Storage temperature</li> </ul>      | Tstg     | -55 to +150                             | °C |

## **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul>    | AVDD, AVSS              | $5.0 \pm 0.25$    | V  |

|---------------------------------------|-------------------------|-------------------|----|

|                                       | DV <sub>DD</sub> , DVss | 3.0 to 5.25       | V  |

|                                       | DVss - AVss             | 0 to 100          | mV |

| Reference input voltage               | VRB                     | More than 1.8     | V  |

|                                       | VRT                     | to $AVDD - 0.4$   | V  |

| <ul> <li>Analog input</li> </ul>      | VIN                     | More than 1.8Vp-p |    |

| <ul> <li>Clock pulse width</li> </ul> | Tpw1                    | 25 (min.)         | ns |

|                                       | Tpw0                    | 25 (min.)         | ns |

| Operating ambient temperations        | rature                  |                   |    |

|                                       | Topr                    | -20 to +75        | °C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

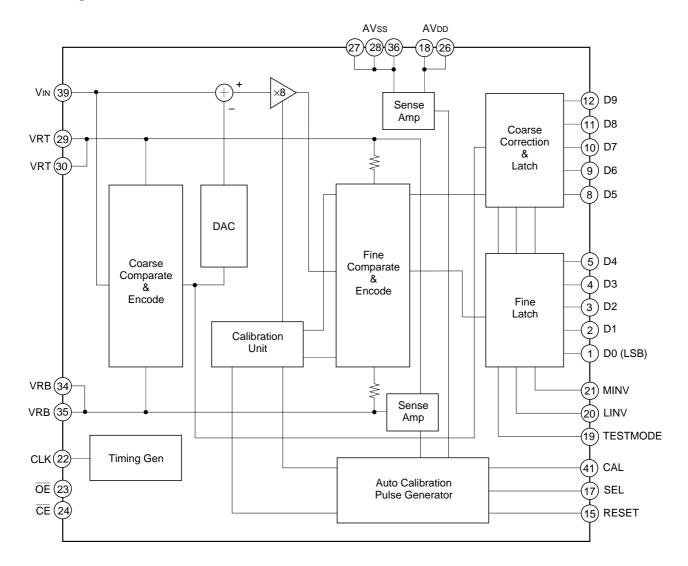

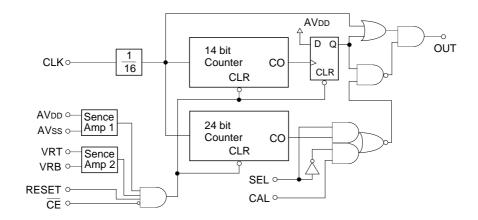

## **Block Diagram**

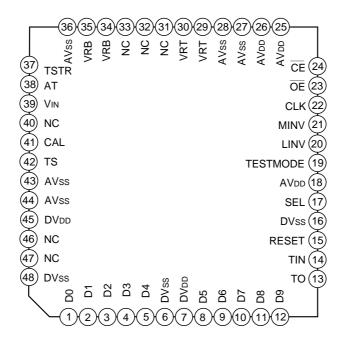

## **Pin Configuration**

## **Pin Description**

| Pin Descript          | -        |                    | Б                                                                                                                               |

|-----------------------|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Pin No                | Symbol   | Equivalent circuit | Description                                                                                                                     |

| 1 to 5<br>8 to 12     | D0 to D9 | DVbb DVss 7/7      | D0 (LSB) to D9 (MSB) output.                                                                                                    |

| 13                    | то       |                    | Test pin. TS = High: High impedance state                                                                                       |

| 7, 45                 | DVdd     |                    | Digital VDD.                                                                                                                    |

| 6, 16, 48             | DVss     |                    | Digital Vss.                                                                                                                    |

| 27, 28, 36,<br>43, 44 | AVss     |                    | Analog Vss.                                                                                                                     |

| 17                    | SEL      | AVDD W AVSS        | Calibration input pulse select after completion of the startup calibration. High: Internal pulse generation Low: External input |

| 22                    | CLK      | AVDD W AVSS AVSS   | Clock pin.                                                                                                                      |

| 41                    | CAL      | AVDD W > AVSS V    | Calibration pulse input.                                                                                                        |

| 15                    | RESET    | AVDD W AVSS        | Calibration circuit reset and startup calibration restart.                                                                      |

| Pin No. | Symbol | Equivalent circuit | Description                                                          |

|---------|--------|--------------------|----------------------------------------------------------------------|

| 14      | TIN    |                    | Test signal input. Normally fixed to AVDD or AVss.                   |

| 29, 30  | VRT    | AVDD AVSS AVSS     | Reference top.                                                       |

| 34, 35  | VRB    | AVss \$ 34 35      | Reference bottom.                                                    |

| 38      | AT     |                    | Test signal output. TS = High: High impedance state                  |

| 42      | тѕ     |                    | Test signal input. Normally fixed to AVDD.                           |

| 37      | TSTR   |                    | Test signal input. Normally fixed to AVss.                           |

| 23      | ŌĒ     | AVDD AVSS AVSS     | D0 to D9 output enable. Low: Output state High: High impedance state |

| 24      | CE     | AVDD W > AVSS      | Chip enable.<br>Low: Active state<br>High: Standby state             |

| Pin No.    | Symbol   | Equivalent circuit | Description                                               |

|------------|----------|--------------------|-----------------------------------------------------------|

| 19         | TESTMODE | AVDD W > AVSS      | Test mode.<br>High: Output state<br>Low: Output fixed     |

| 20         | LINV     | AVDD W >>-         | Output inversion. High: D0 to D8 are inverted and output. |

| 21         | MINV     | AVDD W > -         | Output inversion.<br>High: D9 is inverted and<br>output.  |

| 18, 25, 26 | AVdd     |                    | Analog VDD.                                               |

| 39         | Vin      | AVDD AVSS AVSS     | Analog input.                                             |

## **Digital Output**

The following table shows the correlation between the analog input voltage and the digital output code (TESTMODE = 1, LINV, MINV = 0)

| Input signal voltage | Step       | Digital output code<br>MSB LSB          |

|----------------------|------------|-----------------------------------------|

| VRT                  | 0          | 1 1 1 1 1 1 1 1 1 1                     |

|                      | 511<br>512 | 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 |

| VRB                  | 1023       | 0 0 0 0 0 0 0 0 0                       |

The following table shows the output state for the combination of TESTMODE, LINV, and MINV states.

| TESTMODE | LINV | MINV | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 |

|----------|------|------|----|----|----|----|----|----|----|----|----|----|

| 1        | 0    | 0    | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  |

| 1        | 1    | 0    | N  | N  | N  | Ν  | N  | Ν  | N  | N  | N  | Р  |

| 1        | 0    | 1    | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  | N  |

| 1        | 1    | 1    | N  | N  | N  | Ν  | N  | Ν  | N  | N  | N  | N  |

| 0        | 0    | 0    | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| 0        | 1    | 0    | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  |

| 0        | 0    | 1    | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  |

| 0        | 1    | 1    | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

P: Forward-phase output N: Inverted output

Electrical Characteristics (Fc = 20MSPS, AVDD = 5V, DVDD = 3.3V, VRB = 2.0V, VRT = 4.0V, Ta = 25°C)

| Item                               |            | Symbol           |                                                    | onditions                   | Min.            | Тур. | Max. | Unit |

|------------------------------------|------------|------------------|----------------------------------------------------|-----------------------------|-----------------|------|------|------|

| Max. conversion rat                | te         | Fc max           | Fin = 1.0kHz                                       |                             | 20              |      |      | MCDC |

| Min. conversion rate               | e          | Fc min           | triangular wa                                      | ave input                   |                 |      | 0.5  | MSPS |

| Supply Ana                         | alog       | IAdd             | Fin = 1.0kHz                                       | ·                           | 16              | 23   | 30   |      |

| current Dig                        | jital      | ID <sub>DD</sub> | triangular wa                                      | ave input                   |                 | 3.0  | 5.0  | mA   |

| Standby Ana                        | alog       | IAst             | CE = High                                          |                             |                 |      | 1.0  |      |

| current Dig                        | jital      | IDsт             | CE = High                                          |                             |                 |      | 1.0  | μA   |

| Deference nin com                  | 4          | IRT              |                                                    |                             | 5.0             | 7.0  | 11.0 | Л    |

| Reference pin curre                | ent        | lпв              |                                                    |                             | -11.0           | -7.0 | -5.0 | mA   |

| Analog input band                  |            | BW               | -1dB                                               |                             |                 | 35   |      | MHz  |

| Analog input capac                 | itance     | CIN              |                                                    |                             |                 | 10   |      | pF   |

| Reference resistand<br>(VRT – VRB) | ce value   | RREF             |                                                    |                             | 180             | 280  | 380  | Ω    |

| Offset voltage                     |            | Еот              | Eot = theore                                       | etical value-actual<br>alue | -22             | 8    | 28   | - mV |

| Oliset Voltage                     |            | Еов              | EOB = actuation theoretical v                      | al measured value-<br>alue  | -18             | 12   | 42   | IIIV |

| Startup calibration s              | start      | Vcal1            | AVDD - AVS                                         | S                           |                 | 2.5  |      | V    |

| voltage                            |            | Vcal2            | VRT – VRB                                          |                             |                 | 1.0  |      | ] V  |

| Digital input voltage              | VIH        |                  | AV <sub>DD</sub> = 4.75V to 5.25V                  |                             | 2.3             |      |      | V    |

| Digital Input Voltage              | •          | VIL              | AVDD = 4.75V to 5.25V                              |                             |                 |      | 0.8  | ]    |

| Analog input curren                | <b>.</b> + | Аін              | Vin = 4V                                           |                             |                 | 30   | 50   | μA   |

| Analog input curren                |            | AıL              | VIN = 2V                                           |                             | <del>-</del> 50 | -10  |      | μΛ   |

| Digital input current              |            | Iн               | DV <sub>DD</sub> = max                             | VIH = DVDD                  |                 |      | 5    | μΑ   |

| Digital input current              | •          | lı∟              | D V DD = III ax                                    | VIL = 0V                    |                 |      | 5    | μπ   |

| Digital output curre               | nt         | Іон              | $\overline{OE} = AVss$                             | Voh = DVdd - 0.5V           | 3.5             |      |      | mA   |

| Digital output curren              | ii.        | lol              | $DV_{DD} = min$                                    | Vol = 0.4V                  | 3.5             |      |      | IIIA |

| Digital output curre               | nt         | Іоzн             | $\overline{OE} = AV_DD$                            | Voh = DVdd                  |                 |      | 1    | μA   |

| Digital output curren              | ıı         | lozL             | $DV_{DD} = max$                                    | Vol = 0V                    |                 |      | 1    | _ μΑ |

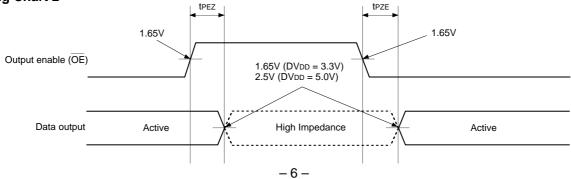

| Tri-state output disa              | able time  | <b>t</b> PEZ     | Clock not synchronized for active → high impedance |                             | 20              | 25   | 30   | ns   |

| Tri-state output ena               | ıble time  | <b>t</b> pze     | Clock not synchronized for high impedance → active |                             | 10              | 15   | 20   | ns   |

| Integral non-linearit              | y error    | EL               |                                                    |                             |                 | ±1.3 | ±2.0 | LCD  |

| Differential non-linea             | rity error | Ep               |                                                    |                             |                 | ±0.5 | ±1.0 | LSB  |

| Differential gain erro             | or         | DG               | NTSC 40 IRE mod                                    |                             |                 | 1.0  |      | %    |

| Differential phase e               | rror       | DP               | ramp, Fc = 14.3MSPS                                |                             |                 | 0.3  |      | deg  |

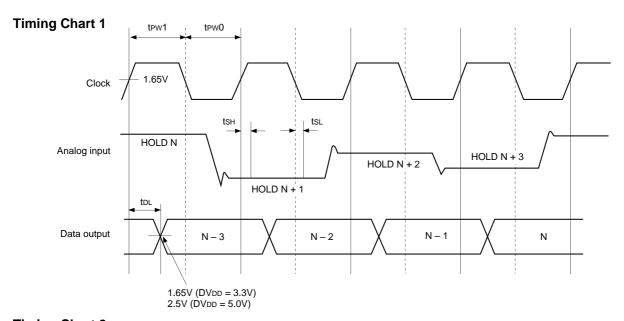

| Output data delay                  |            | <b>t</b> DL      | CL = 20pF                                          |                             | 8               | 13   | 18   | ns   |

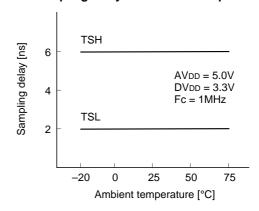

| Sampling delay                     |            | <b>t</b> sн      |                                                    |                             | 0               | 6    |      | ns   |

| Camping delay                      |            | <b>t</b> sL      |                                                    |                             |                 | 2    | 4    | 113  |

| Item     | Symbol | Conditions   | Min. | Тур. | Max. | Unit |

|----------|--------|--------------|------|------|------|------|

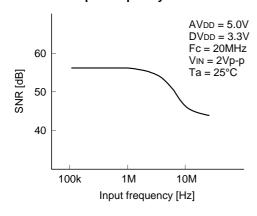

|          |        | Fin = 100kHz |      | 56   |      |      |

|          |        | Fin = 500kHz |      | 56   |      |      |

| SNR      | SNR    | Fin = 1MHz   |      | 56   |      | dB   |

| SIVIC    | Ortic  | Fin = 3MHz   |      | 55   |      | ub   |

|          |        | Fin = 7MHz   |      | 50   |      |      |

|          |        | Fin = 10MHz  |      | 46   |      |      |

| SFDR SFD | SFDR   | Fin = 100kHz |      | 68   |      |      |

|          |        | Fin = 500kHz |      | 67   |      |      |

|          |        | Fin = 1MHz   |      | 65   |      | dB   |

|          | O Di   | Fin = 3MHz   |      | 65   |      | ub   |

|          |        | Fin = 7MHz   |      | 54   |      |      |

|          |        | Fin = 10MHz  |      | 53   |      |      |

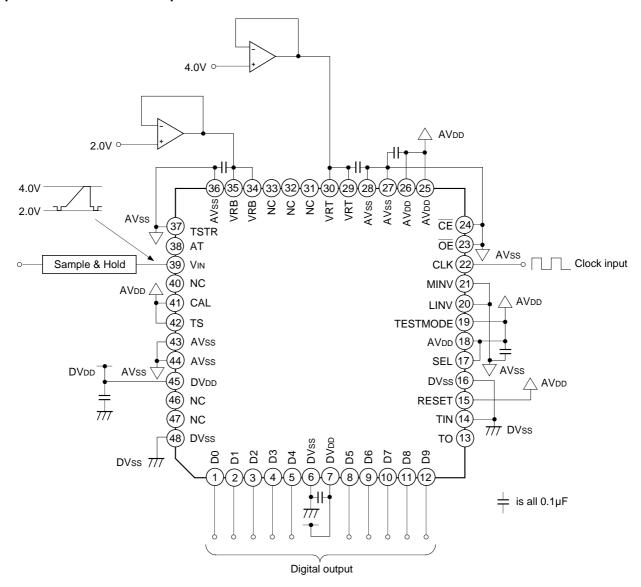

## Application Circuit 1. Startup calibration + internal auto calibration

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

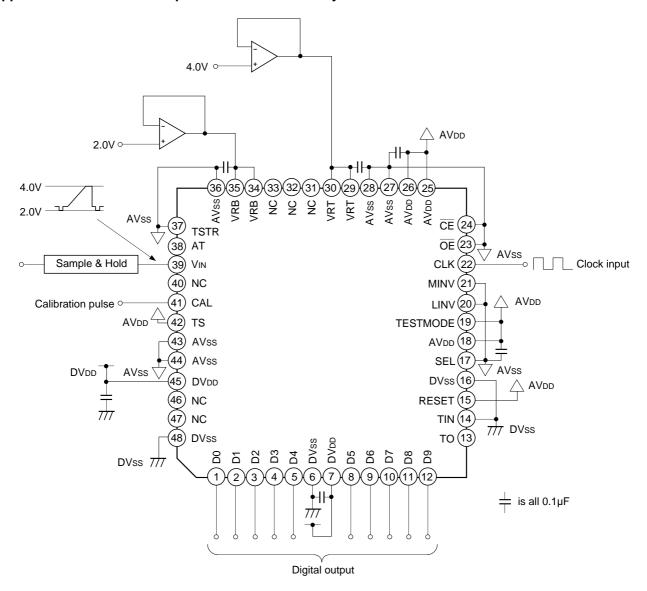

## Application Circuit 2. Startup calibration + external sync calibration

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

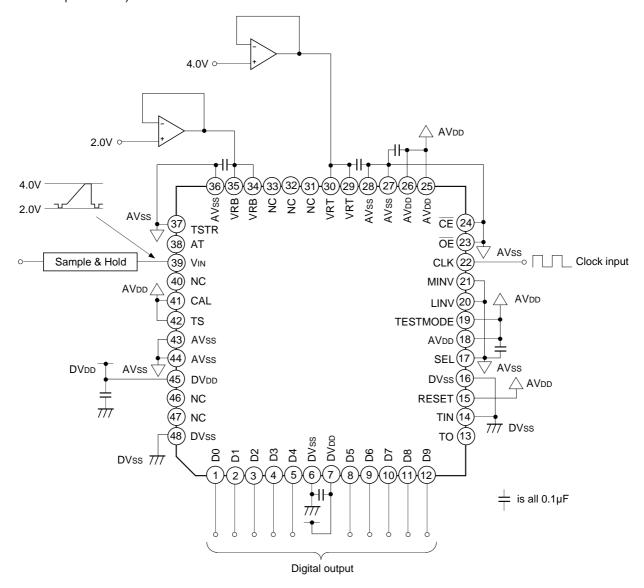

## Application Circuit 3. Only startup calibration

(Less than supply voltage fluctuation range of AV<sub>DD</sub> =  $\pm 100$ mV and reference voltage fluctuation range of |VRT - VRB| = 200mV)

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### 1. Calibration Function

In order to achieve superior linearity, the CXD2311AR has a built-in calibration circuit. In order to eliminate the necessity for the externally input calibration pulse required by the earlier CXD2311R, a startup calibration function and an auto calibration pulse generation function have been newly added to the CXD2311AR. Fig. 1 shows a block diagram of the calibration pulse generation circuit.

Fig. 1. Calibration Pulse Generation Circuit

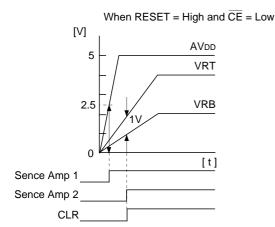

#### (1) Startup Calibration Function

Over 600 calibration pulses are needed to complete the initial calibration process when the power is first supplied to the IC. The startup calibration function automatically generates these pulses internally and completes the initial calibration process.

The following five conditions must be satisfied to initiate the startup calibration function.

- a) The voltage between AV<sub>DD</sub> and AVss is approximately 2.5V or more.

- b) The voltage between VRT and VRB is approximately 1V or more.

- c) The RESET pin (Pin 15) must is high.

- d) The CE pin (Pin 24) must is low.

- e) Condition b is met after condition a.

Once all five of these conditions have been met, the calibration pulses are generated. The pulses are generated by counting 16 main clock cycles on a 14-bit counter and closing the gate when the carry-out occurs. Therefore, the time required for startup calibration after the above five conditions have been met is determined by the following formula:

Startup calibration time = main clock cycle  $\times$  16  $\times$  16,384

For example, if the main clock frequency is 14.3MHz, the time required for startup calibration is 18ms.

#### (2) Auto Calibration Pulse Generation Function

After startup calibration is completed, this function periodically generates calibration pulses so that calibration can be performed constantly without any need for input of calibration pulses from an external source. This function counts 16 main clock cycles on a 24-bit counter and uses the carry-out as the calibration pulse. The cycle of the calibration pulse generated in this fashion is as follows:

Internal calibration pulse generation cycle = main clock cycle  $\times$  16  $\times$  16,777,216

Therefore, if the main clock frequency is 14.3MHz, the calibration pulse cycle is approximately 19 seconds; since calibration is performed once every seven pulses, the calibration cycle is approximately 130 seconds. In order to use this function, the SEL pin (Pin 17) must be high.

Note that this function cannot be used if fixing the lower bits in the calibration operation as described below will cause problems because this function is executed asynchronously without regard to the input signals.

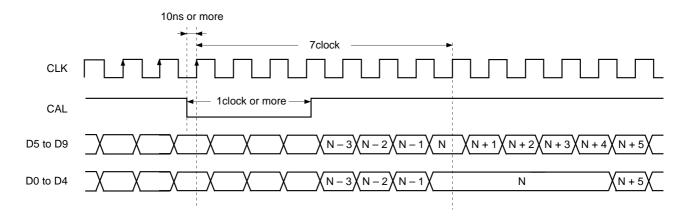

#### (3) External Calibration Pulse Input Function

If the auto calibration function cannot be used, calibration can be performed in synchronization with the input signals when a calibration pulse is input from the CAL pin (Pin 41) by setting the SEL pin (Pin 17) low.

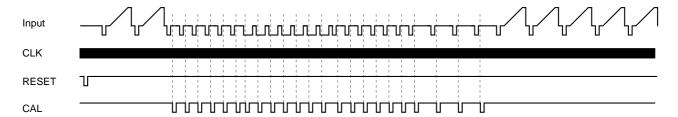

Fig. 2. Calibration Timing Chart

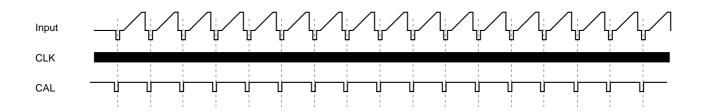

Calibration starts when the falling edge of the pulse input to the CAL pin (Pin 41) is detected. Because the lower comparator is occupied for four clock cycles at this point, the previous lower data is held for four clock cycles after seven clock cycles since the rising edge of the clock cycle in which the falling edge of CAL was detected. Calibration can be performed outside of video intervals by using the sync signal, etc., to input the CAL signal. An example of this is shown below.

#### [1] Inputting CAL every H-sync

## [2] Inputting CAL every V-sync

It is also possible to use only the startup calibration function by leaving the SEL pin (Pin 17) low and fixing the CAL pin (Pin 41) either high or low. Note that this method requires restriction of the fluctuation range of the supply voltage and the reference voltage.

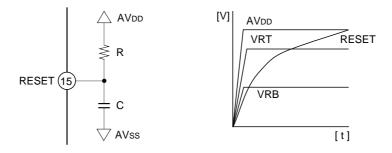

## (4) Re-initiating the Startup Calibration Function

The startup calibration function can be re-initiated after the power and reference voltage are supplied by using the CE pin (Pin 24) and the RESET pin (Pin 15). Particularly in cases where the riseup characteristics of the power supply and the reference voltage are unstable or the order of the riseup is not kept, it is possible to initiate startup calibration properly by connecting a CR and delaying startup until after power supply riseup.

Fig. 3. Initiation of the Startup Calibration Function Using the RESET pin

### 2. Power supply

To prevent the influence of noise, connect the power supply to a 0.1µF by-pass capacitor as near the device as possible.

#### 3. DVDD

Either a 3.3V or 5.0V digital power supply can be used. Compared to the 5.0V power supply, the 3.3V power supply generates a decreased amount of radiation noise but offers a decreased drive capacity. These two power supplies do not virtually differ in static and dynamic characteristics. Further, the High output level rises up to DVpp.

### 4. Reference input

The voltage to be supplied to the reference pins must be driven by a buffer having a 10mA or more drive capacity. For supplied voltage stabilization, connect the buffer to a 0.1µF by-pass capacitor as near the pins as possible.

#### 5. Latch-up

Ensure that the AVDD and DVDD pins share the same power supply on a board to prevent latch-up which may be caused by power ON time-lag.

#### 6. Board

To obtain full-expected performance from this IC, be sure that the mounting board has a large ground pattern for lower impedance. It is recommended that the IC be mounted on a board without using a socket to evaluate its characteristics adequately.

### **Example of Representative Characteristics**

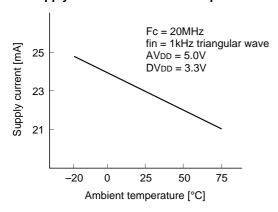

#### Supply current vs. Ambient temperature

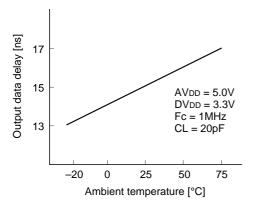

#### Output data delay vs Ambient temperature

#### Input frequency vs. SNR

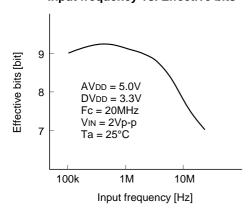

## Input frequency vs. Effective bits

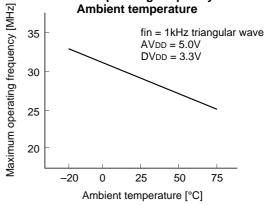

## Maximum operating frequency vs. Ambient temperature

#### Sampling delay vs. Ambient temperature

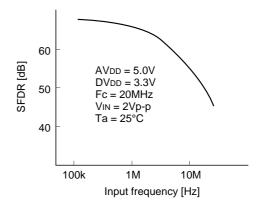

#### Input frequency vs. SFDR

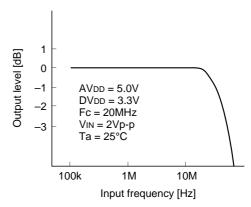

#### Input band

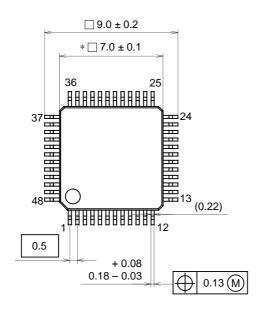

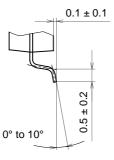

## Package Outline Unit: mm

# 48PIN LQFP (PLASTIC)

NOTE: Dimension "\*" does not include mold protrusion.

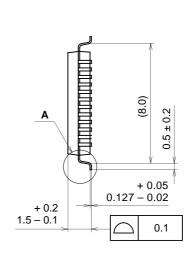

DETAIL A

| SONY CODE  | LQFP-48P-L01   |

|------------|----------------|

| EIAJ CODE  | LQFP048-P-0707 |

| JEDEC CODE |                |

## PACKAGE STRUCTURE

| PACKAGE MATERIAL | EPOXY RESIN                 |

|------------------|-----------------------------|

| LEAD TREATMENT   | SOLDER/PALLADIUM<br>PLATING |

| LEAD MATERIAL    | 42/COPPER ALLOY             |

| PACKAGE MASS     | 0.2g                        |