# **Timing Generator for Progressive Scan CCD Image Sensor**

### **Description**

The CXD2457R is an IC developed to generate the timing pulses required by Progressive Scan CCD image sensors as well as signal processing circuits.

#### **Features**

- Electronic shutter function

- Supports non-interlaced operation

- Base oscillation frequency 30.0MHz

- Horizontal drive frequency switchable between 15/10/5MHz

- Switchable between FINE (Progressive Scan) mode or DRAFT (high-frame rate readout) mode

- Vertical driver

### **Applications**

Progressive Scan CCD cameras

#### Structure

Silicon gate CMOS IC

### **Applicable CCD Image Sensor**

ICX204AK

### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul> | Vdda, | VDDb, VDDc, VDDd         |    |

|------------------------------------|-------|--------------------------|----|

|                                    |       | Vss - 0.5 to $Vss + 7.0$ | V  |

| <ul> <li>Supply voltage</li> </ul> | Vss   | VL - 0.5 to $VL + 10.0$  | V  |

| <ul> <li>Supply voltage</li> </ul> | VH    | VL - 0.5 to $VL + 26.0$  | V  |

| <ul> <li>Supply voltage</li> </ul> | VM    | VL - 0.5 to $VL + 26.0$  | V  |

| <ul> <li>Input voltage</li> </ul>  | Vı    | $Vss-0.5\ to\ VdD+0.5$   | V  |

| <ul> <li>Output voltage</li> </ul> | Vo    | $Vss-0.5\ to\ VdD+0.5$   | V  |

| Operating tempera                  | ature |                          |    |

|                                    | Topr  | -20 to +75               | °C |

| Storage temperatu                  | ıre   |                          |    |

|                                    | Tstg  | -55 to +150              | °C |

|                                    |       |                          |    |

#### **Recommended Operating Conditions**

|                                      |                      | ,              |    |

|--------------------------------------|----------------------|----------------|----|

| <ul> <li>Supply voltage 1</li> </ul> | V <sub>DD</sub> a, \ | VDDb, VDDC     |    |

|                                      |                      | 3.0 to 3.6     | V  |

| • Supply voltage 2                   | VDDd                 | 3.0 to 3.6     | V  |

| • Supply voltage 3                   | VH                   | 14.25 to 15.75 | V  |

| • Supply voltage 4                   | VL                   | −9.0 to −5.0   | V  |

| • Supply voltage 5                   | VM                   | 0              | V  |

| Operating temperating temperature    | ature                |                |    |

|                                      | Topr                 | -20 to +75     | °C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

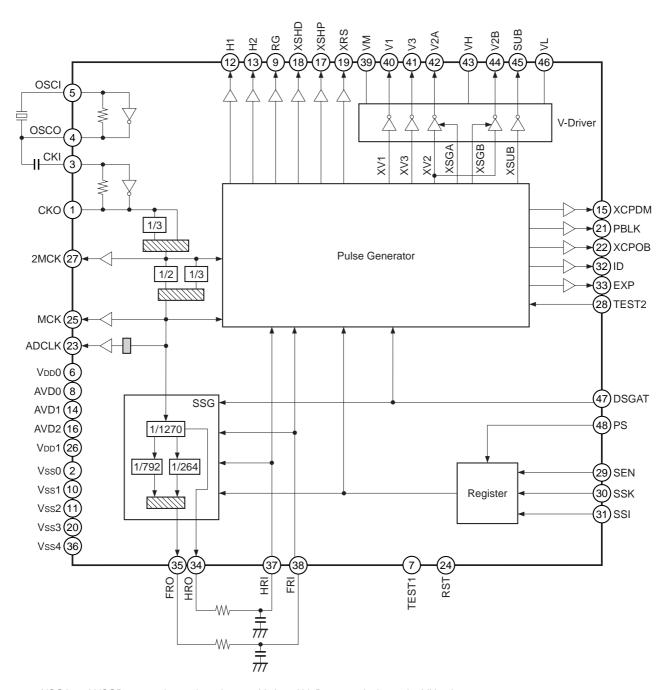

### **Block Diagram**

$\mathsf{XSGA}$  and  $\mathsf{XSGB}$  are readout pulses that use V2A and V2B, respectively, as the VH value.

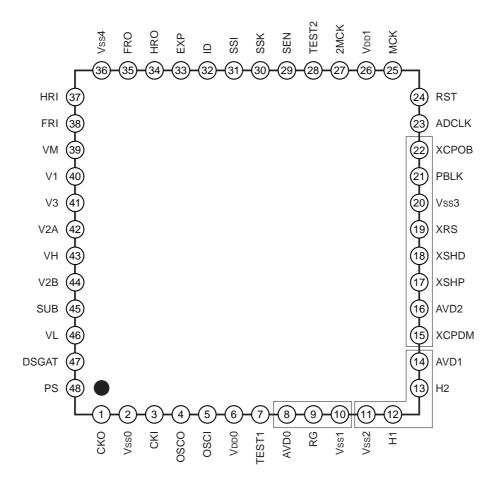

# Pin Configuration (Top View)

The enclosed pins use separate power supplies.

# **Pin Description**

| Pin<br>No. | Symbol | I/O | Description                                                                               |

|------------|--------|-----|-------------------------------------------------------------------------------------------|

| 1          | СКО    | 0   | Oscillator output. (30.0MHz)                                                              |

| 2          | Vss0   | _   | GND                                                                                       |

| 3          | CKI    | I   | Oscillator input. (30.0MHz)                                                               |

| 4          | osco   | 0   | Inverter output for oscillation. (30.0MHz)                                                |

| 5          | OSCI   | I   | Inverter input for oscillation. (30.0MHz)                                                 |

| 6          | VDD0   | _   | Power supply.                                                                             |

| 7          | TEST1  | ı   | Test. With pull-down resistor. Fix to low.                                                |

| 8          | AVD0   | _   | Power supply.                                                                             |

| 9          | RG     | 0   | Reset gate pulse output.                                                                  |

| 10         | Vss1   | _   | GND                                                                                       |

| 11         | Vss2   | _   | GND                                                                                       |

| 12         | H1     | 0   | Clock output for horizontal CCD drive.                                                    |

| 13         | H2     | 0   | Clock output for horizontal CCD drive.                                                    |

| 14         | AVD1   | _   | Power supply.                                                                             |

| 15         | XCPDM  | 0   | Clamp pulse.                                                                              |

| 16         | AVD2   | _   | Power supply.                                                                             |

| 17         | XSHP   | 0   | Sample-and-hold pulse.                                                                    |

| 18         | XSHD   | 0   | Sample-and-hold pulse.                                                                    |

| 19         | XRS    | 0   | Sample-and-hold pulse.                                                                    |

| 20         | Vss3   | _   | GND                                                                                       |

| 21         | PBLK   | 0   | Blanking cleaning pulse.                                                                  |

| 22         | ХСРОВ  | 0   | Clamp pulse.                                                                              |

| 23         | ADCLK  | 0   | Clock output for AD conversion.                                                           |

| 24         | RST    | I   | Reset (Low: Reset, High: Normal operation). Always input one reset pulse during power-on. |

| 25         | MCK    | 0   | Clock output for digital circuit.                                                         |

| 26         | VDD1   | _   | Power supply.                                                                             |

| 27         | 2MCK   | 0   | Clock output for digital circuit.                                                         |

| 28         | TEST2  | I   | Test. Fix to high.                                                                        |

| 29         | SEN    | I   | PS = High: Drive frequency setting input. PS = Low: Serial setting strobe input.          |

| 30         | SSK    | I   | PS = High: Readout method setting input. PS = Low: Serial setting clock input.            |

| 31         | SSI    | I   | PS = High: Shutter speed setting input. PS = Low: Serial setting data input.              |

| 32         | ID     | 0   | Line identification signal output write enable pulse output or XSUB output.               |

| 33         | EXP    | 0   | Pulse output indicating exposure is underway or checksum result output.                   |

| Pin<br>No. | Symbol | I/O | Description                                                                                                     |

|------------|--------|-----|-----------------------------------------------------------------------------------------------------------------|

| 34         | HRO    | 0   | Horizontal sync signal (HR) output or XSGB output.                                                              |

| 35         | FRO    | 0   | Horizontal sync signal (FR) output or XSGA output.                                                              |

| 36         | Vss4   | _   | GND                                                                                                             |

| 37         | HRI    | I   | Horizontal sync signal (HR) input.                                                                              |

| 38         | FRI    | I   | Horizontal sync signal (FR) input.                                                                              |

| 39         | VM     | _   | GND (vertical clock driver GND).                                                                                |

| 40         | V1     | 0   | Clock output for vertical CCD drive.                                                                            |

| 41         | V3     | 0   | Clock output for vertical CCD drive.                                                                            |

| 42         | V2A    | 0   | Clock output for vertical CCD drive.                                                                            |

| 43         | VH     | _   | 15V power supply (vertical clock driver power supply).                                                          |

| 44         | V2B    | 0   | Clock output for vertical CCD drive.                                                                            |

| 45         | SUB    | 0   | CCD electric charge sweep pulse output.                                                                         |

| 46         | VL     | _   | -7.5V power supply (vertical clock driver power supply).                                                        |

| 47         | DSGAT  | I   | Output stop (Same operation control as SLP when low).                                                           |

| 48         | PS     | I   | Parallel/serial switching for mode setting input method. (High: Parallel, Low: Serial) With pull-down resistor. |

# **Electrical Characteristics**

# **DC Characteristics**

(Within the recommended operating conditions)

| Item             | Pins                              | Symbol            | Conditions                         | Min.       | Тур. | Max.      | Unit |

|------------------|-----------------------------------|-------------------|------------------------------------|------------|------|-----------|------|

| Supply voltage 1 | VDDO, VDD1,                       | V <sub>DD</sub> a | Containone                         | 3.0        | 3.3  | 3.6       | V    |

| Supply voltage 2 | AVD0                              | VDDb              |                                    | 3.0        | 3.3  | 3.6       | V    |

| Supply voltage 3 |                                   | VDDC              |                                    | 3.0        | 3.3  | 3.6       | V    |

| Supply voltage 4 | AVD2                              | VDDd              |                                    | 3.0        | 3.3  | 3.6       | V    |

| Supply voltage 5 | VH                                | VH                |                                    | 14.5       | 15.5 | 15.5      | V    |

| Supply voltage 6 | VM                                | VM                |                                    | _          | 0.0  | _         | V    |

| Supply voltage 7 | VL                                | VL                |                                    | -9.0       |      | -5.0      | V    |

|                  |                                   | VIH1              |                                    | 0.7Vppa    |      |           | V    |

| Input voltage 1  | CKI                               | VIL1              |                                    |            |      | 0.3Vppa   | V    |

|                  |                                   | VIH2              |                                    | 0.7Vpdb    |      |           | V    |

| Input voltage 2  | TEST1, PS                         | VIL2              |                                    |            |      | 0.3Vppa   | V    |

|                  | RST, TEST2,                       | Vt + 1            |                                    | 0.8Vppa    |      |           | V    |

| Input voltage 3  | SEN, SSK, SSI,<br>HRI, FRI, DSGAT | Vt – 1            |                                    |            |      | 0.2Vppa   | V    |

|                  | CKO, MCK,<br>2MCK                 | Vон1              | Feed current where IoH = -10.0mA   | VDDa - 0.8 |      |           | V    |

| Output voltage 1 |                                   | Vol1              | Pull-in current where IoL = 7.2mA  |            |      | 0.4       | V    |

| Output valtage 2 | RG                                | Voн2              | Feed current where IoH = -3.3mA    | VDDb - 0.8 |      |           | V    |

| Output voltage 2 |                                   | VOL2              | Pull-in current where IoL = 2.4mA  |            |      | 0.4       | V    |

| Output voltage 2 | U4 U2                             | Vонз              | Feed current where IoH = -36.0mA   | VDDC - 0.8 |      |           | V    |

| Output voltage 3 | H1, H2                            | Vol3              | Pull-in current where IoL = 24.0mA |            |      | 0.4       | V    |

| Output voltage 4 | XCPDM, XSHP,                      | Vон4              | Feed current where IoH = -3.3mA    | VDDd - 0.8 |      |           | V    |

| Output voltage 4 | XSHD, XRS,<br>PBLK, XCPOB         | Vol4              | Pull-in current where IoL = 2.4mA  |            |      | 0.4       | V    |

| Output voltage 5 | ID, EXP, HRO,                     | Vон5              | Feed current where IoH = -2.4mA    | VDDa - 0.8 |      |           | V    |

| Output voltage 5 | FRO                               | Vol5              | Pull-in current where IoL = 4.8mA  |            |      | 0.4       | V    |

| Output voltage 6 | SUB                               | Vон6              | Feed current where IoH = -4.0mA    | VH - 0.25  |      |           | V    |

| Output voltage o | 306                               | Vol6              | Pull-in current where IoL = 5.4mA  |            |      | VL + 0.25 | V    |

| Output voltage 7 | V1, V3                            | Vом7              | Feed current where IoH = -5.0mA    | VM - 0.25  |      |           | V    |

| Output voltage 7 | V 1, V 3                          | Vol7              | Pull-in current where IoL = 10.0mA |            |      | VL + 0.25 | V    |

|                  |                                   | Vом101            | Feed current where IoH = -7.2mA    | VH - 0.25  |      |           | V    |

| Output voltage 8 | V2A, V2B                          | VOM102            | Pull-in current where IoL = 5.0mA  |            |      | VM + 0.25 | V    |

| Output voltage o | VZM, VZD                          | Vol8              | Feed current where IoH = -5.0mA    | VM - 0.25  |      |           | V    |

|                  |                                   | Vol8              | Pull-in current where IoL = 10.0mA |            |      | VL + 0.25 | V    |

#### Inverter I/O Characteristics for Oscillation

#### (Within the recommended operating conditions)

| Item                 | Pins       | Symbol | Conditions                        | Min.    | Тур.   | Max.    | Unit |

|----------------------|------------|--------|-----------------------------------|---------|--------|---------|------|

| Logical Vth          | OSCI       | LVth   |                                   |         | VDDa/2 |         | V    |

| Input voltage        | OSCI       | ViH    |                                   | 0.7VDDd |        |         | V    |

|                      | USCI       | VIL    |                                   |         |        | 0.3VDDa | V    |

| Output voltage       | osco       | Vон    | Feed current where Ioн = -6.0mA   | VDDa/2  |        |         | V    |

|                      |            | Vol    | Pull-in current where IoL = 6.0mA |         |        | VDDa/2  | V    |

| Feedback resistor    | OSCI, OSCO | RFB    | VIN = VDDd or Vss                 | 500k    | 2M     | 5M      | Ω    |

| Oscillator frequency | OSCI, OSCO | f      |                                   | 20      |        | 50      | MHz  |

### **Base Oscillation Clock Input Characteristics**

#### (Within the recommended operating conditions)

| Item                | Pins | Symbol | Conditions           | Min.    | Тур.   | Max.    | Unit |

|---------------------|------|--------|----------------------|---------|--------|---------|------|

| Logical Vth         |      | LVth   |                      |         | VDDa/2 |         | V    |

| Input voltage       | CKI  | ViH    |                      | 0.7VDDa |        |         | V    |

|                     | CKI  | VIL    |                      |         |        | 0.3VDDa | V    |

| Input amplification |      | Vin    | fmax 50MHz sine wave | 0.3     |        |         | Vp-p |

<sup>\*1</sup> Input voltage is the input voltage characteristics for direct input from an external source. Input amplification is the input amplification characteristics for input through capacitor.

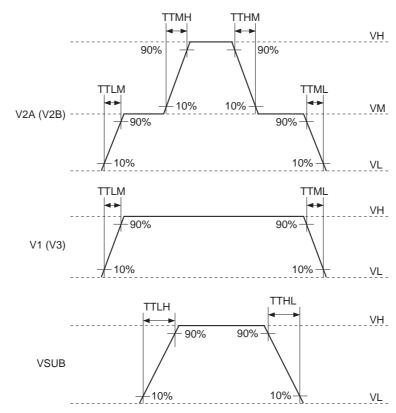

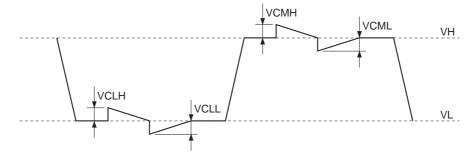

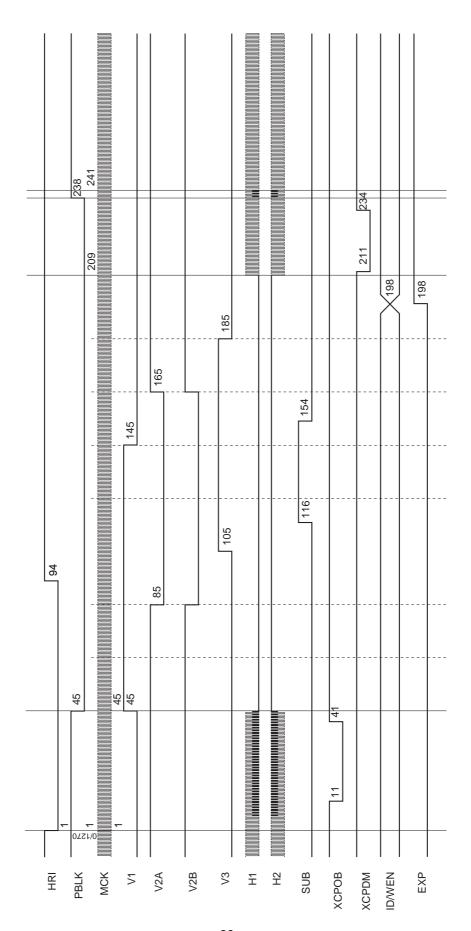

# **Switching Characteristics**

(VH = 15.0V, VM = GND, VL = -8.5V)

| Item         | Symbol | Conditions | Min. | Тур. | Max. | Unit |

|--------------|--------|------------|------|------|------|------|

|              | TTLM   | VL to VM   |      | 350  | 550  | ns   |

| Rise time    | TTMH   | VM to VH   |      | 450  | 700  | ns   |

|              | TTLH   | VL to VH   |      | 50   | 80   | ns   |

|              | TTML   | VM to VL   |      | 250  | 400  | ns   |

| Fall time    | TTHM   | VH to VM   |      | 300  | 450  | ns   |

|              | TTHL   | VH to VL   |      | 50   | 80   | ns   |

|              | VCLH   |            |      |      | 1.0  | V    |

| Output noise | VCLL   |            |      |      | 1.0  | ٧    |

| voltage      | VCMH   |            |      |      | 1.0  | V    |

|              | VCML   |            |      |      | 1.0  | V    |

<sup>\*1</sup> The MOS structure of this IC has a low tolerance for static electricity, so full care should be given for measures to prevent electrostatic discharge.

<sup>\*2</sup> For noise and latch-up countermeasures, be sure to connect a bypass capacitor (0.1μF or more) between each power supply pin (VH, VL) and GND.

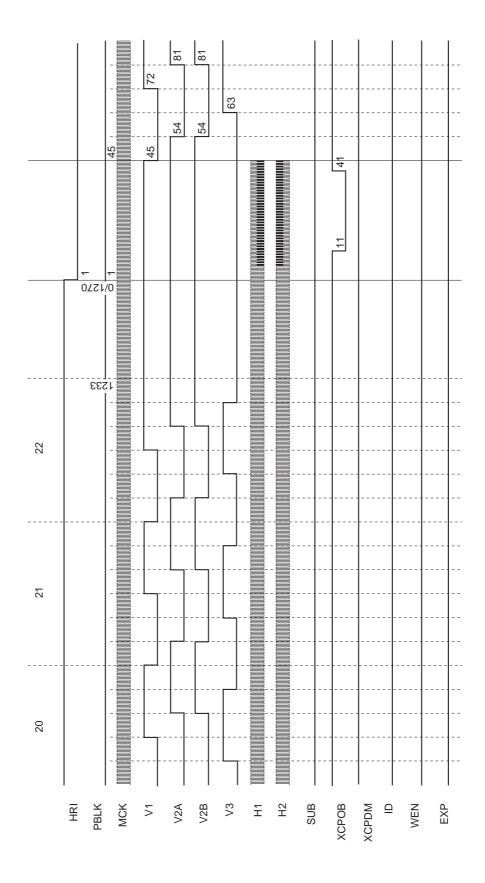

# **Switching Waveforms**

### **Waveform Noise**

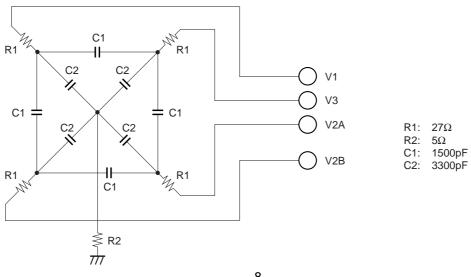

### **Measurement Circuit**

### **AC Characteristics**

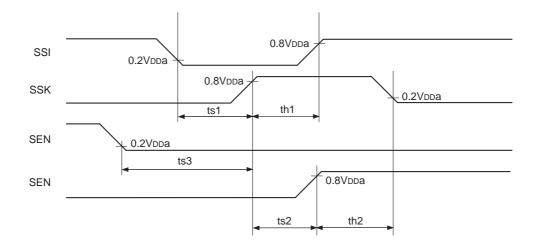

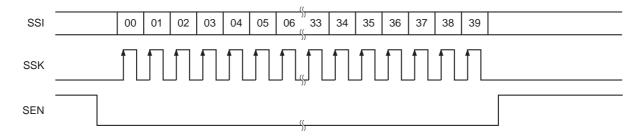

### 1) AC characteristics between the serial interface clocks

(Within the recommended operating conditions)

| Symbol | Definition                                          | Min. | Тур. | Max. | Unit |

|--------|-----------------------------------------------------|------|------|------|------|

| ts1    | SSI setup time, activated by the rising edge of SSK | 20   |      |      | ns   |

| th1    | SSI hold time, activated by the rising edge of SSK  | 20   |      |      | ns   |

| ts2    | SSK setup time, activated by the rising edge of SEN | 20   |      |      | ns   |

| th2    | SSK hold time, activated by the rising edge of SEN  | 20   |      |      | ns   |

| ts3    | SEN setup time, activated by the rising edge of SSK | 20   |      |      | ns   |

| fk     | SSK frequency                                       |      |      | 7.5  | MHz  |

### 2) Serial interface clock internal loading characteristics

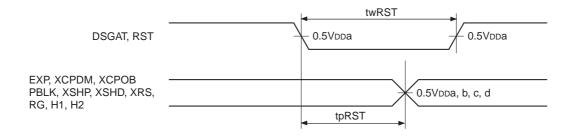

### 3) Output timing characteristics using DSGAT and RST

H1 and H2 load capacitance = 180pF

EXP, XCPDM, PBLK, XSHP, XSHD, XRS and RG load capacitance = 10pF

(Within the recommended operating conditions)

| Symbol | Definition                                                                             | Min. | Тур. | Max. | Unit |

|--------|----------------------------------------------------------------------------------------|------|------|------|------|

| tpRST  | Time until the above outputs reach the specified value after the fall of DSGAT and RST |      |      | 75   | ns   |

| twRST  | RST and DSGAT pulse width                                                              | 10   |      |      | ns   |

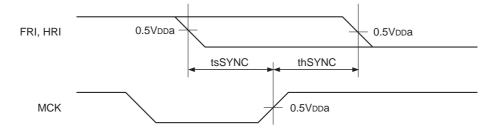

### 4) FRI and HRI loading characteristics

### MCK load capacitance = 10pF

(Within the recommended operating conditions)

| Symbol | Definition                                                  | Min. | Тур. | Max. | Unit |

|--------|-------------------------------------------------------------|------|------|------|------|

| tsSYNC | FRI and HRI setup time, activated by the rising edge of MCK | 5    |      |      | ns   |

| thSYNC | FRI and HRI hold time, activated by the rising edge of MCK  | 5    |      |      | ns   |

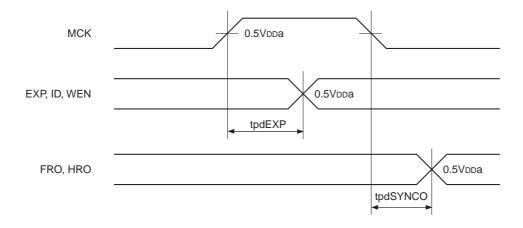

# 5) Output variation characteristics of ID, WEN, EXP, FRO and HRO

EXP, ID and WEN load capacitance = 10pF

(Within the recommended operating conditions)

| Symbol   | Definition                                                          | Min. | Тур. | Max. | Unit |

|----------|---------------------------------------------------------------------|------|------|------|------|

| tpdEXP   | Time until the WEN, ID and EXP outputs change after the rise of MCK | 0.5  |      | 8.5  | ns   |

| tpdSYNCO | Time until the FRO and HRO outputs change after the rise of MCK     | 1.0  |      | 11.5 | ns   |

#### **Description of Operation**

### 1. Progressive Scan CCD drive pulse generation

- Combining this IC with a crystal oscillator generates a fundamental frequency of 30.0MHz.

- CCD drive pulse generation is synchronized with HRI and FRI.

- The CCD drive method can be changed to various modes by inputting serial data or parallel data to the CXD2457R.

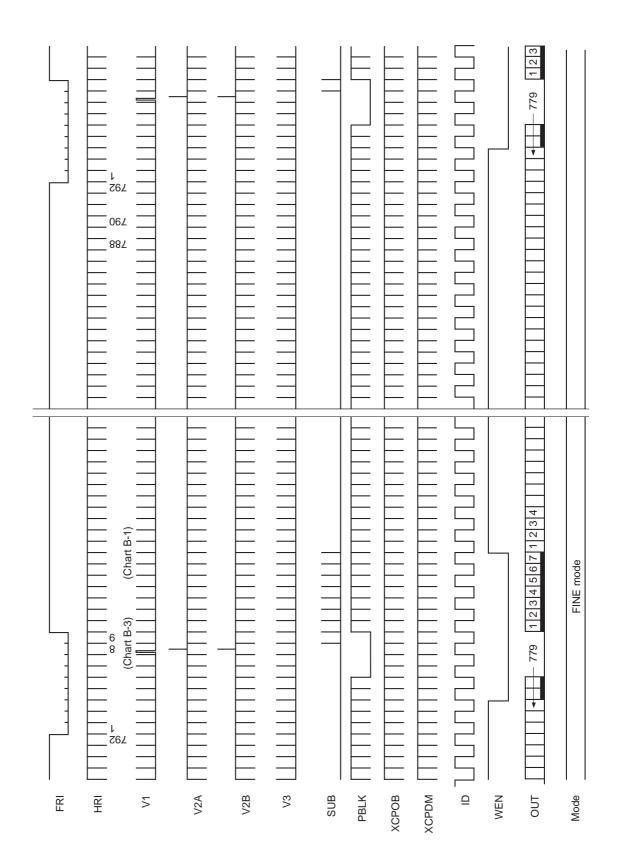

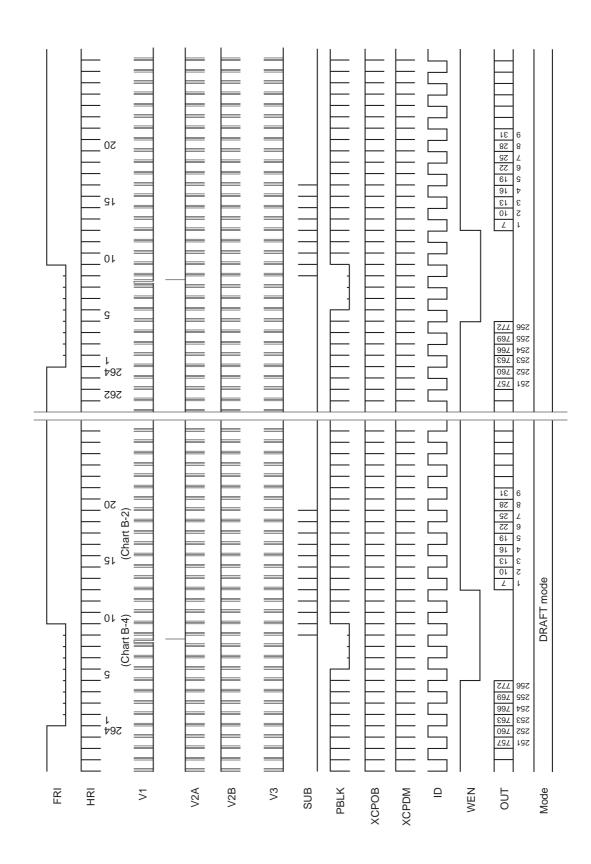

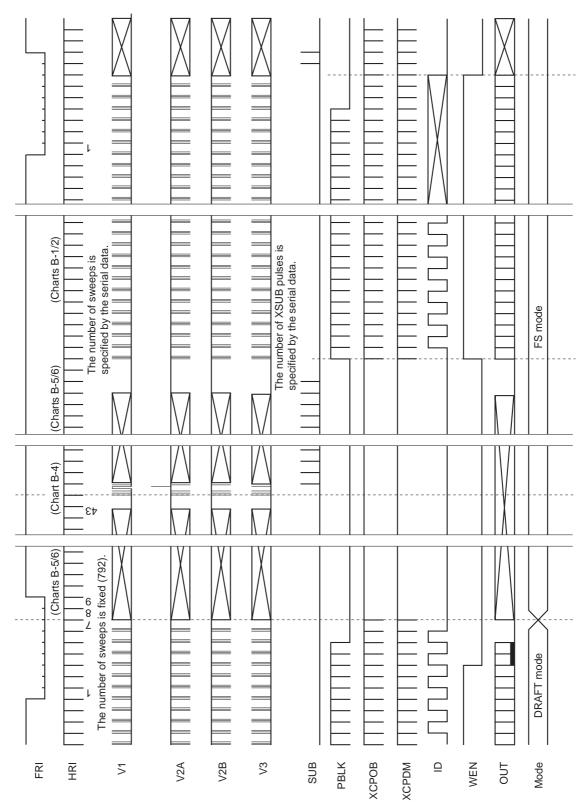

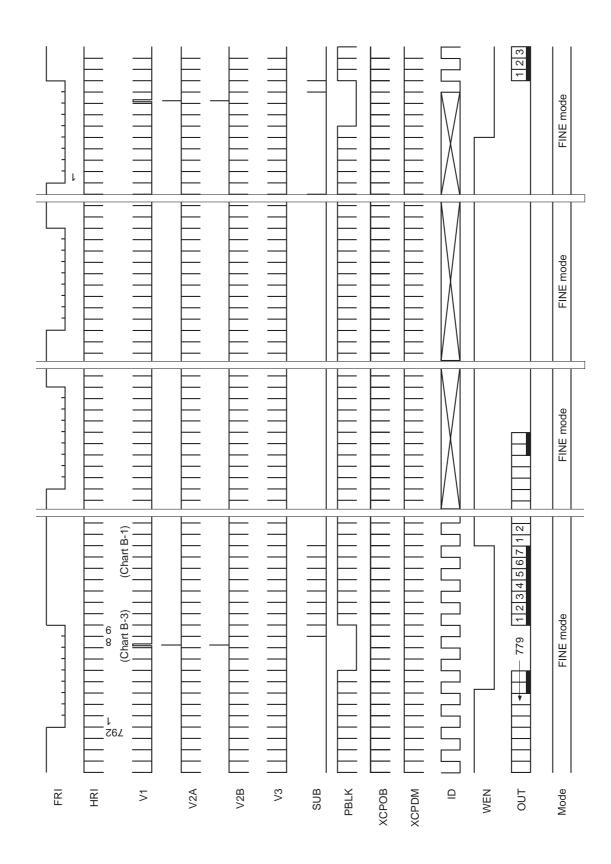

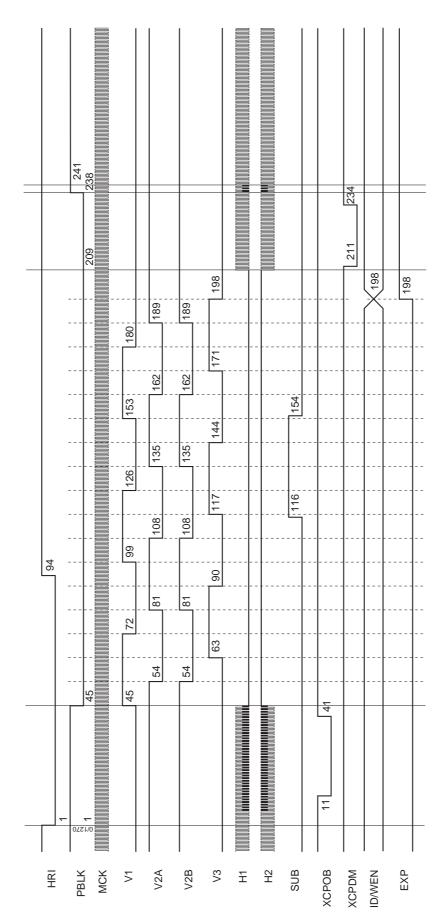

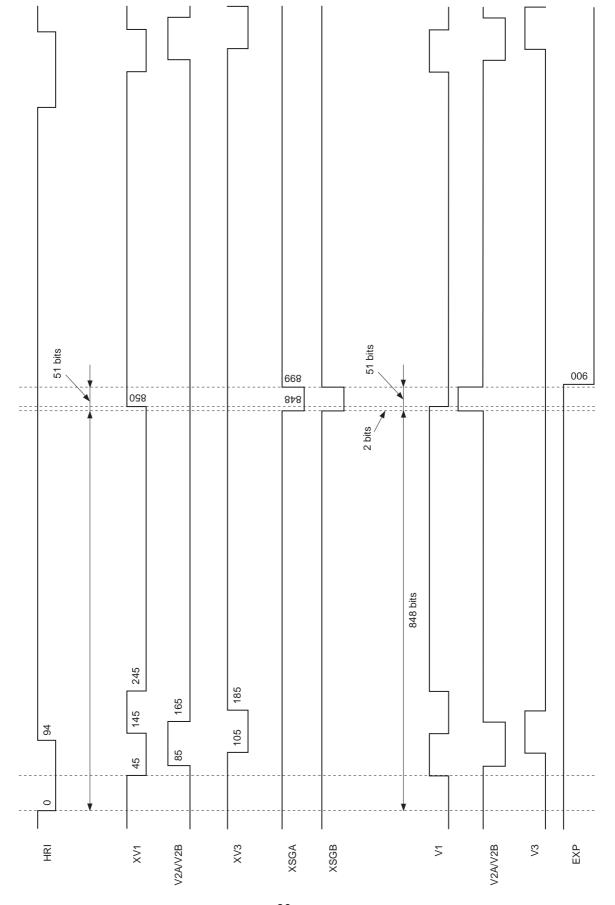

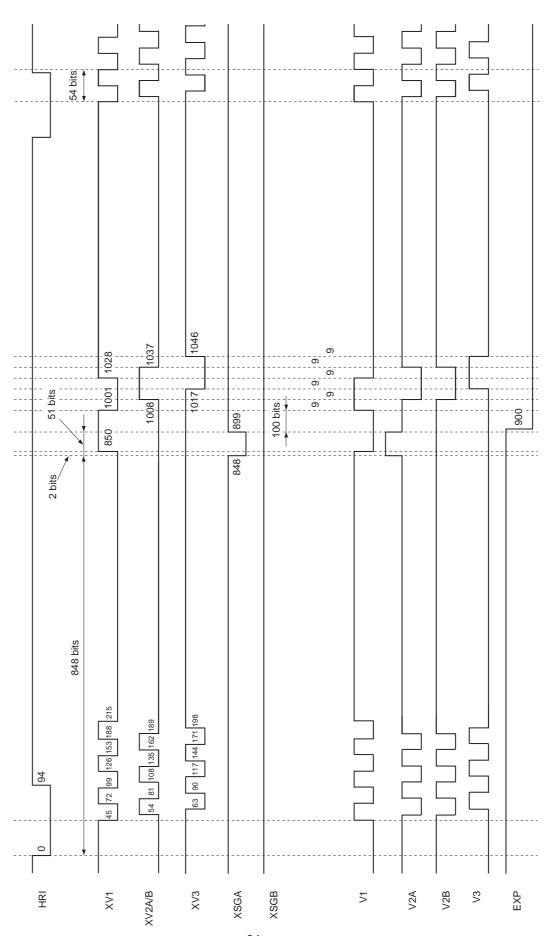

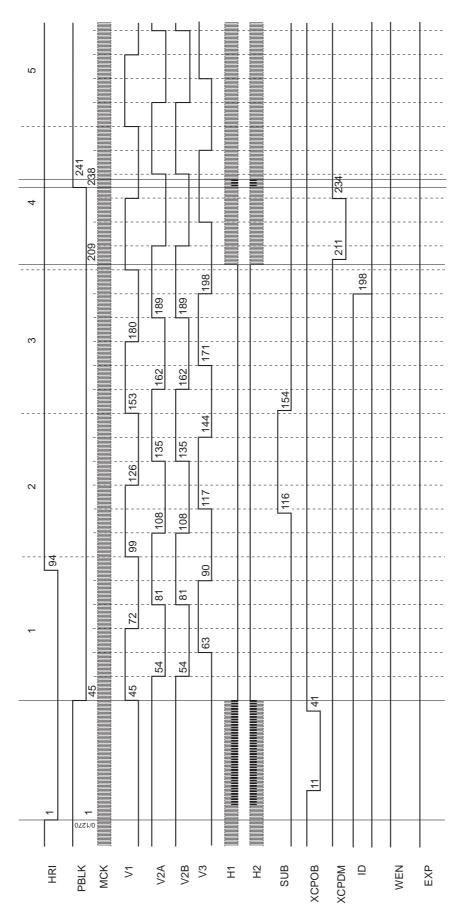

- The various drive methods possessed by the CXD2457R are shown in the Timing Charts A-1 to 4 (V rate) and B-1 to 6 (H rate).

### 2. Serial data input method

• All CXD2457R operations can be controlled via the serial interface. The serial data format is as follows.

Serial data format

#### Serial data

| Data             | Symbol        | Function                                                                                                                   |                           | When reset |

|------------------|---------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|

| D00<br>to<br>D07 | CHIP          | Chip switching                                                                                                             | See D00 to D07<br>CHIP.   | All 0      |

| D08<br>to<br>D10 | CTGRY         | Category switching                                                                                                         | See D08 to D10<br>CTGRY.  | All 0      |

| D11<br>to<br>D31 | DATA          | Control data for each category The meaning of this CTGRY control data differs according to the category set by D08 to D10. | See D11 to D31<br>DATA.   | All 0      |

| D32<br>to<br>D39 | Checksum bits | Checksum bits                                                                                                              | See D32 to D39<br>CHKSUM. | All 0      |

#### 3. Serial data and description of functions

|           | Detailed description                                                             |                                                                                                                                        |         |         |                     |         |        |         |                                    |  |  |  |  |

|-----------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------------------|---------|--------|---------|------------------------------------|--|--|--|--|

| D00<br>to |                                                                                  | The serial interface data is loaded to the CXD2457R when D00 and D07 are 1. However, this assumes that D32 to D39 CHKSUM is satisfied. |         |         |                     |         |        |         |                                    |  |  |  |  |

| D07       | D07                                                                              | D06                                                                                                                                    | D05     | D04     | D03                 | D02     | D01    | D00     | Function                           |  |  |  |  |

| CHIP      | 1                                                                                | 0                                                                                                                                      | 0       | 0       | 0                   | 0       | 0      | 1       | Loading to the CXD2457R            |  |  |  |  |

|           | This CTGRY data indicates the functions that the serial interface data controls. |                                                                                                                                        |         |         |                     |         |        |         |                                    |  |  |  |  |

| D00       | D10                                                                              | D09                                                                                                                                    | D08     |         |                     |         |        |         | Function                           |  |  |  |  |

| D08 to    | 0                                                                                | 0                                                                                                                                      | 0       | Mode    | contr               | ol data | l      |         |                                    |  |  |  |  |

| D10       | 0                                                                                | 1                                                                                                                                      | 0       | Elect   | ronic s             | hutter  | contro | l data  |                                    |  |  |  |  |

| CTGRY     | 0                                                                                | 1                                                                                                                                      | 1       | High-   | speed               | phase   | adjus  | tment   | data (Set all of D11 to D31 to 0.) |  |  |  |  |

|           | 1                                                                                | 0                                                                                                                                      | 0       | Syste   | System setting data |         |        |         |                                    |  |  |  |  |

|           | Input                                                                            | of value                                                                                                                               | es othe | er than | those               | listed  | above  | is prol | nibited.                           |  |  |  |  |

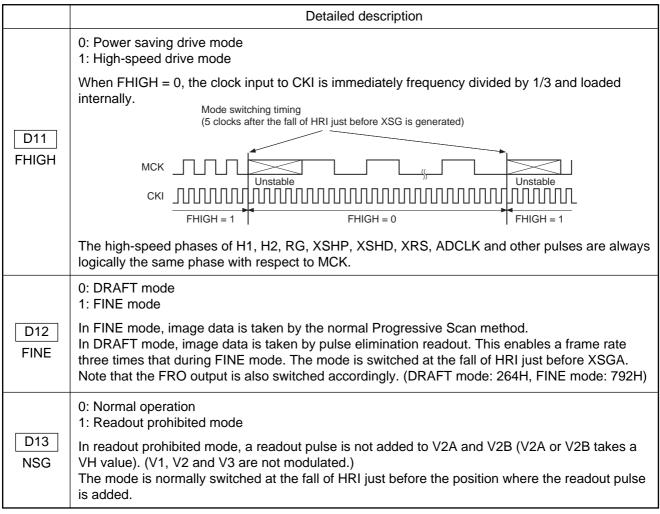

#### CTGRY: Mode control data

# **Detailed description** 0: Normal operation 1: FS mode In order to increase the frame rate, a certain portion of the captured image of CCD can be cut out by performing high-speed sweep. In FS mode, high-speed sweep is performed for the V registers of the entire image (period Z) after FRI input. Next, high-speed sweep is performed again for only the desired period (period X) after generating the XSGA pulse. Then, after performing normal V transfer and outputting the effective signal (period Y), high-speed sweep is performed for the entire image again by inputting FRI at the desired timing. This makes it possible to take only the desired portion in the V direction, thus effectively increasing the frame rate. Operation is fixed during period Z, with 22 lines swept every 1H and repeating over a 36H period. During period X, first XSGA is generated, then sweep operation starts. This period is set in serial data FVFS (system setting data: D21 to D26) in HRI units. Be sure to set FINE = 0 in this mode. D14 • When the frame rate is increased as the FS vertical effective signal Y line (example) Χ Sweep variable period (period X) Effective signal period (period Y) 1068 Sweep fixed period (period Z) Ζ Reset by FRI after Timing chart normal transfer FRI V2A 36H Set by FVFS (Fix) D15 to Set to 0. D16

D17 to D18 STB

### Detailed description

### Operation control settings

The operating mode control bits are loaded to the CXD2457R at the rise timing of the SEN input, and control is applied immediately.

| D18 | D17 | Symbol | Control mode                                                     |

|-----|-----|--------|------------------------------------------------------------------|

| 0   | 0   | CAM    | Normal operation mode                                            |

| 0   | 1   | SLP    | Sleep mode (mode for the status where CCD drive is not required) |

| 1   | Х   | STN    | Standby mode                                                     |

### Pin status during operation control

| Pin<br>No. | Symbol | CAM | SLP | STN | RST* | Pin<br>No. | Symbol | CAM | SLP | STN | RST* |

|------------|--------|-----|-----|-----|------|------------|--------|-----|-----|-----|------|

| 1          | СКО    | ACT | ACT | ACT | ACT  | 25         | MCK    | ACT | ACT | ACT | ACT  |

| 2          | Vss0   | _   | _   | _   | _    | 26         | VDD1   | _   | _   | _   | _    |

| 3          | CKI    | ACT | ACT | ACT | ACT  | 27         | 2MCK   | ACT | ACT | ACT | ACT  |

| 4          | osco   | ACT | ACT | ACT | ACT  | 28         | TEST2  | _   |     | _   | _    |

| 5          | OSCI   | ACT | ACT | ACT | ACT  | 29         | SEN    | ACT | ACT | _   | _    |

| 6          | VDD0   | _   | _   | _   | _    | 30         | SSK    | ACT | ACT | _   | _    |

| 7          | TEST1  | _   | _   | _   | _    | 31         | SSI    | ACT | ACT | _   | _    |

| 8          | AVD0   | _   | _   | _   | _    | 32         | ID     | ACT | L   | L   | L    |

| 9          | RG     | ACT | L   | L   | L    | 33         | EXP    | ACT | L   | L   | L    |

| 10         | Vss1   | _   | _   | _   | _    | 34         | HRO    | ACT | ACT | L   | L    |

| 11         | Vss2   | _   | _   | _   | _    | 35         | FRO    | ACT | ACT | L   | L    |

| 12         | H1     | ACT | L   | L   | L    | 36         | Vss4   | _   |     | _   |      |

| 13         | H2     | ACT | L   | L   | L    | 37         | HRI    | ACT | ACT |     |      |

| 14         | AVD1   | _   | _   | _   | _    | 38         | FRI    | ACT | ACT |     | _    |

| 15         | XCPDM  | ACT | L   | L   | L    | 39         | VM     | _   | _   |     | _    |

| 16         | AVD2   | _   | _   | _   | _    | 40         | V1     | ACT | VM  | VM  | VM   |

| 17         | XSHP   | ACT | L   | L   | L    | 41         | V3     | ACT | VM  | VM  | VM   |

| 18         | XSHD   | ACT | L   | L   | L    | 42         | V2A    | ACT | VH  | VH  | VH   |

| 19         | XRS    | ACT | L   | L   | L    | 43         | VH     | _   |     | _   |      |

| 20         | Vss3   | _   | _   | _   | _    | 44         | V2B    | ACT | VH  | VH  | VH   |

| 21         | PBLK   | ACT | L   | L   | L    | 45         | SUB    | ACT | VH  | VH  | VH   |

| 22         | ХСРОВ  | ACT | L   | L   | L    | 46         | VL     | _   | _   | _   | _    |

| 23         | ADCLK  | ACT | L   | L   | L    | 47         | DSGAT  | ACT | ACT | L   | L    |

| 24         | RST    | ACT | ACT | ACT | ACT  | 48         | PS     | ACT | ACT | ACT | ACT  |

$<sup>^{*}</sup>$  See "6. RST pulse" for a detailed description of RST.

Note) ACT indicates circuit operation, and L indicates "low" output level in the controlled status.

|                  | Detailed description                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| D19<br>EXPXEN    | O: The EXP pulse indicating the exposure period is generated.  1: The EXP pulse indicating the exposure period is not generated, and is constantly fixed to low.  This bit is invalid when STATUS = 1.  Note that the STB setting has priority.  The data is reflected at the rise of XSGA. |  |  |  |  |  |  |  |  |  |

| D20<br>3MCK      | O: 2MCK clock system  1: 3MCK clock system  This bit switches how MCK is comprised from the clock selected by FHIGH. Note that the waveform is unstable for 5 clocks before and after switching.                                                                                            |  |  |  |  |  |  |  |  |  |

| to D23           | Invalid data                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| D24<br>to<br>D28 | Low-speed electronic shutter setting. The value set here is the number of FR during which readout operation is not performed even if there is input. The setting range is from 0 to 31. When set to 0, readout operation is performed at the first VR. When FS = 1, this bit is invalid.    |  |  |  |  |  |  |  |  |  |

| VSHUT            | MSB LSB Function  D28 D27 D26 D25 D24 Number of FR during which readout operation is not performed                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| D29<br>to<br>D31 | Invalid data                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

# CXD2457R clock system

When using a 30MHz crystal

|       | FHIGH | змск | FINE | MCK frequency | 2MCK pin output | Frame rate |

|-------|-------|------|------|---------------|-----------------|------------|

| Mode1 | 1     | 0    | 1    | 15MHz         | 30MHz           | 15Frame/s  |

| Mode2 | 1     | 1    | 0    | 10MHz         | 15MHz           | 30Frame/s  |

| Mode3 | 0     | 0    | 0    | 5MHz          | 10MHz           | 15Frame/s  |

| Mode4 | 1     | 0    | 0    | 15MHz         | 30MHz           | 45Frame/s  |

| Mode5 | 1     | 1    | 1    | 10MHz         | 15MHz           | 10Frame/s  |

Note) Combinations of FHIGH, 3MCK and FINE other than those listed above are prohibited.

### CTGRY: Electronic shutter control data

|                  | Detailed description                                                                                          |  |  |  |  |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|

| D11 to           | High-speed electronic shutter setting. The value set here is the number of SUB pulses from FR to the next FR. |  |  |  |  |  |  |  |  |  |  |  |  |

| D20              | MSB LSB Function                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |

| HSHUT            | D20 D19 D18 D17 D16 D15 D14 D13 D12 D11 Number of SUB pulses setting                                          |  |  |  |  |  |  |  |  |  |  |  |  |

| D21<br>to<br>D31 | Input 0.                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |

High-speed and low-speed electronic shutter can be used together. Therefore, the exposure time is as follows:

FR cycle  $\times$  VSHUT + (fv – HSHUT)  $\times$  HR cycle + 745/MCK frequency [Hz] = Exposure time[second] (fv: Number of HR in 1FR)

# CTGRY: System setting data

|               | Detailed description                                                                                                                                                                                                                                                |         |              |                       |                 |        |                                       |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|-----------------------|-----------------|--------|---------------------------------------|--|--|--|

| D11<br>SGXEN  | O: Internal SSG functions operate to generate FRO and HRO.  1: Internal SSG functions are stopped, and the FRO and HRO pulses are fixed to low.  Note that the STB setting has priority. When the sync signal is input from external CXD2457R, use it at SGXEN = 1. |         |              |                       |                 |        |                                       |  |  |  |

| D12<br>EXSG   | 0: Normal operation 1: XSGA and XSGB are output from the FRO and HRO pins.  Note that the amplitude of the output pulses are Vss to Vdda.                                                                                                                           |         |              |                       |                 |        |                                       |  |  |  |

|               | These bits select the                                                                                                                                                                                                                                               | pulse   | out          | put from the ID pin.  |                 |        |                                       |  |  |  |

|               |                                                                                                                                                                                                                                                                     |         |              | D.                    | 14              |        |                                       |  |  |  |

| D13 to        |                                                                                                                                                                                                                                                                     |         |              | 0                     | 1               |        |                                       |  |  |  |

| D14           | _                                                                                                                                                                                                                                                                   | 013 -   | 0            | ID pulse output       | WEN pulse o     | utput  |                                       |  |  |  |

| IDSEL         |                                                                                                                                                                                                                                                                     |         | 1            | XSUB pulse output     | ID pulse ou     | tput   |                                       |  |  |  |

|               | XS                                                                                                                                                                                                                                                                  | SUB: I  | nvei         | rted SUB pulse outpu  | t at the amplit | ude of | Vss to Vdda                           |  |  |  |

| D15<br>VTXEN  | O: VT (readout clock) is added to V2A, V2B and V3 as normal.  1: (Readout pulse) is not added to V2A, V2B and V3.  During readout, only the modulation necessary for readout is performed.  Note that this setting has priority over mode control data NSG (D13).   |         |              |                       |                 |        |                                       |  |  |  |

| D16 CHKSUM    | 0: Checksum is not poset in the CHKSUN 1: Checksum is perfo                                                                                                                                                                                                         | M regi  | ster.        | )                     | ·               |        | er, dummy data must be esults are NG. |  |  |  |

| D17<br>STATUS | 0: The EXP pulse is of 1: High is indicated if This pulse is output a over mode control da                                                                                                                                                                          | the cl  | heck<br>rise | sum results are OK,   |                 |        | are NG.<br>This pulse has priority    |  |  |  |

| to D20        | Input 0.                                                                                                                                                                                                                                                            |         |              |                       |                 |        |                                       |  |  |  |

| D21           | These bits set the hig                                                                                                                                                                                                                                              | gh-spe  | eeds         | sweep period (unit: H | ) in FS mode.   |        |                                       |  |  |  |

| to            | MSB                                                                                                                                                                                                                                                                 |         |              | LSB                   |                 |        |                                       |  |  |  |

| D26           | D26 D25 D24 [                                                                                                                                                                                                                                                       | D23     | D22          | 2 D21                 |                 |        |                                       |  |  |  |

| FVFS          | The high-speed swee                                                                                                                                                                                                                                                 | ep is p | erfo         | rmed 22 times every   | 1H.             |        |                                       |  |  |  |

|                  | Detailed description                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| D27<br>XVCK      | 0: Normal operation 1: V1, V2 and V3 are inverted and output as XV1, XV2 and XV3. The amplitude is from VL to VM. |

| D28<br>to<br>D31 | Invalid data                                                                                                      |

### **CHKSUM**

|     | Detailed description                           |          |        |        |          |       |         |                                               |                        |  |  |  |  |

|-----|------------------------------------------------|----------|--------|--------|----------|-------|---------|-----------------------------------------------|------------------------|--|--|--|--|

|     | These are the checksum bits.                   |          |        |        |          |       |         |                                               |                        |  |  |  |  |

|     | MSI                                            | 3        |        |        |          |       |         | LSB                                           |                        |  |  |  |  |

|     | D07                                            | D06      | D05    | D04    | D03      | D02   | D01     | 000                                           |                        |  |  |  |  |

|     | D15                                            | D14      | D13    | D12    | D11      | D10   | D09     | 008                                           |                        |  |  |  |  |

| D32 | D23                                            | D22      | D21    | D20    | D19      | D18   | D17     | 016                                           |                        |  |  |  |  |

| to  | D31                                            | D30      | D29    | D28    | D27      | D26   | D25     | D24                                           | 1                      |  |  |  |  |

| D39 | +) D39                                         | D38      | D37    | D36    | D35      | D34   | D33     | $O32 \rightarrow CHKSUM$                      |                        |  |  |  |  |

| 200 | If the total = 0, the checksum results are OK. |          |        |        |          |       |         |                                               |                        |  |  |  |  |

|     | Data is not r                                  | eflected | to the | regist | ers if c | hecks | um is N | n checksum is OK.<br>S.<br>ways OK and the da | ta is reflected to the |  |  |  |  |

# 4. Shutter speed setting specifications when PS = H

When PS = H, the CXD2457R can be controlled without inputting serial data by using the SEN, SSK and SSI pins.

| Pin |                                              |             | Wh                                                                                                                                  | en L                       |   | When H |                                                                 |     |  |

|-----|----------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---|--------|-----------------------------------------------------------------|-----|--|

| SEN | FHIGH<br>(horizontal CCD<br>drive frequency) | Serial regi | sters FHI                                                                                                                           | gisters FHIGH = 1 an<br>0. | d |        |                                                                 |     |  |

| SSK | FINE (readout method)                        |             | Serial register FINE = 0 and the CXD2457R operates in DRAFT mode.  Serial register FINE = 1 and the CXD2457R operates in FINE mode. |                            |   |        |                                                                 |     |  |

| SSI | HSHUT,<br>VSHUT<br>(exposure time)           |             | SEN                                                                                                                                 | L H                        |   | SSK    | H 777 727 745 596 r: When SSI = H (1/28) r: When SSI = L (1/60) | · · |  |

Other registers hold the value input when PS = L, and assume the status indicated by STB when the RST pulse is input.

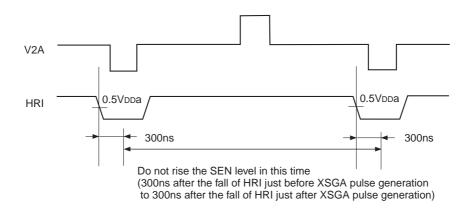

### 5. Reflective position of each data

Each serial data is reflected at the timing shown in the table below. The reflection position is the same when PS = H. When using the low-speed electronic shutter, the data is not reflected at FR where XSGA is not generated (a readout pulse is not added to V2A).

Table 5-1. Serial data reflection timing

| Data                                          | Reflection position                        |

|-----------------------------------------------|--------------------------------------------|

| Mode control data (STB)                       | SEN rise                                   |

| Mode control data (EXPXEN)                    | XSGA pulse rise                            |

| Mode control data (other than STB and EXPXEN) | HRI fall just before XSGA pulse generation |

| Electronic shutter control data               | HRI fall just after XSGA pulse generation  |

| High-speed phase adjustment data              | HRI fall just before XSGA pulse generation |

| System setting data (SGXEN)                   | SEN rise                                   |

| System setting data (other than SGXEN)        | HRI fall just before XSGA pulse generation |

#### 6. RST pulse

Setting Pin 30 to low resets the system. The serial data values after reset are as shown in the "Serial data" table.

Also, some internal circuits stop operating when RST = L. For a description of the pin status when RST = L, see the "Pin status during operation control" table given in the detailed description of STB under "3. Serial data and description of functions".

#### 7. DSGAT

DSGAT is ON when low and the CXD2457R is set to sleep mode as with SLP of STB.

Note that control is applied when either or both of DSGAT and SLP are ON. Also, when STN is ON, the CXD2457R is set to standby mode regardless of the DSGAT status.

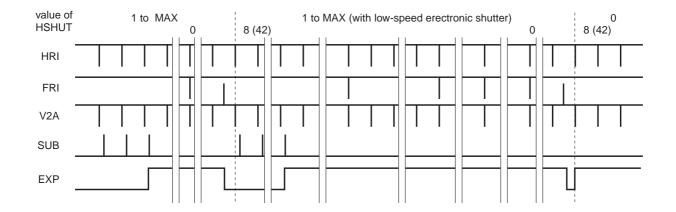

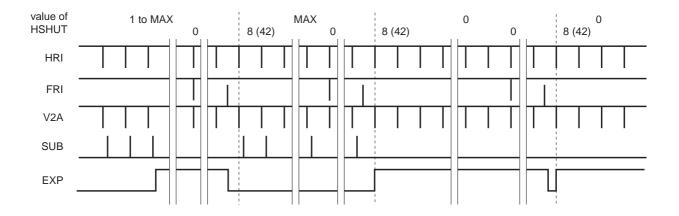

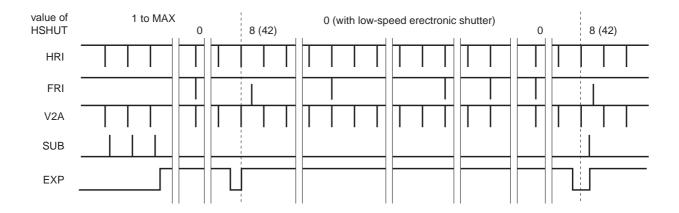

#### 8. EXP pulse

The EXP pulse indicates the exposure period.

The details are shown on the following pages.

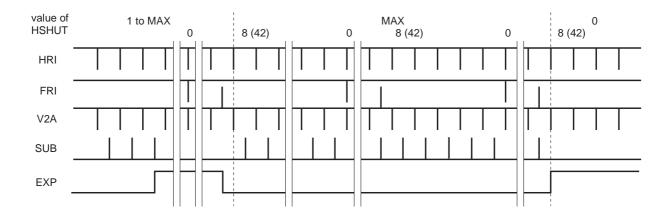

### (1) HSHUT ≥ MAX

### (2)HSHUT ≥ MAX (with low-speed erectronic shutter)

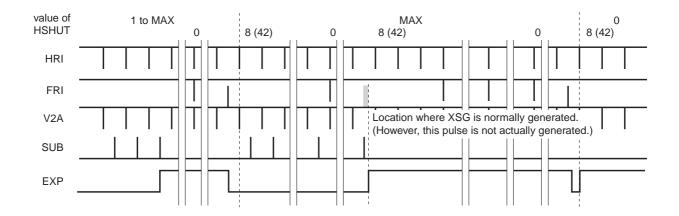

### (3) $1 \le HSHUT < MAX$

Numbers in parentheses are for FS mode.

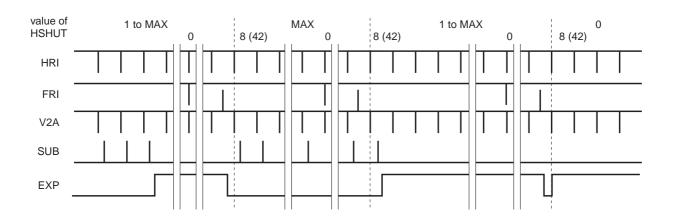

### (4) 1≤HSHUT<MAX (with low-speed erectronic shutter)

### (5) HSHUT = 0

## (6) HSHUT=0 (with low-speed erecyronic shutter)

Numbers in parentheses are for FS mode.

The mode is switched at the point where XSG is normally generated.

Chart A-4. FINE Mode (Vertical synchronization) Low-speed electronic shutter

Chart B-5. FS Mode: V clock continuous drive start (Horizontal synchronization)

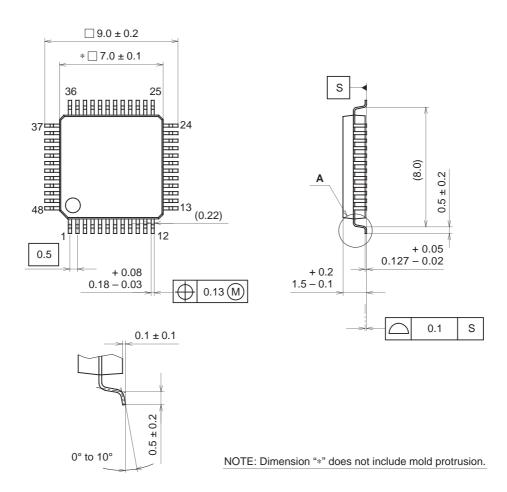

### Package Outline Unit: mm

# 48PIN LQFP (PLASTIC)

DETAIL A

| SONY CODE  | LQFP-48P-L01   |

|------------|----------------|

| EIAJ CODE  | LQFP048-P-0707 |

| JEDEC CODE |                |

### PACKAGE STRUCTURE

| PACKAGE MATERIAL | EPOXY RESIN                 |  |

|------------------|-----------------------------|--|

| LEAD TREATMENT   | SOLDER/PALLADIUM<br>PLATING |  |

| LEAD MATERIAL    | 42/COPPER ALLOY             |  |

| PACKAGE MASS     | 0.2g                        |  |