# For Immediate Assistance, Contact Your Local Salesperson

## SPECIFICATIONS

ELECTRICAL At +25°C V<sub>R8</sub> = +1.0V, V<sub>ELA</sub> = V<sub>EED</sub> = -5.2V, unless otherwise noted

|                                                                |                                                                                                                  |                |       | DAC600A      |                |           | DAC600B    | N              |                     |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------|-------|--------------|----------------|-----------|------------|----------------|---------------------|

| PARAMETER                                                      | CONDITIONS                                                                                                       | TEMP           | MIN   | TYP          | MAX            | MIN       | TYP        | MAX            | UNITS               |

| DIGITAL INPUTS                                                 |                                                                                                                  |                |       |              |                |           |            |                |                     |

| Logic                                                          | 12 Paraliel Input Lines, ECL                                                                                     |                |       |              |                |           |            |                |                     |

| Resolution<br>ECL Logic Input Levels: V <sub>IL</sub>          |                                                                                                                  | Full           | 1.48  | -1.95        | 12<br>2        |           |            |                | Bits<br>V           |

| ECL Logic input Levels: VIL                                    | Logic "0"                                                                                                        | Full           | 1.48  | -1.95        | 2              |           | ·          |                | μA                  |

| -iL<br>V <sub>81</sub>                                         | Logic "1"                                                                                                        | Full           | -1.1  | -0.75        | ō              | •         | •          | •              | v<br>v              |

| L,                                                             |                                                                                                                  | Full           |       |              | 200            |           |            | •              | μA                  |

| DIGITAL TIMING                                                 |                                                                                                                  |                |       |              |                |           | _          |                |                     |

| Input Data Rate                                                | and the second | Full           | DC    |              | 256            | •         |            | •              | MHz                 |

| CLK Pulse Width High or Low                                    |                                                                                                                  | Full           | 1.95  |              |                | •         |            |                | ns                  |

| Set-up Time                                                    |                                                                                                                  | Full           | 1.5   | 1.0          |                |           | :          |                | ps                  |

| Hold Time (Referred to CLK)<br>Propagation Delay               |                                                                                                                  | Full ·         | 1.9   | 1.7<br>2     |                |           |            |                | ns                  |

| ANALOG OUTPUT                                                  |                                                                                                                  |                |       | ۷            |                | <u> </u>  |            |                | ns                  |

| Bipolar Output Current                                         | R, = 0Ω                                                                                                          | Full           | 19    | 20           | 21             |           |            |                | mA                  |

| Output Resistance                                              | n <sub>L</sub> = 082                                                                                             | Full           | 47.5  | 50           | 52.5           | 49        | •          | 51             | Ω                   |

| Output Capacitance                                             |                                                                                                                  | Full           | 47.5  | 15           | VE.V           | -13       | •          | <b>.</b>       | pF                  |

| CONTROL AMPLIFIER                                              |                                                                                                                  |                |       |              |                |           |            |                |                     |

| Input Resistance                                               |                                                                                                                  | Fu#            |       | 800          |                |           | •          |                | Ω                   |

| Full Power Bandwidth                                           | –3dB                                                                                                             | Full           |       | 10           |                |           | •          |                | MHz                 |

| Offset                                                         |                                                                                                                  | +25°C          |       | 0            | ±1             |           | 0          | ±0.5           | mV                  |

| Input Reference Range                                          |                                                                                                                  | Full           | 100mV |              | ±1.25          | •         |            | · ·            | V                   |

| TRANSFER CHARACTERISTICS                                       |                                                                                                                  |                |       |              |                |           |            |                |                     |

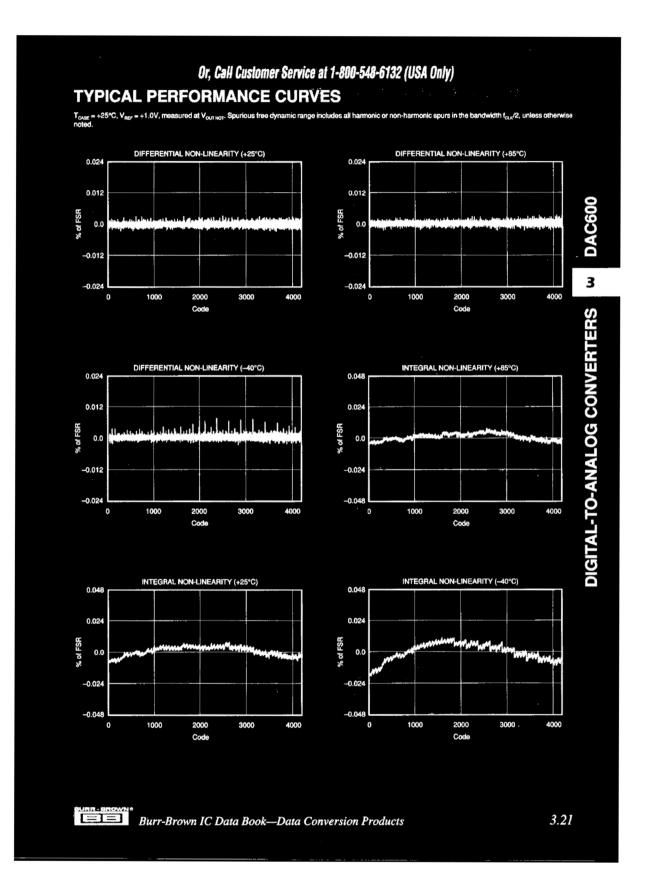

| Integral Linearity Error(1): VOUT NOT                          | Best Fit Straight Line                                                                                           | +25°C          |       | ±0.012       | ±0.024         |           | ±0.006     | ±0.012         | %FSR                |

| VOUTNOT                                                        | 5 - C                                                                                                            | Full<br>+25°C  |       | ±0.024       | ±0.036<br>±0.1 |           | ±0.012     | ±0.024<br>±0.1 | %FSR<br>%FSR        |

| Vout<br>Differential Linearity Error <sup>(1)</sup> : Vout NOT |                                                                                                                  | +25°C<br>+25°C |       |              | ±0.1<br>±0.024 |           |            | ±0.1<br>±0.012 | %FSR<br>%FSR        |

| Vout Not                                                       |                                                                                                                  | Full           |       |              | ±0.036         |           |            | ±0.024         | %FSR                |

| Vour                                                           |                                                                                                                  | +25°C          |       |              | ±0.1%          |           |            | ±0.1%          | %FSR                |

| 12-Bit Monotonicity                                            |                                                                                                                  | +25°C          | (     | Guarantee    | d              |           | Guarantee  |                |                     |

|                                                                |                                                                                                                  | Full           |       | Typical      |                | · · · · · | Guarantee  |                |                     |

| Output Offset Current: Vour Nor                                | Bits 1-12 HIGH                                                                                                   | +25°C          |       | 75           | 150            |           | 50         | 100            | μΑ                  |

| Vout NOT<br>Gain Error <sup>(2)</sup>                          |                                                                                                                  | Full<br>+25°C  |       | 57<br>±0.5   | 150<br>±1.5    |           | 50<br>±0.5 | 100<br>±1.0    | μA<br>%             |

|                                                                |                                                                                                                  | Full           |       | ±0.5<br>±1.3 | ±1.5<br>±2.0   |           | ±0.5       | ±1.0<br>±2.0   | %                   |

| Output Leakage Current                                         | VREF = 0V, Bits 1-12 LOW, VOUT NOT                                                                               | +25°C          |       | 10           | 75             |           | 5          | 50             | μÂ                  |

| TIME DOMAIN PERFORMANCE                                        |                                                                                                                  |                |       |              |                |           |            |                |                     |

| Glitch Energy                                                  | Major Carry                                                                                                      | +25°C          |       | 5.6          |                |           | •          |                | pVs                 |

| Fall Time                                                      | 90% to 10%                                                                                                       | +25°C          |       | 510          |                |           | •          |                | ps                  |

| Rise Time                                                      | 10% to 90%                                                                                                       | +25°C          |       | 770          |                |           | •          |                | ps                  |

| Settling Time <sup>(3)</sup><br>±0.1% FSR                      | Major Carry, 1 LSB Change                                                                                        | Full           |       | 4            |                |           |            |                |                     |

| ±0.1% FSR<br>±0.024% FSR                                       | Major Carry, 7 LSB Change                                                                                        | Full<br>Full   |       | 4<br>15      |                |           |            |                | ns<br>ns            |

| DYNAMIC PERFORMANCE                                            |                                                                                                                  |                |       |              |                |           |            |                | 115                 |

| Spurious Free Dynamic Range (4)                                |                                                                                                                  |                |       |              |                |           |            |                |                     |

| $t_0 = 1 \text{MHz}$                                           | f <sub>cLOCK</sub> = 50MHz                                                                                       | +25°C          |       | 74           |                | 70        | 77         |                | dBFS <sup>(3)</sup> |

| $f_0 = 10MHz$                                                  | f = 50MHz                                                                                                        | +25°C          |       | 71           |                | 65        | 73         |                | dBFS                |

| $f_0 = 1 MHz$                                                  | for our = 100MHz                                                                                                 | +25°C          |       | 72           |                | 70        | 75         |                | dBFS                |

| f <sub>o</sub> = 10MHz                                         | $f_{ct,OCK} = 100 MHz$                                                                                           | +25°C          |       | 71           |                | 66        | 70         |                | dBFS                |

| $f_0 = 20MHz$                                                  | f <sub>cLOCK</sub> = 100MHz                                                                                      | +25°C          |       | 63           |                | 59        | 62<br>70   |                | dBFS                |

| f <sub>o</sub> = 10MHz<br>f <sub>o</sub> = 20MHz               | f <sub>CLOCK</sub> = 200MHz<br>f <sub>CLOCK</sub> = 200MHz                                                       | +25°C<br>+25°C |       | 66<br>58     |                | 66<br>64  | 70<br>67   |                | dBFS<br>dBFS        |

| $f_0 = 50MHz$                                                  | f <sub>cLOCK</sub> = 200MHz                                                                                      | +25℃<br>+25℃   |       | 58           |                | 50        | 55         |                | dBFS                |

| Output Noise                                                   | Bits 1-12 HIGH                                                                                                   | +25°C          |       | 10.6         |                |           | •          |                | nV/√Hz              |

| POWER SUPPLIES                                                 |                                                                                                                  |                |       |              |                |           |            |                |                     |

| Supply Voltages: VEE                                           |                                                                                                                  | Full           | 4.5   | -5.2         | -5.5           | •         | •          | •              | v                   |

| Supply Currents: I                                             | Pins 33 and 34                                                                                                   | Full           | 30    | 46           | 60             | •         | • *        | •              | mA                  |

| EED                                                            | Pins 5 and 55                                                                                                    | Full           | 110   | 150          | 190            | •         | •          | •              | mA                  |

| Power Consumption                                              | Operating                                                                                                        | Full           |       | 900mW        | 1.3            |           | •          | •              | w                   |

| TEMPERATURE RANGE                                              |                                                                                                                  |                |       |              |                |           |            |                |                     |

| Specification: DAC600AN, BN                                    | Ambient                                                                                                          | Full           | -40   |              | +85            |           |            | •              | °C                  |

| $\theta_{\mu}$                                                 |                                                                                                                  |                |       | 30           |                |           |            |                | °C/W                |

VMEASURED (FS) -VIDEAL (FS) X 100 VIDEAL (FS) NOTES: (1) Linearity tests are measured into a virtual ground (op amp). (2) Gain error in % is calculated by: GE (%) = (3) Settling time is influenced by the load due to fast edge speeds. Use good transmission line techniques for best results. (4) Spurious free dynamic range is measured from the fundamental frequency to any harmonic or non-harm

nic spurs within the bandw "/2<sub>c</sub>, uniess

3,18

Burr-Brown IC Data Book—Data Conversion Products

## Or, Call Customer Service at 1-800-548-6132 (USA Only)

### ORDERING INFORMATION

| MODEL        | DESCRIPTION         | TEMPERATURE<br>RANGE (AMBIENT) |

|--------------|---------------------|--------------------------------|

| DAC600AN, BN | 68-Pin Plastic QUAD | 40°C to +85°C                  |

|              |                     |                                |

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>EEA</sub>                                  | 0.3 to –7       |

|---------------------------------------------------|-----------------|

| V <sub>EEA</sub>                                  | 0.3 to -7       |

| Logic Inputs                                      | 0 to -5.5V      |

| Reference Input Voltage                           | 0 to +1.25V     |

| Reference Input Current                           | 0 to 1.56mA     |

| Case Temperature                                  | 40°C to +125°C  |

| Junction Temperature                              | +150°C          |

| Storage Temperature                               | 55°C to +125°C  |

| Lead Temperature (soldering, 10s)                 | +300°C          |

| Stresses above these ratings may permanently dama | age the device. |

ELECTROSTATIC X **DISCHARGE SENSITIVITY**

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that this integrated circuit be handled and stored using appropriate ESD protection methods.

#### PACKAGE INFORMATION PACKAGE DRAW MODEL PACKAGE NUM BER DAC600AN, BN 68-Pin Plastic QUAD 312-1 NOTE: (1) For detailed drawing and dim tion table, please see end of da

**DAC600**

3

sheet, or Appendix D of Burr-Brown IC Data Book.

#### PIN DEFINITIONS

| PINIDEF |                                 |                                               |        |                           |                                                        |                   |

|---------|---------------------------------|-----------------------------------------------|--------|---------------------------|--------------------------------------------------------|-------------------|

| PIN NO  | DESIGNATION                     | DESCRIPTION                                   | PIN NO | DESIGNATION               | DESCRIPTION                                            | ()                |

| 1       | BYPASS                          | Disables Latching of Data                     | 35     | V <sub>REF2</sub><br>NC   | Analog Reference Voltage Center Tap                    | CONVERTERS        |

| 2       | CLK                             | CLOCK                                         | 36     | NC                        |                                                        | TT                |

| 3       | CLKNOT                          | CLOCKNOT                                      | 37     | NC                        |                                                        |                   |

| 4       | DGND                            | Digital Ground                                | 38     | VREF                      | Analog Reference Voltage                               |                   |

| 5       | DV <sub>ee</sub> <sup>(1)</sup> | -5.2V Supply                                  | 39     |                           | Analog Reference Voltage                               | 1.00              |

| 6       | Bit 9                           |                                               | 40     |                           |                                                        | 11                |

| 7       | Bit 10                          | • ·                                           | 41     | NC                        |                                                        |                   |

| 8       | Bit 11                          |                                               | 42     | R <sub>OFFSET</sub><br>NC | Offset Compensation                                    |                   |

| 9       | Bit 12                          | LSB                                           | 43     |                           |                                                        |                   |

| 10      | NC                              |                                               | 44     | BYPASS                    | 0.1µF Bypass to Ground                                 | Ö                 |

| 11      | NC                              |                                               | 45     | NC                        |                                                        | S                 |

| 12      | NC                              |                                               | 46     | NC                        |                                                        |                   |

| 13      | Vour                            | DAC Output                                    | 47     | ALTCOMPC                  | Control Amp PTAT Reference Compensation <sup>(2)</sup> | 6                 |

| 14      |                                 | DAC Output                                    | 48     | AGND                      | Analog Signal Ground                                   | Õ                 |

| 15      | Land                            | Ladder Ground                                 | 49     | NĆ                        |                                                        | $\sim$            |

| 16      | LGND                            | Ladder Ground                                 | 50     | LBIAS                     | Ladder Bias Alternate Compensation <sup>(2)</sup>      |                   |

| 17      |                                 | DAC Output Complement                         | 51     | NC                        |                                                        |                   |

| 18      | VOUTNOT                         | DAC Output Complement                         | 52     | NC                        |                                                        | ~                 |

| 19      | NC                              |                                               | 53     | NC                        |                                                        | 4                 |

| 20      | AGND                            | Analog Ground                                 | 54     | Bit 1                     | MSB                                                    |                   |

| 21      | NC                              |                                               | 55     | DV <sub>EE</sub><br>DGND  | Digital –5.2V Supply                                   | Ó                 |

| 22      | NC                              |                                               | 56     |                           | Digital Signal Ground                                  | Ľ                 |

| 23      | NC                              |                                               | 57     | DGND                      | Digital Signal Ground                                  |                   |

| 24      | NC                              |                                               | 58     | Bit 2                     |                                                        |                   |

| 25      | NC                              |                                               | 59     | Bit 3                     |                                                        | 4                 |

| 26      | BYPASS                          | 0.1µF Bypass to Ground                        | 60     | Bit 4                     |                                                        |                   |

| 27      | NC                              |                                               | 61     | NC                        |                                                        | DIGITAL-TO-ANALOG |

| 28      | ALTCOMPIB                       | PTAT-IB Reference Compensation <sup>(2)</sup> | 62     | Bit 5                     |                                                        | 5                 |

| 29      | AGND                            | Analog Ground                                 | 63     | DGND                      | Digital Ground                                         |                   |

| 30      | AGND                            | Analog Ground                                 | 64     | Bit 6                     |                                                        |                   |

| 31      | NC                              |                                               | 65     | Bit 7                     |                                                        |                   |

| 32      | LOOPCRNT                        | DAC Reference Alt. Loop Current               | 66     | DGND                      | Digital Ground                                         |                   |

|         |                                 | (Connect to AGND)                             | 67     | Bit 8                     |                                                        |                   |

| 33      | Veen                            | -5.2V Supply                                  | 68     | NC                        |                                                        |                   |

| 34      | Veen                            | -5.2V Supply                                  |        |                           |                                                        |                   |

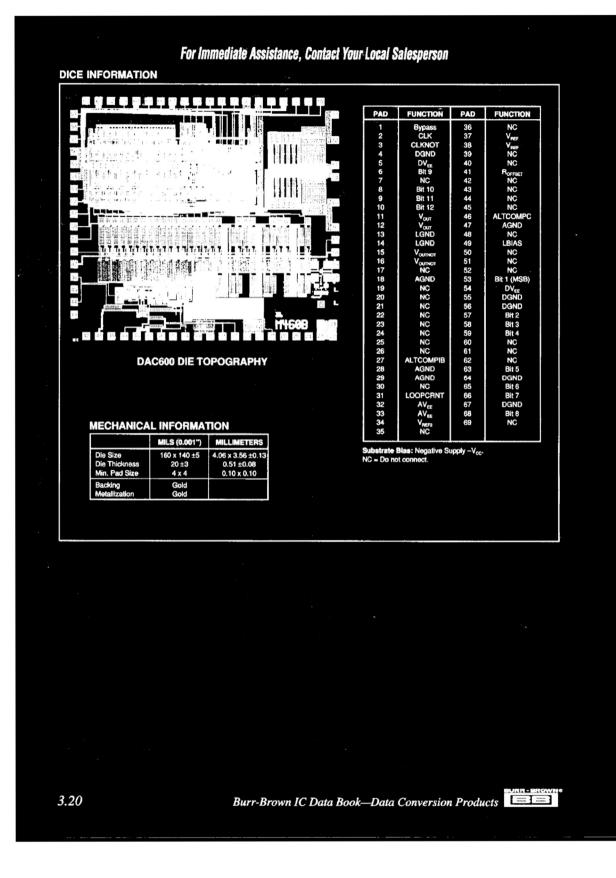

NC: no connect NOTE: (1) Pins 5 and 55 typically draw 150mA of current. Pins 33 and 34 combined typically draw 46mA. (2) Connect bypass capacitor to V<sub>ee</sub>.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

BURR-BROWN® BURR-BROWN IC Data Book—Data Conversion Products

3.19

## Or, Call Customer Service at 1-800-548-6132 (USA Only)

## THEORY OF OPERATION

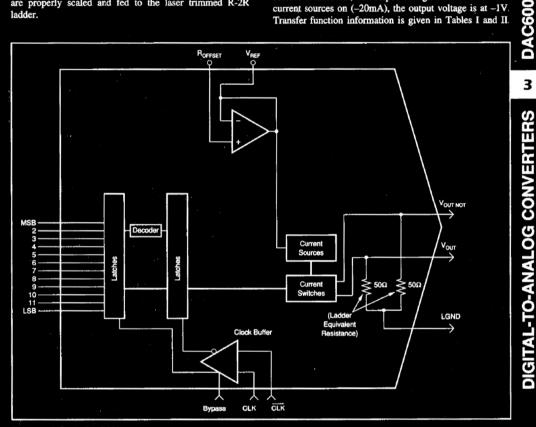

The DAC600 employs a familiar architecture where input bits switch on the appropriate current sources (Figure 1.) Bits 1-4 are decoded into 15 segments after the first set of latches. The edge triggered master-slave latches are driven by an internal clock buffer. Current sources for bits 5 and 6 are scaled down in binary fashion. These current sources are switched directly to the output of the R-2R ladder. Bits 7-12 are properly scaled and fed to the laser trimmed R-2R ladder. Decoding of bits 1-4 into 15 segments and synchronizing the data with a master/slave register reduces glitching. If the BYPASS input is low, data is transferred to the output on the positive going edge of the clock. If BYPASS is high, data is transferred to the output regardless of clock state. All digital inputs are ECL compatible.

The output current sees  $50\Omega$  of output impedance from the equivalent resistance of a R-2R ladder. With all of the current sources off, the output voltage is at 0V. With all current sources on (-20mA), the output voltage is at -1V. Transfer function information is given in Tables I and II.

FIGURE 1. Basic DAC600 Architecture.

|   |   |   |   | INPUT BITS OUTPUT VOLTAGES |   |   |   |   |    |    |    |            |                   |

|---|---|---|---|----------------------------|---|---|---|---|----|----|----|------------|-------------------|

| 1 | 2 | 3 | 4 | 5                          | 6 | 7 | 8 | 9 | 10 | 11 | 12 | Vour       | NV <sub>out</sub> |

| 0 | 0 | 0 | 0 | 0                          | 0 | C | 0 | 0 | 0  | 0  | 0  | ov         | -0.999756V        |

| 0 | 0 | 0 | 0 | 0                          | 0 | 0 | 0 | 0 | 0  | 0  | 1  | –244μV     | 0.999512V         |

|   |   |   |   |                            |   |   |   |   |    |    |    |            |                   |

|   |   |   |   |                            |   |   |   |   |    |    |    | •          |                   |

|   |   |   |   |                            |   |   |   |   |    |    |    | 1 .        |                   |

|   |   |   |   |                            |   |   |   |   |    |    |    | •          |                   |

|   |   |   |   |                            |   |   |   |   |    |    |    | •          |                   |

| 1 | 0 | 0 | 0 | 0                          | 0 | 0 | 0 | 0 | 0  | 0  | 0  | -0.5       | -0.499756         |

| 1 | 1 | 1 | 1 | 1                          | 1 | 1 | 1 | 1 | 1  | 1  | 1  | -0.999756V | 0                 |

|   |   |   |   | -                          | - |   |   |   |    |    |    |            |                   |

TABLE I. Input Code vs Output Voltage Relationships.

| BIT      | VOLTAGE (No External Load, Vour) |

|----------|----------------------------------|

| 1        | -0.5                             |

| 2        | -0.25                            |

| 3        | -0.125                           |

| 4        | -62.5mV                          |

| 5        | -31.25mV                         |

| 6        | -15.625mV                        |

| 7        | -7.8125mV                        |

| 8        | -3.9063mV                        |

| 9        | -1.9531mV                        |

| 10       | _976μV                           |

| 11       | -488µV                           |

| 12 (LSB) | 244µV                            |

TABLE II. Nominal Bit Weight Values.

Burr-Brown IC Data Book—Data Conversion Products

3.25

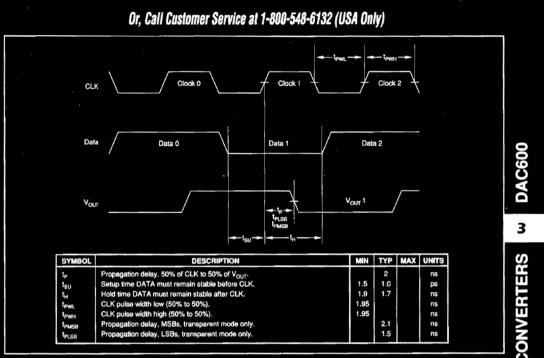

FIGURE 5. Timing Diagram.

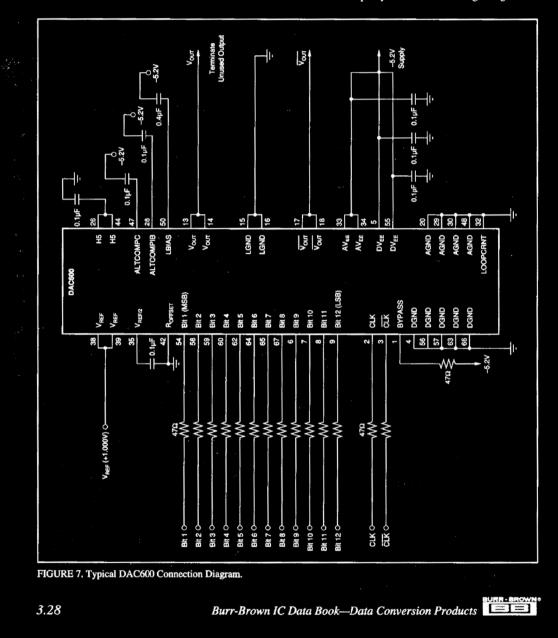

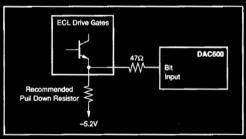

analog ground plane. For speeds of up to 256MHz, series termination with 47 $\Omega$  resistors will be adequate (Figure 6). This termination technique will greatly lessen the issue of termination currents coupling into the analog ground plane. This is shown in the typical DAC600 connection diagram (Figure 7.)

FIGURE 6. Series Bit Termination.

#### LAYOUT AND POWER SUPPLIES

A multilayer PC board with a solid ground and power planes is recommended. All of the ground pins (both analog and digital) should be connected directly to the analog ground plane at the DAC600.

Wide busses for the power paths are recommended as good general practice. External bypassing is recommended. A  $10\mu$ F ceramic capacitor in parallel with a  $0.01\mu$ F chip capacitor will be sufficient in most applications.

Burr-Brown IC Data Book-Data Conversion Products

ALTCOMPB and ALTCOMPC should be bypassed with 0.1  $\mu F$  capacitors connected to V<sub>EEA</sub>. When not used in the multiplying mode LBIAS should be bypassed with a 0.4  $\mu F$  capacitor connected to V<sub>EEA</sub>. The heat spreader (pins 26 and 44) should be bypassed with a 0.1  $\mu F$  capacitor.

#### MAXIMIZING PERFORMANCE

In addition to optimizing the layout and ground of the DAC600, there are other important issues to consider when optimizing the performance of this DAC in various AC applications.

The DAC600 includes an internal 50 $\Omega$  output impedance to simplify output interfacing to a 50 $\Omega$  load. Because some loads may be a complex impedance, care must be taken to match the output impedance with the load. Mismatching of impedances can cause reflections which will affect the measured AC performance parameters such as settling time, harmonic distortion, rise/fall times, etc. Often complex impedances can be matched by placing a variable 3 to 10pF capacitor at the output of the DAC to ground. Also, probing the output of the DAC can present a complex impedance.

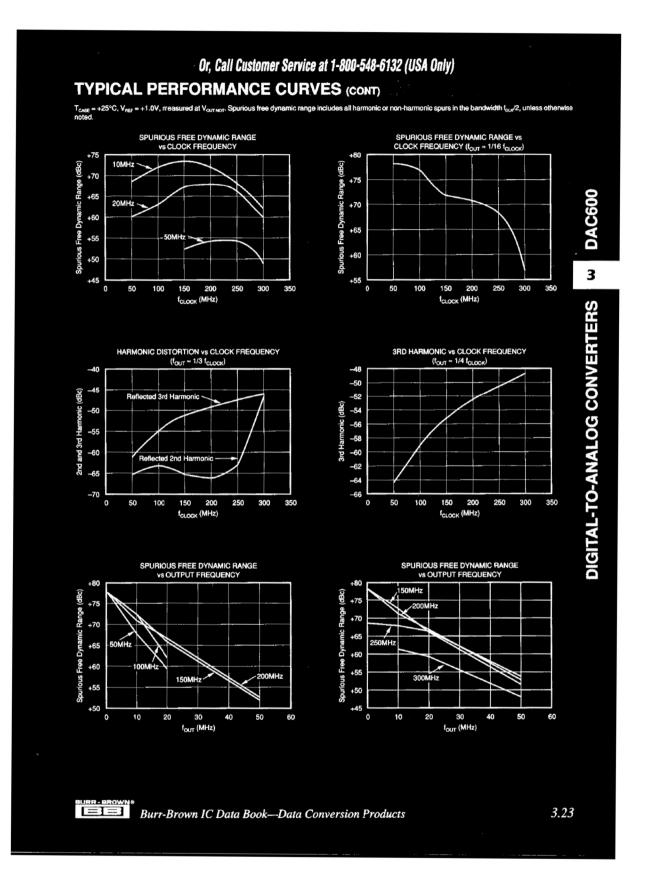

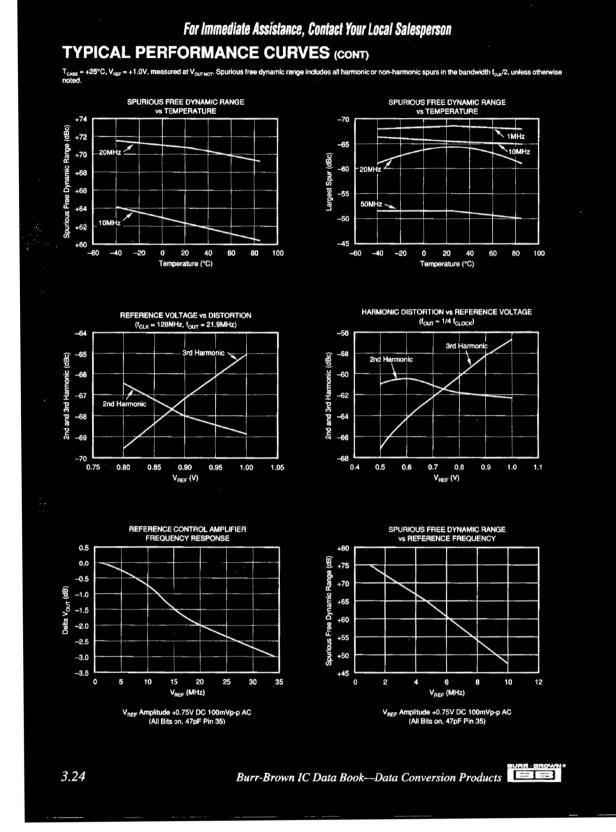

The typical performance curves of Spurious Free Dynamic Range vs various combinations of clock rate and/or input frequency should give a general idea of the spectral performance of the DAC under system specific clock and output frequencies. For variable frequency DDS and ARB applications, having a programmable frequency bandpass (smart) filter at the output of the DAC can greatly improve system

3:27

### For Immediate Assistance, Contact Your Local Salesperson

spur and noise performance by filtering out unwanted spur and noise spectra. Even with a programmable bandpass filter, care should be taken to update the DAC at greater than 4 times per cycle to (1) minimize the 2nd and 3rd harmonic magnitudes by having the output slew excessively between any successive clock and (3) to keep the 2nd harmonic and other even order harmonics from folding back close to the fundamental under the condition  $f_{OLT} = 1/3 f_{CLK}$  and (3) to keep the 3rd harmonic and other harmonics from folding back close to the fundamental under the condition  $f_{otrr}=1/4\,f_{cLK}.$  The making use of the high update rate of the DAC600 helps to lessen the problems of large harmonics "folding back" into the passband.

For DDS applications, often the DAC itself is the limit in Spurious Free Dynamic Range (SFDR) performance. However, due to the high linearity of the DAC600, low frequency spurious performance may be limited by the digital truncation error of the phase accumulator/ROM combination. Most vendors supplying a combination of phase accumulator and ROM specify the SFDR of their digital algorithm.