# DG401/883, DG403/883 DG405/883

June 1994

## **Monolithic CMOS Analog Switches**

#### **Features**

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

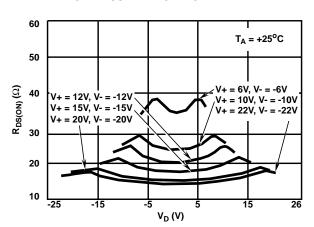

- ON-Resistance <35 $\Omega$

- Low Power Consumption (P<sub>D</sub> <35μW)

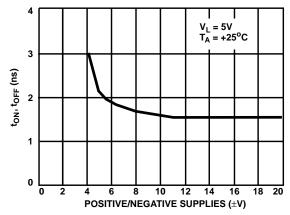

- · Fast Switching Action

- t<sub>ON</sub> <150ns</li>

- t<sub>OFF</sub> <100ns

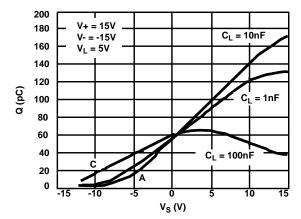

- Low Charge Injection

- DG401/883 Dual SPST; Replaces HI-5041/883

- DG403/883 Dual SPDT; Replaces DG190/883B, IH5043/883B, IH5151/883B, HI-5051/883, HI-5043/883B

- DG405/883 Dual DPST; Replaces DG184/883B, HI-5045/883, IH5145/883B

- TTL, CMOS Compatible

- Single or Split Supply Operation

## **Applications**

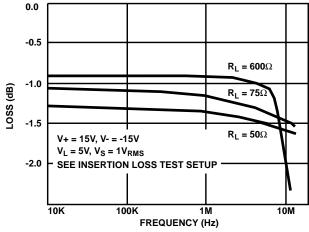

- Audio Switching

- Battery Operated Systems

- Data Acquisition

- Hi-Rel Systems

- Sample and Hold Circuits

- Communication Systems

## Description

The DG401/883, DG403/883 and DG405/883 monolithic CMOS analog switches have TTL and CMOS compatible digital inputs.

These switches feature low analog ON resistance (<35 $\Omega$ ) and fast switch time (t<sub>ON</sub> <150ns). Low charge injection simplifies sample and hold applications.

The improvements in the DG401/403/405/883 series are made possible by using a high voltage silicon-gate process. An epitaxial layer prevents the latch-up associated with older CMOS technologies. The 44V maximum voltage range permits controlling 30V peak-to-peak signals. Power supplies may be single-ended from +5V to +34V, or split from  $\pm$ 5V to  $\pm$ 17V.

The analog switches are bilateral, equally matched for AC or bidirectional signals. The ON resistance variation with analog signals is quite low over a  $\pm 15 \text{V}$  analog input range. The three different devices provide the equivalent of two SPST (DG401/883), two SPDT (DG403/883) or two DPST (DG405/883) relay switch contacts with CMOS or TTL level activation. The pinout is similar, permitting a standard layout to be used, choosing the switch function as needed.

## Ordering Information

| PART NUMBER | TEMPERATURE<br>RANGE | PACKAGE        |

|-------------|----------------------|----------------|

| DG401AK/883 | -55°C to +125°C      | 16 Lead CERDIP |

| DG403AK/883 | -55°C to +125°C      | 16 Lead CERDIP |

| DG405AK/883 | -55°C to +125°C      | 16 Lead CERDIP |

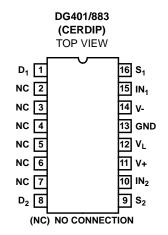

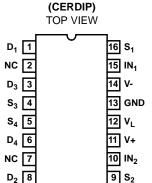

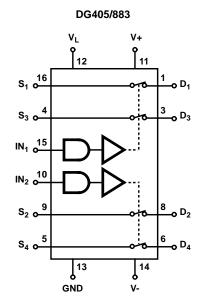

DG403/883, DG405/883

#### **Pinouts**

(NC) NO CONNECTION

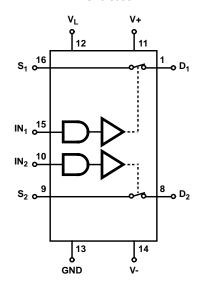

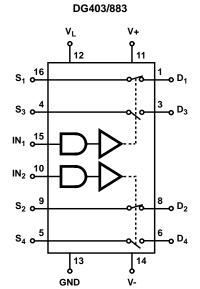

# Functional Diagrams

DG401/883

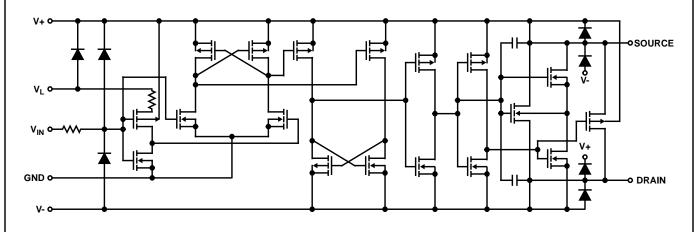

# Schematic Diagram

# Truth Table

|       | DG401/883 | DG403/883   |             | DG405/883 |

|-------|-----------|-------------|-------------|-----------|

| LOGIC | SWITCH    | SWITCH 1, 2 | SWITCH 3, 4 | SWITCH    |

| 0     | OFF       | OFF         | ON          | OFF       |

| 1     | ON        | ON          | OFF         | ON        |

NOTE: Logic "0" ≤0.8V. Logic "1" ≥2.4V.

## Specifications DG401/883, DG403/883, DG405/883

#### **Absolute Maximum Ratings Reliability Information** $\theta_{JC}$ V+ to V-.....+44.0V Thermal Resistance (Max) Operating Temperature (A Suffix) . . . . . . . . . . -55 $^{\rm o}$ C to +125 $^{\rm o}$ C Digital Inputs (Note 1), $V_S$ , $V_D$ . . . . . (V-) -2V to (V+) + 2V or 30mA, Junction Temperature (CerDIP) .....+175°C Whichever Occurs First Continuous (Any Terminal) Current, (Note 1) . . . . . . . . . ±30mA (Pulsed 1ms, 10% Duty Cycle) Storage Temperature Range (A Suffix) $\dots \dots$ -65°C to +125°C Lead Temperature (Soldering 10s).....+300°C CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

## **Operating Conditions**

| Operating Voltage Range                   | Input High Voltage2.4V Min |

|-------------------------------------------|----------------------------|

| Operating Temperature Range55°C to +125°C | Input Rise and Fall Time   |

| Input Low Voltage                         |                            |

#### TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Tested at V+ = +15V, V- = -15V,  $V_L = 5V$ , Unless Otherwise Specified

| PARAMETERS                       | SYMBOL                                     | CONDITIONS                                                      | GROUP A<br>SUBGROUP | TEMPERATURE   | LIMITS |       |       |

|----------------------------------|--------------------------------------------|-----------------------------------------------------------------|---------------------|---------------|--------|-------|-------|

|                                  |                                            |                                                                 |                     |               | MIN    | MAX   | UNITS |

| Drain-to-Source<br>ON Resistance | R <sub>DS(ON)</sub>                        | V+ = +13.5V, V- = -13.5V,<br>$I_S = -10$ mA, $V_D = \pm 10$ V   | 1                   | +25°C         | -      | 35    | Ω     |

|                                  |                                            |                                                                 | 2, 3                | +125°C, -55°C | -      | 45    | Ω     |

| Delta Drain-to-Source            | Delta                                      | $V+ = +16.5V, V- = -16.5V,$ $I_S = -10mA,$ $V_D = +5V, 0V, -5V$ | 1                   | +25°C         | -      | 3     | Ω     |

| ON Resistance                    | R <sub>DS(ON)</sub>                        |                                                                 | 2, 3                | +125°C, -55°C | -      | 5     | Ω     |

| Source OFF Leakage Current       | I <sub>S(OFF)</sub>                        | V+ = +16.5V, V- = -16.5V,                                       | 1                   | +25°C         | -      | ±0.25 | nA    |

|                                  |                                            | $V_S = -15.5V, V_D = +15.5V$                                    | 2                   | +125°C        | -      | ±20   | nA    |

|                                  |                                            | V+ = +16.5V, V- = -16.5V,                                       | 1                   | +25°C         | -      | ±0.25 | nA    |

|                                  |                                            | $V_S = +15.5V, V_D = -15.5V$                                    | 2                   | +125°C        | -      | ±20   | nA    |

| Drain OFF Leakage Current        | I <sub>D(OFF)</sub>                        | V+ = +16.5V, V- = -16.5V,<br>$V_S = -15.5V, V_D = +15.5V$       | 1                   | +25°C         | -      | ±0.25 | nA    |

|                                  |                                            |                                                                 | 2                   | +125°C        | -      | ±20   | nA    |

|                                  |                                            | $V+ = +16.5V, V- = -16.5V, V_S = +15.5V, V_D = -15.5V$          | 1                   | +25°C         | -      | ±0.25 | nA    |

|                                  |                                            |                                                                 | 2                   | +125°C        | -      | ±20   | nA    |

| Channel ON Leakage<br>Current    | I <sub>D(ON)</sub> +<br>I <sub>S(ON)</sub> | V+ = +16.5V, V- = -16.5V,<br>$V_S = V_D = \pm 15.5V$            | 1                   | +25°C         | -      | ±0.4  | nA    |

|                                  |                                            |                                                                 | 2                   | +125°C        | -      | ±40   | nA    |

| Low Level Input Current          | I <sub>IL</sub>                            | V <sub>IN</sub> Under Test = 0.8V,<br>All Others = 2.4V         | 1, 2                | +25°C, +125°C | -      | ±1.0  | μΑ    |

| High Level Input Current         | I <sub>IH</sub>                            | V <sub>IN</sub> Under Test = 2.4V,<br>All Others = 0.8V         | 1, 2                | +25°C, +125°C | -      | ±1.0  | μА    |

| Positive Supply Current          | l+                                         | V+ = 16.5V, V- = -16.5V,<br>V <sub>IN</sub> = 0V or 5.0V        | 1                   | +25°C         | -      | +1.0  | μΑ    |

|                                  |                                            |                                                                 | 2, 3                | +125°C, -55°C | -      | +5.0  | μΑ    |

| Negative Supply Current          | I-                                         | V+ = +16.5V, V- = -16.5V,<br>V <sub>IN</sub> = 0V or 5.0V       | 1                   | +25°C         | -      | -1.0  | μΑ    |

|                                  |                                            |                                                                 | 2, 3                | +125°C, -55°C | -      | -5.0  | 1     |

| Logic Supply Current             | IL                                         | V+ = +16.5V, V- = -16.5V,<br>V <sub>IN</sub> 0V or 5V           | 1                   | +25°C         | -      | +1.0  | μА    |

|                                  |                                            |                                                                 | 2, 3                | +125°C, -55°C | -      | +5.0  | 1     |

| Ground Current                   | I <sub>GND</sub>                           | V+ = +16.5V, V- = -16.5V,<br>V <sub>IN</sub> 0V or 5V           | 1                   | +25°C         | -      | -1.0  | μΑ    |

|                                  |                                            |                                                                 | 2, 3                | +125°C, -55°C | -      | -5.0  | 1     |

## Specifications DG401/883, DG403/883, DG405/883

## TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Tested at V+ = +15V, V- = -15V,  $V_L = 5V$ , Unless Otherwise Specified

|                                                 |                  |                                  | GROUP A  |               | LIMITS |     |       |

|-------------------------------------------------|------------------|----------------------------------|----------|---------------|--------|-----|-------|

| PARAMETERS                                      | SYMBOL           | CONDITIONS                       | SUBGROUP | TEMPERATURE   | MIN    | MAX | UNITS |

| Turn On Time                                    | t <sub>ON</sub>  | $R_L = 300\Omega, C_L = 35pF$    | 9        | +25°C         | -      | 150 | ns    |

|                                                 |                  |                                  | 10, 11   | +125°C, -55°C | -      | 275 | ns    |

| Turn Off Time                                   | t <sub>OFF</sub> | $R_L = 300\Omega, C_L = 35pF$    | 9        | +25°C         | -      | 100 | ns    |

|                                                 |                  |                                  | 10       | +125°C        | -      | 250 | ns    |

|                                                 |                  |                                  | 11       | -55°C         | -      | 175 | ns    |

| Break-Before-Make<br>Time Delay<br>(DG403 Only) | t <sub>D</sub>   | $R_L = 300\Omega$ , $C_L = 35pF$ | 9        | +25°C         | 10     | 150 | ns    |

#### NOTE:

#### **TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS**

Table 3 Intentionally Left Blank.

**TABLE 4. ELECTRICAL TEST REQUIREMENTS**

| MIL-STD-883 TEST REQUIREMENTS               | SUBGROUPS (SEE TABLES 1 AND 2) |  |  |

|---------------------------------------------|--------------------------------|--|--|

| Interim Electrical Parameters (Pre Burn-In) | 1                              |  |  |

| Final Electrical Test Parameters            | 1 (Note 1), 2, 3, 9, 10, 11    |  |  |

| Group A Test Requirements                   | 1, 2, 3, 9, 10, 11             |  |  |

| Groups C and D Endpoints                    | 1                              |  |  |

#### NOTE:

1. PDA applies to Subgroup 1 only.

<sup>1.</sup> Signals on  $S_X$ ,  $D_X$ , or  $IN_X$  exceeding V+ or V- will be clamped by internal diodes. Limit forward diode current to maximum current ratings.

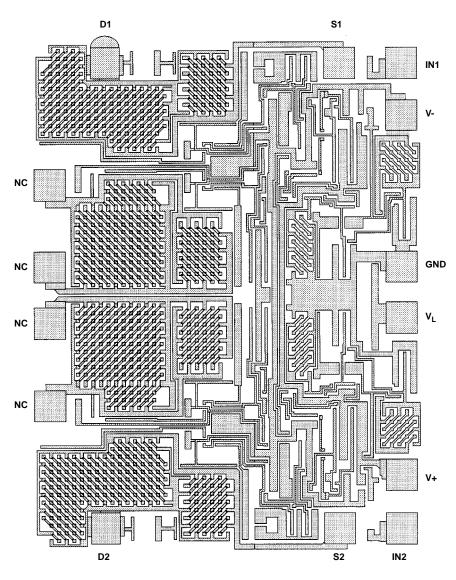

## Die Characteristics

## **DIE DIMENSIONS:**

$2150 \mu m \ x \ 1720 \mu m \ x \ 485 \pm 25 \mu m$

## **METALLIZATION:**

Type: Si - Al

Thickness: 12kÅ ± 1kÅ

## **GLASSIVATION:**

Type: Nitride

Thickness: 8kÅ ± 1kÅ

## **WORST CASE CURRENT DENSITY:**

$1.5 \times 10^5 \text{A/cm}^2$

# Metallization Mask Layout

## DG401/883

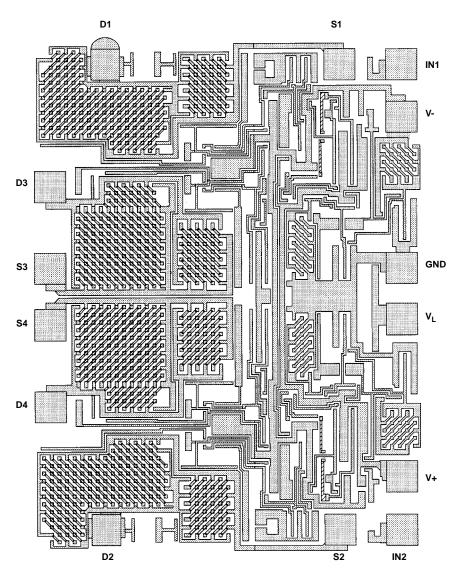

## DG403/883, DG405/883

## Die Characteristics

## **DIE DIMENSIONS:**

$2150 \mu m \ x \ 1720 \mu m \ x \ 485 \pm 25 \mu m$

## **METALLIZATION:**

Type: Si - Al

Thickness: 12kÅ ± 1kÅ

## **GLASSIVATION:**

Type: Nitride

Thickness: 8kÅ ± 1kÅ

## WORST CASE CURRENT DENSITY:

$1.5 \times 10^5 \text{A/cm}^2$

# Metallization Mask Layout

#### DG403/883, DG405/883

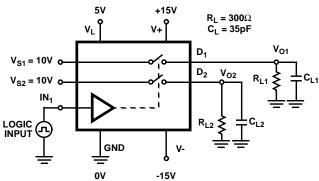

## **Test Circuits**

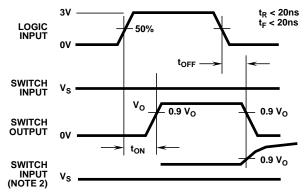

5٧ +15V  $R_L = 300\Omega$  $C_L = 35pF$ ٧o SWITCH INPUT IN₁  $R_{\mathsf{L}}$ LOGIC INPUT GND -15V

Repeat test for  $\rm IN_2$  and  $\rm S_2$  For load conditions, see Specifications.  $\rm C_L$  (includes fixture and stray capacitance)

FIGURE 1B.

$V_{O} = V_{S} \frac{L}{R_{L} + r_{DS(ON)}}$

NOTES:

- 1. Logic input waveform is inverted for switches that have the opposite logic sense.

- 2.  $V_S = 10V$  for  $t_{ON}$ ,  $V_S = -10V$  for  $t_{OFF}$ .

FIGURE 1A.

FIGURE 1. SWITCHING TIME

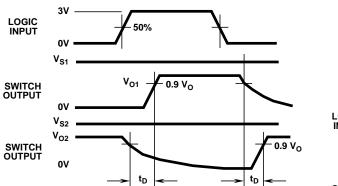

FIGURE 2A.

FIGURE 2B.

C<sub>1</sub> (includes fixture and stray capacitance)

FIGURE 2. BREAK-BEFORE-MAKE

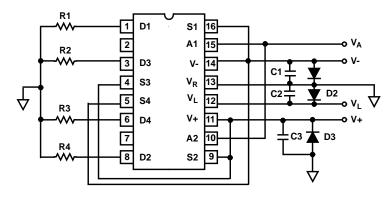

## **Burn-In Circuit**

#### DG401/883, DG403/883, DG405/883

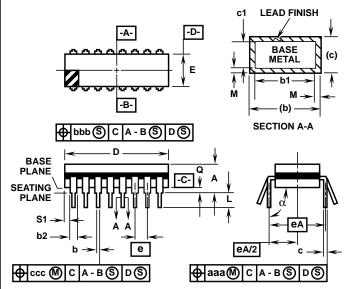

## Ceramic Dual-In-Line Frit Seal Packages (CerDIP)

#### NOTES:

- Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 3. Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b2

- This dimension allows for off-center lid, meniscus, and glass overrun.

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH.

- 11. Materials: Compliant to MIL-I-38535.

F16.3 MIL-STD-1835 GDIP1-T16 (D-2, CONFIGURATION A) 16 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

|        | INCHES |        | MILLIMETERS |       |       |

|--------|--------|--------|-------------|-------|-------|

| SYMBOL | MIN    | MAX    | MIN         | MAX   | NOTES |

| Α      | -      | 0.200  | -           | 5.08  | -     |

| b      | 0.014  | 0.026  | 0.36        | 0.66  | 2     |

| b1     | 0.014  | 0.023  | 0.36        | 0.58  | 3     |

| b2     | 0.045  | 0.065  | 1.14        | 1.65  | -     |

| b3     | 0.023  | 0.045  | 0.58        | 1.14  | 4     |

| С      | 0.008  | 0.018  | 0.20        | 0.46  | 2     |

| c1     | 0.008  | 0.015  | 0.20        | 0.38  | 3     |

| D      | -      | 0.840  | -           | 21.34 | 5     |

| Е      | 0.220  | 0.310  | 5.59        | 7.87  | 5     |

| е      | 0.100  | BSC    | 2.54 BSC    |       | -     |

| eA     | 0.300  | BSC    | 7.62 BSC    |       | -     |

| eA/2   | 0.150  | BSC    | 3.81 BSC    |       | -     |

| L      | 0.125  | 0.200  | 3.18        | 5.08  | -     |

| Q      | 0.015  | 0.060  | 0.38        | 1.52  | 6     |

| S1     | 0.005  | -      | 0.13        | -     | 7     |

| α      | 90°    | 105°   | 90°         | 105°  | -     |

| aaa    | -      | 0.015  | -           | 0.38  | -     |

| bbb    | -      | 0.030  | -           | 0.76  | -     |

| ccc    | -      | 0.010  | -           | 0.25  | -     |

| М      | -      | 0.0015 | -           | 0.038 | 2, 3  |

| N      | 16     |        | 1           | 6     | 8     |

Rev. 0 4/94

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

# DG401, DG403 DG405

## **DESIGN INFORMATION**

## **Monolithic CMOS Analog Switches**

The information contained in this section has been developed through characterization by Intersil Corporation and is for use as application and design information only. No guarantee is implied.

## **Typical Performance Curves**

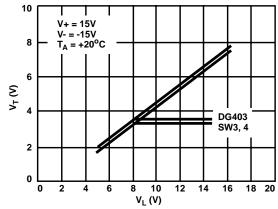

FIGURE 3. INPUT SWITCHING THRESHOLD VS LOGIC SUPPLY VOLTAGE

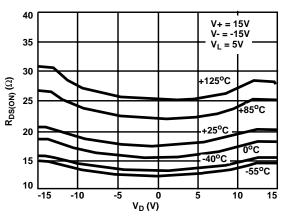

FIGURE 5.  $R_{DS(ON)}$  vs  $V_D$  AND TEMPERATURE

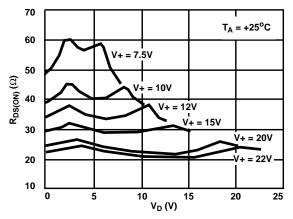

FIGURE 7. R<sub>DS(ON)</sub> vs V<sub>D</sub> AND POWER SUPPLY VOLTAGE,

FIGURE 4. INPUT SWITCHING THRESHOLD vs POWER SUPPLY VOLTAGE

FIGURE 6. R<sub>DS(ON)</sub> vs V<sub>D</sub> AND POWER SUPPLY VOLTAGE

FIGURE 8. CHARGE INJECTION vs ANALOG VOLTAGE (Vs)

# **DESIGN INFORMATION (Continued)**

The information contained in this section has been developed through characterization by Intersil Corporation and is for use as application and design information only. No guarantee is implied.

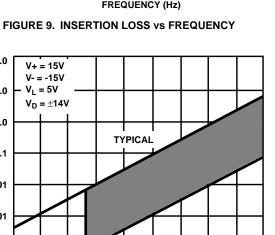

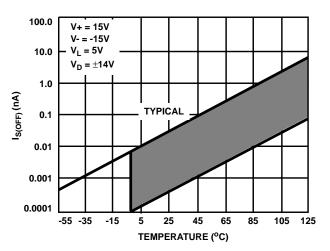

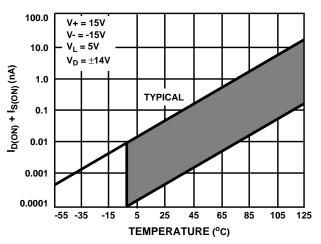

## Typical Performance Curves (Continued)

100.0

10.0

1.0

0.1

0.01

0.001

0.0001

l<sub>D(OFF)</sub> (nA)

45

TEMPERATURE (°C)

FIGURE 11.  $I_{D(OFF)}$  vs TEMPERATURE

-15

-55 -35

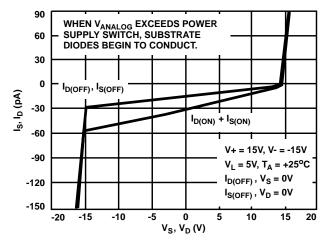

FIGURE 13. LEAKAGE CURRENT vs ANALOG VOLTAGE

FIGURE 10. I<sub>S(OFF)</sub> vs TEMPERATURE

FIGURE 12.  $I_{D(ON)} + I_{S(ON)}$  vs TEMPERATURE

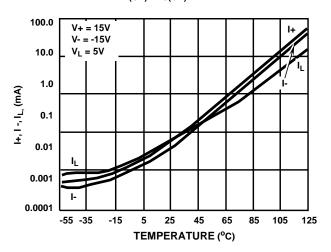

FIGURE 14. SUPPLY CURRENT vs TEMPERATURE

125

105

# **DESIGN INFORMATION (Continued)**

The information contained in this section has been developed through characterization by Intersil Corporation and is for use as application and design information only. No guarantee is implied.

## Typical Performance Curves (Continued)

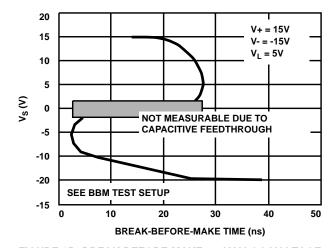

FIGURE 15. BREAK-BEFORE-MAKE vs ANALOG VOLTAGE

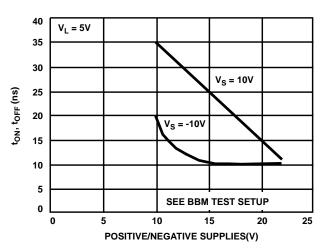

FIGURE 16. BREAK-BEFORE-MAKE vs POWER SUPPLY VOLTAGE

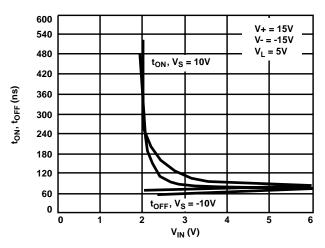

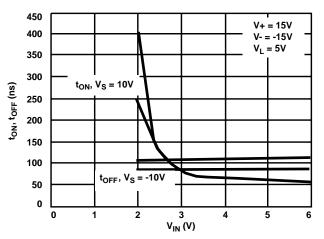

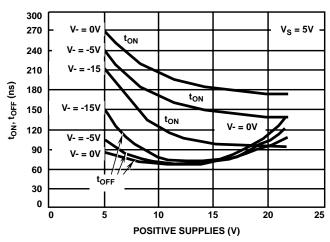

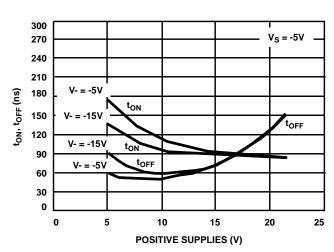

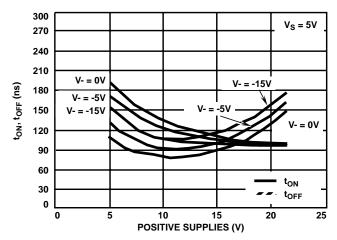

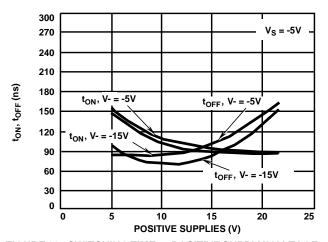

FIGURE 17. SWITCHING TIME vs INPUT LOGIC VOLTAGE ( $V_{\rm IN}$ ) REFER TO FIGURE 1 FOR TEST CONDITIONS.

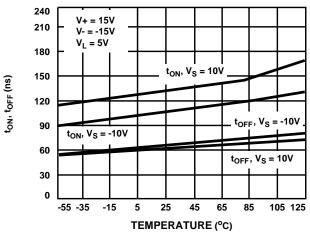

FIGURE 18. SWITCHING TIME vs TEMPERATURE, REFER TO FIGURE 1 FOR TEST CONDITIONS.

FIGURE 19. SWITCHING TIME vs ANALOG VOLTAGE, REFER TO FIGURE 1 FOR TEST CONDITIONS.

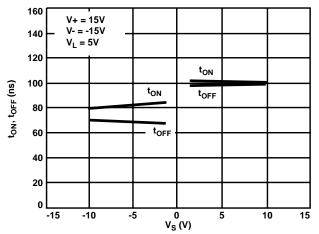

FIGURE 20. SWITCHING TIME vs INPUT LOGIC VOLTAGE ( $V_{\rm IN}$ ), REFER TO FIGURE 1 FOR TEST CONDITIONS.

# **DESIGN INFORMATION (Continued)**

The information contained in this section has been developed through characterization by Intersil Corporation and is for use as application and design information only. No guarantee is implied.

## Typical Performance Curves (Continued)

200  $V_S = 5V$  $V_L = 5V$ 180  $t_{ON}$ V<sub>S</sub> = -5V 160 ton 140  $V_S = 5V$ ton, toff (ns) 120 toff 100  $V_S = -5V$ 80 toff 60 40 20 0 10 15 25 POSITIVE/NEGATIVE SUPPLIES (V)

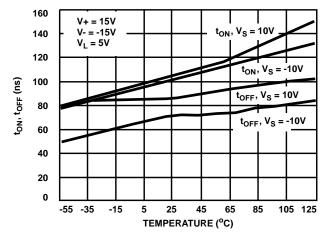

FIGURE 21. SWITCHING TIME VS TEMPERATURE, REFER TO FIGURE 1 FOR TEST CONDITIONS.

FIGURE 22. SWITCHING TIME vs POWER SUPPLY VOLTAGE, REFER TO FIGURE 1 FOR TEST CONDITIONS.

FIGURE 23. SWITCHING TIME VS POSITIVE SUPPLY VOLTAGE, REFER TO FIGURE 1 FOR TEST CONDITIONS.

FIGURE 24. SWITCHING TIME VS POSITIVE SUPPLY VOLTAGE, REFER TO FIGURE 1 FOR TEST CONDITIONS.

FIGURE 25. SWITCHING TIME VS POSITIVE SUPPLY VOLTAGE, REFER TO FIGURE 1 FOR TEST CONDITIONS.

FIGURE 26. SWITCHING TIME VS POSITIVE SUPPLY VOLTAGE, REFER TO FIGURE 1 FOR TEST CONDITIONS.