# Flip Flops, Series 54/74

## DM5474/DM7474 (SN5474/SN7474) dual D flip flops

#### general description

The DM5474/DM7474 dual D flip flops are designed for use where the flexibility of two inputs, such as on a JK or an RS flip flop, are not required. If only a single input (two logic combinations) can be utilized, then an extra input is superfluous. The DM5474/DM7474 have only a single DATA input. The logical level applied to this DATA input is transferred to the Q output when the clock pulse voltage rises to a logical 1. It is only necessary to set-up information on the DATA input several

nanoseconds before the clock pulse voltage rises; likewise it is only necessary to hold that information several nanoseconds after the clock pulse voltage reaches the logical 1 level. DATA information is then free to change in preparation for the next clock pulse. Since only one pin is used for data entry, fully asynchronous (both PRESET and CLEAR) capability can be provided in a 14 pin dual-in-line package.

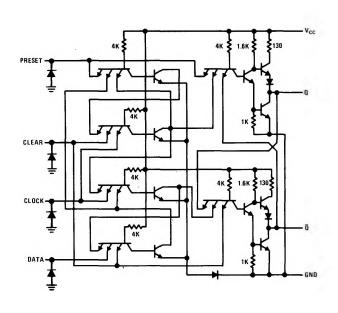

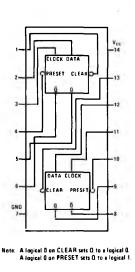

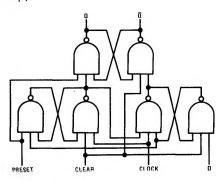

#### schematic and connection diagrams

## typical applications

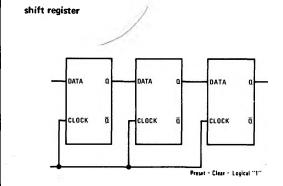

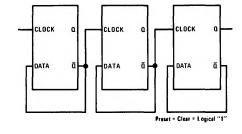

ripple counter (divide-by-2<sup>n</sup>)

# absolute maximum ratings

Supply Voltage

+7V

Input Voltage

5.5V

Fan Out

10

Storage Temperature Range

-65°C to +150°C

Operating Temperature Range

DM5474

-55°C to +125°C

DM7474

0°C to +70°C

Lead Temperature (soldering, 10 sec)

300°C

## electrical characteristics (Note 1)

| PARAMETER  Input Diode Clamp Voltage                                                  |                            | CONDITION                                                                                 |                            |                                | MIN            | TYP          | MAX          | UNITS    |

|---------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------|----------------------------|--------------------------------|----------------|--------------|--------------|----------|

|                                                                                       |                            | $V_{CC} = 5.0V$ $I_{OUT} = -12 \text{ m}$ $T_A = 25^{\circ}\text{C}$                      | ıA                         |                                | 1              |              | -1.5         | ٧        |

| Logical "1" Input<br>Voltage                                                          | DM5474<br>DM7474           | $V_{CC} = 4.5V$<br>$V_{CC} = 4.75V$                                                       |                            |                                | 2.0            |              |              | v        |

| Logical "0" Input<br>Voltage                                                          | DM5474<br>DM7474           | $V_{CC} = 4.5V$ $V_{CC} = 4.75V$                                                          |                            |                                |                |              | 0.80         | v        |

| Logical "1" Output<br>Voltage                                                         |                            | $V_{CC} = 4.5V$ $V_{CC} = 4.75V$                                                          | I <sub>OUT</sub> = -400    | μΑ                             | 2.4            | 3.3          | 0.00         | v        |

| Logical "0" Output                                                                    | DM5474                     | 45                                                                                        | I <sub>OUT</sub> = 16.0 mA |                                |                | 0.15         |              | v        |

| Logical "0" Input Current                                                             | DM7474                     | V = 5.5V                                                                                  | V <sub>IN</sub> = 0.40V    | Data or Preset                 |                | -1.0<br>-2.0 | -1.6<br>-3.2 | mA<br>mA |

| Logical "1" Input                                                                     | DM7474                     | $V_{CC} = 5.25V$ $V_{CC} = 5.5V$                                                          | V <sub>IN</sub> = 2.4V     | Clear or Clock  Data or Preset |                | -2.0         | 40.0         | μV       |

| Current  Logical "1" Input                                                            | DM7474<br>DM5474           | $V_{CC} = 5.25V$ $V_{CC} = 5.5V$                                                          |                            | Clear or Clock                 |                |              | 80.0         | μV<br>mA |

| Current Output Short Current (Note 2)                                                 | DM7474<br>DM5474<br>DM7474 | $V_{CC} = 5.3V$ $V_{CC} = 5.25V$ $V_{CC} = 5.5V$ $V_{CC} = 5.25V$                         | V <sub>OUT</sub> = 0V      |                                | -20.0<br>-18.0 |              | -55.0        | mA       |

| Power Supply Current (each flip-flop)                                                 |                            | $V_{CC} = 5.25V$ $V_{CC} = 5.0V$ $V_{IN} = 5.0V$                                          |                            |                                | -18.0          | 8.2          | 13.0         | mA       |

| Maximum Clock Frequency                                                               |                            | V <sub>CC</sub> = 5.0V<br>T <sub>A</sub> = 25°C                                           | C = 50 pF                  |                                | 15.0           | 25.0         | Į.           | MHz      |

| Propagation Delay Time to a Logical "0" from Clock $-$ t <sub>pd 0</sub>              |                            | V <sub>CC</sub> = 5.0V<br>T <sub>A</sub> = 25°C                                           | C = 50 pF                  |                                | 13.0           | 22.0         | 45.0         | ns       |

| Propagation Delay Time to a Logical "1" from Clock $ t_{pd \ 1}$                      |                            | V <sub>CC</sub> = 5.0V<br>T <sub>A</sub> = 25°C                                           | C = 50 pF                  |                                | 10.0           | 16.0         | 30.0         | ns       |

| Propagation Delay Time to a Logical "0" from Clear, or Preset - t <sub>pd 0</sub>     |                            | V <sub>CC</sub> = 5.0V<br>T <sub>A</sub> = 25°C                                           |                            |                                |                |              | 40.0         | ns       |

| Propagation Delay Time to a Logical "1" from Clear, or Preset $-$ t <sub>pd 1</sub>   |                            | V <sub>CC</sub> = 5.0V<br>T <sub>A</sub> = 25°C                                           |                            |                                |                |              | 25.0         | ns       |

| Time Prior to Clock Pulse that Data Information Must be Present — t <sub>set up</sub> |                            | $ \begin{pmatrix} V_{CC} = 5.0V \\ T_A = 25^{\circ}C \\ C = 50 \text{ pF} \end{pmatrix} $ | Logical "1"                |                                |                | 15.0         | 20.0         | ns       |

|                                                                                       |                            |                                                                                           |                            |                                |                | 15.0         | 20.0         | ns       |

| Time After Clock Pulse that Data Information Must be Held — t <sub>hold</sub>         |                            | $V_{CC} = 5.0V$ $T_A = 25^{\circ}C$                                                       | Logical "1"                | ·                              |                | -5.0         | 0            | ns       |

Note 1: Min/max limits apply across the guaranteed operating temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C for DM5474 and 0°C to 70°C for DM7474 unless otherwise specified. All typicals are given for  $V_{CC} = 5.0V$  and  $T_{A} = 25^{\circ}$ C.

Note 2: Only one output may be shorted at a time.

# typical performance characteristics

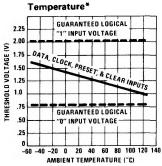

Threshold Voltage vs

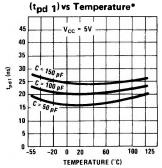

Transition Time to a Logical "1"

Transition Time to a Logical "0"

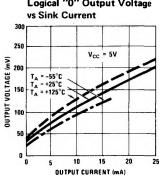

Logical "0" Output Voltage

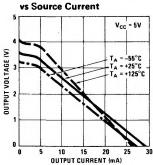

Logical "1" Output Voltage

## block diagram (each flip flop)

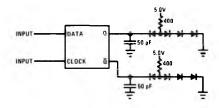

#### ac test circuit

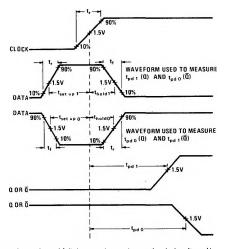

# switching time waveforms

Note: No maximum rise and fall times are imposed upon the clock voltage. However very slow transitions which allow an input to remain in the threshold region can cause noise problems.

<sup>\*</sup>Note: Curves apply to DM7474 across 0°C to +70°C range only.