# DP83251/55 PLAYER™ Device (FDDI Physical Layer Controller)

### **General Description**

The DP83251/DP83255 PLAYER device implements one Physical Layer (PHY) entity as defined by the Fiber Distributed Data Interface (FDDI) ANSI X3T9.5 Standard. The PLAYER device contains NRZ/NRZI and 4B/5B encoders and decoders, serializer/deserializer, framing logic, elasticity buffer, line state detector/generator, link error detector, repeat filter, smoother, and configuration switch.

### **Features**

- Low power CMOS-BIPOLAR process

- Single 5V supply

- Full duplex operation

- Separate management interface (Control Bus)

- Parity on PHY-MAC Interface and Control Bus Interface

- On-chip configuration switch

- Internal and external loopback

- DP83251 for single attach stations

- DP83255 for dual attach stations

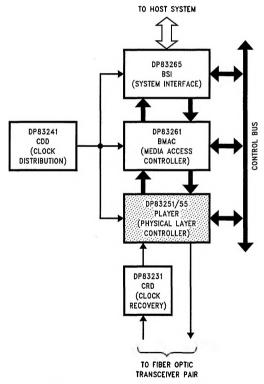

FIGURE 1-1. FDDI Chip Set Block Diagram

### **Table of Contents**

- 1.0 FDDI CHIP SET OVERVIEW

- 2.0 ARCHITECTURE DESCRIPTION

- 2.1 Overview

- 2.2 Interfaces

- 3.0 FUNCTIONAL DESCRIPTION

- 3.1 Receiver Block

- 3.2 Transmitter Block

- 3.3 Configuration Switch

- 4.0 MODES OF OPERATION

- 4.1 Run Mode

- 4.2 Stop Mode

- 4.3 Loopback Mode

- 4.4 Cascade Mode

- 5.0 REGISTERS

- 6.0 PIN DESCRIPTIONS

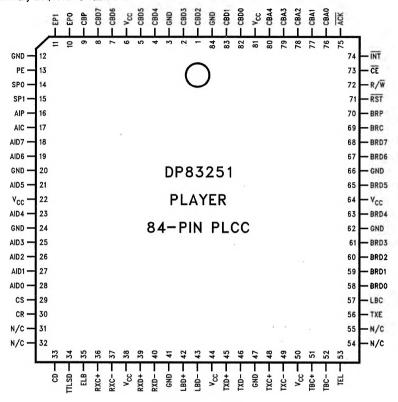

- 6.1 DP83251

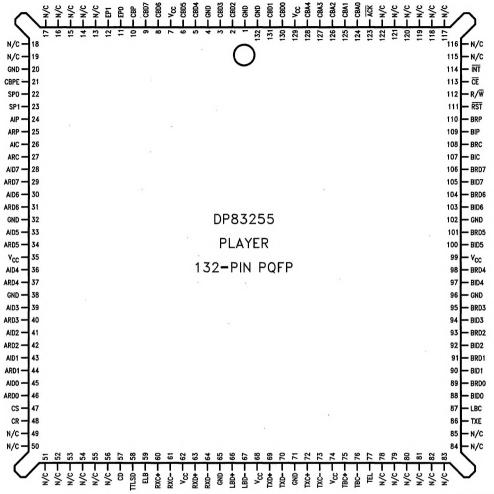

- 6.2 DP83255

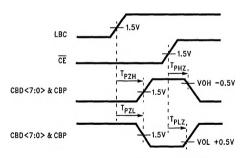

### 7.0 ELECTRICAL CHARACTERISTICS

- 7.1 Absolute Maximum Ratings

- 7.2 Recommended Operating Conditions

- 7.3 DC Electrical Charcteristics

- 7.4 AC Electrical Charcteristics

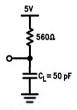

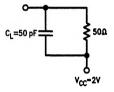

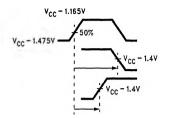

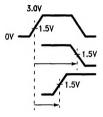

- 7.5 Test Circuits

### 8.0 DETAILED DESCRIPTIONS

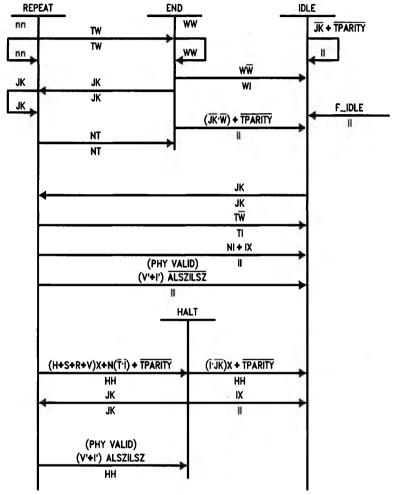

- 8.1 Framing Hold Rules

- 8.2 Noise Events

- 8.3 Link Errors

- 8.4 Repeat Filter

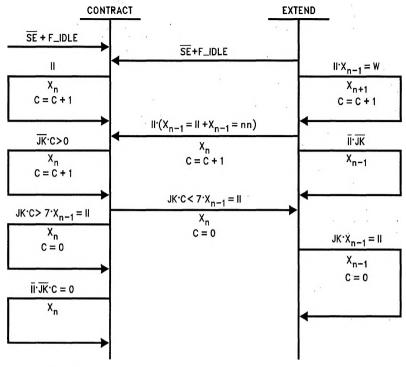

- 8.5 Smoother

- 8.6 National Byte-wide Code for PHY-MAC Interface

### 1.0 FDDI Chip Set Overview

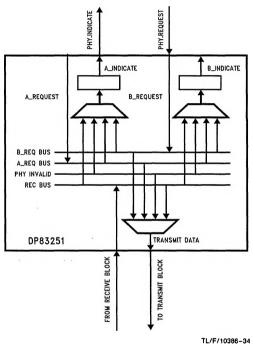

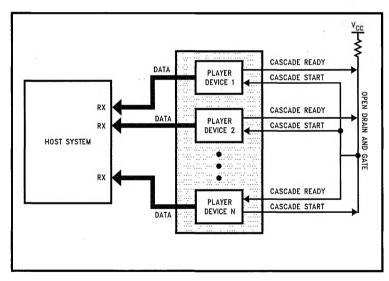

National Semiconductor's FDDI chip set consists of five components as shown in *Figure 1-1*. For more information on the other devices of the chip set, consult the appropriate datasheets and application notes.

# DP83231 CRD™ Device Clock Recovery Device

The Clock Recovery Device extracts a 125 MHz clock from the incoming bit stream.

### **Features**

- · PHY Layer loopback test

- · Crystal controlled

- Clock locks in less than 85 μs

# DP83241 CDD™ Device Clock Distribution Device

From a 12.5 MHz reference, the Clock Distribution Device synthesizes the 125 MHz, 25 MHz, and 12.5 MHz clocks required by the BSI, BMAC and PLAYER devices.

# DP83251/55 PLAYER™ Device Physical Layer Controller

The PLAYER device implements the Physical Layer (PHY) protocol as defined by the ANSI FDDI PHY X3T9.5 Standard.

### **Features**

- 4B/5B encoders and decoders

- · Framing logic

- Elasticity Buffer, Repeat Filter and Smoother

- Line state detector/generator

- · Link error detector

- Configuration switch

- Full duplex operation

- Separate management port that is used to configure and control their operation

In addition, the DP83255 contains an additional PHY\_Data.request and PHY\_Data.indicate port required for concentrators and dual attach stations.

# DP83261 BMAC™ Device Media Access Controller

The BMAC device implements the Timed Token Media Access Control protocol defined by the ANSI FDDI X3T9.5 MAC Standard.

#### **Features**

- · All of the standard defined ring service options

- Full duplex operation with through parity Supports all FDDI Ring Scheduling Classes (Synchronous, Asynchronous, etc.)

- Supports Individual, Group, Short, Long, and External Addressing

- · Generates Beacon, Claim, and Void frames internally

- · Extensive ring and station statistic gathering

- Extensions for MAC level bridging

- Separate management port that is used to configure and control their operation

- · Multi-frame streaming interface

### DP83265 BSI™ Device System Interface

The BSI device implements the interface between the BMAC device and a host system.

### **Features**

- 32-bit wide Address/Data path with byte parity

- Programmable transfer burst sizes of 4 or 8 32-bit words

- Interfaces to low cost DRAMs or directly to system bus

- · Provides 2 Output and 3 Input Channels

- · Supports Header/Info splitting

- · Efficient data structures

- · Programmable Big or Little Endian alignment

- · Full duplex data path allows transmission to self

- · Confirmation status batching services

- · Receive frame filtering services

- Operates from 12.5 MHz to 25 MHz synchronously with the host system

### 2.0 Architecture Description

### 2.1 OVERVIEW

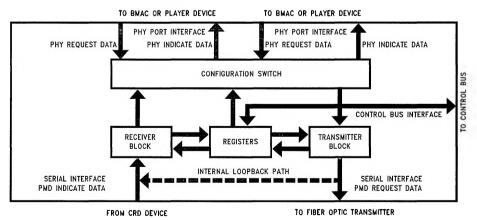

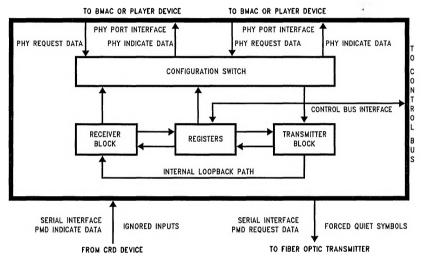

The PLAYER device is comprised of four blocks: Receiver, Transmitter, Configuration Switch and Control Bus Interface as shown in *Figure 2-1*.

#### Receiver

During normal operation, the Receiver Block accepts serial data as inputs at the rate of 125 Mbps from the Clock Recovery Device (DP83231). During the Internal Loopback mode of operation, the Receiver Block accepts data from the Transmitter Block as inputs.

The Receiver Block performs the following operations:

- Converts the incoming data stream from NRZI to NRZ, if necessary

- . Decodes the data from 5B to 4B coding

- . Converts the serial bit stream into 10-bit bytes

- Compensates for the differences between the upstream and local clocks

- Decodes Line States

- Detects link errors

Finally, the Receiver Block presents data symbol pairs (bytes) to the Configuration Switch Block

#### **Configuration Switch**

An FDDI station may be in one of three configurations: Isolate, Wrap or Thru. The Configuration Switch supports these configurations by switching the transmitted and received data paths between the PLAYER and BMAC devices.

The configuration switching is performed internally, therefore no external logic is required for this function.

#### Transmitter

The Transmiter Block accepts 10-bit bytes from the Configuration Switch.

The Transmitter Block performs the following operations:

- . Encodes the data from 4B to 5B coding.

- · Filters out code violations from the data stream.

- Generates Idle, Master, Halt, Quiet or other user defined symbol pairs upon request.

- Converts the data stream from NRZ to NRZI format ready for transmission, if necessary.

- · Provides smoothing function when necessary.

During normal operation, the Transmitter Block presents serial data to the fiber optic transmitter. While in the External Loopback mode, the Transmitter Block presents serial data to the Clock Recovery Device.

#### **Control Bus Interface**

The Control Bus Interface allows a user to:

- Program the Configuration Switch.

- Enable/disable functions within the Transmitter and Receiver Blocks (i.e., NRZ/NRZI Encoder, Smoother, PHY Request Data Parity, Line State Generation, Symbol Pair Injection, NRZ/NRZI Decoder, Cascade Mode, etc.).

The Control Bus Interface also performs the following functions:

- Monitors Line States received

- · Monitors link errors detected by the Receiver Block

- · Monitors other error conditions

#### 2.2 INTERFACES

The PLAYER device connects to external components via 5 functional interfaces: Serial Interface, PHY Port Interface, Control Bus Interface, Clock Interface, and the Miscellaneous Interface.

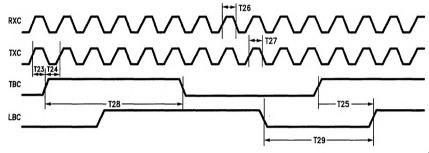

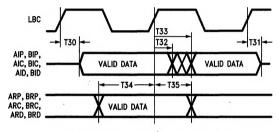

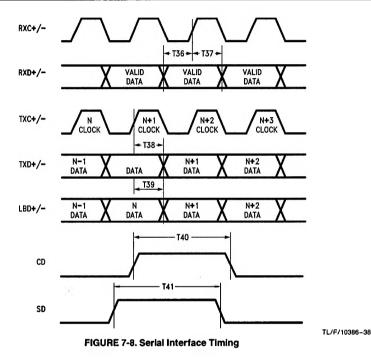

#### Serial Interface

The Serial Interface connects the PLAYER device to a fiber optic transmitter (FOTX) and the Clock Recovery Device (DP83231).

FIGURE 2-1. PLAYER Device Block Diagram

### 2.0 Architecture Description

(Continued)

### **PHY Port Interface**

The PHY Port Interface connects the PLAYER device to one or more BMAC devices and/or PLAYER devices. Each PHY Port Interface consists of two byte-wide-interfaces, one for PHY Request data input to the PLAYER device and one for the PHY Indicate data output of the PLAYER device. Each byte-wide interface consists of a parity bit (odd parity), a control bit, and two 4-bit symbols.

The DP8355 PLAYER device has two PHY Port Interfaces and the DP83251 has only one PHY Port Interface.

### **Control Bus Interface**

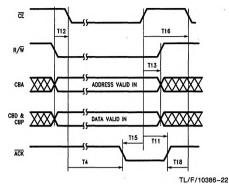

The Control Bus Interface connects the PLAYER device to a wide variety of microprocessors and microcontrollers. The Control Bus is an asynchronous interface which provides access to 32 8-bit registers.

#### **Clock Interface**

The Clock Interface consists of 12.5 MHz and 125 MHz clocks used by the PLAYER device.

The clocks are generated by either the Clock Distribution Device (CDD device) or the Clock Recovery Device (CRD device).

#### Miscellaneous Interface

The Miscellaneous Interface consists of:

- · A reset signal

- · User definable sense signals

- · User definable enable signals

- Synchronization for cascaded PLAYER devices (a highperformance non-FDDI mode)

- · CMOS power and ground, and ECL ground and power

### 3.0 Functional Description

The PLAYER Device is comprised of four blocks: Receiver, Transmitter, Configuration Switch and Control Bus Interface.

### 3.1 RECEIVER BLOCK

During normal operation, the Receiver Block accepts serial data as inputs at the rate of 125 Mbps from the Clock Receiver Device (DP83231). During the Internal Loopback mode of operation, the Receiver Block accepts data from the Transmitter Block as input.

The Receiver Block performs the following operations:

- Converts the incoming data stream from NRZI to NRZ, if necessary

- . Decodes the data from 5B to 4B coding

- Converts the serial bit stream into National byte-wide code

- Compensates for the differences between the upstream and local clocks

- Decodes Line States

- Detects link errors

Finally, the Receiver Block presents data symbol pairs to the Configuration Switch Block.

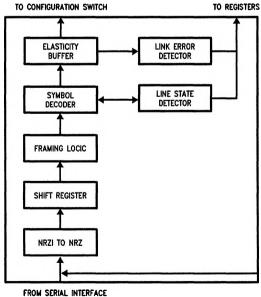

The Receiver Block consists of the following functional blocks:

NRZI to NRZ Decoder Shift Register Framing Logic Symbol Decoder Line State Detector Elasticity Buffer Link Error Detector

See Figure 3-1.

FROM TRANSMITTER BLOCK (INTERNAL LOOPBACK)

FIGURE 3-1. Receiver Block Diagram

#### NRZI TO NRZ DECODER

The NRZI to NRZ Decoder converts Non-Return-To-Zero-Invert-On-Ones data to Non-Return-To-Zero data.

This function can be enabled and disabled through bit 7 (RNRZ) of the Mode Register (MR). When the bit is cleared, it converts the incoming bit stream from NRZI to NRZ. When the bit is set the incoming NRZ bit stream is passed unchanged.

#### SHIFT REGISTER

The Shift Register converts the serial bit stream into symbol-wide data for the 5B/4B Decoder.

The Shift Register also provides byte-wide data for the Framing Logic.

### **FRAMING LOGIC**

The Framing Logic performs the Framing function by detecting the beginning of a frame or the Halt-Halt or Halt-Quiet symbol pair.

The J-K symbol pair (11000 10001) indicates the beginning of a frame during normal operation. The Halt-Halt (00100 00100) and Halt-Quiet (00100 00000) symbol pairs are detected during Connection Management (CMT).

Framing can be temporarily suspended (i.e. framing hold), in order to maintain data integrity. The Framing Hold rules are explained in Section 8.1.

### SYMBOL DECODER

The Symbol Decoder is a two level system. The first level is a 5-bit to 4-bit converter, and the second level is a 4-bit symbol pair to the NSC byte-wide code converter.

The first level latches the received 5-bit symbols and decodes them into 4-bit symbols. Symbols are decoded into two types: data and control. The 4-bit symbols are sent to the Line State Detector and the second level of the Symbol Decoder. See Table 3-1 for the 5B/4B Symbol Decoding list.

The second level translates two 4-bit symbols from the 5B/4B converter and the line state information from the Line State Detector into the National byte-wide code. More details on the National byte-wide code can be found in Section 8.6.

### LINE STATE DETECTOR

The FDDI Physical Layer (PHY) standard specifies eight Line States that the Physical Layer can transmit. These Line States are used in the Connection Management process. They are also used to indicate data within a frame during the normal operation.

The Line State Detector detects nine Line States, one more than the required Line States specified in the standard.

The Line States are reported through the Current Receive State Register (CRSR), Receive Condition Register A (RCRA), and Receive Condition Register B (RCRB).

### **Line States Description**

### **Active Line State**

The Line State Detector recognizes the incoming data to be in the Active Line State upon the reception of the Starting Delimiter (JK symbol pair).

The Line State Detector continues to indicate Active Line State while receiving data symbols, Ending Delimiter (T symbols), and Frame Status symbols (R and S) after the JK symbol pair.

### Idle Line State

The Line State Detector recognizes the incoming data to be in the Idle Line State upon the reception of 2 Idle symbol pairs nominally (plus up to 9 bits of 1 in start up cases).

Idle Line State indicates the preamble of a frame or the lack for frame transmission during normal operation. Idle Line State is also used in the handshake sequence of the PHY Connection Management process.

**TABLE 3-1. Symbol Decoding**

| Symbol        | Incoming 5B | Decoded 4B |

|---------------|-------------|------------|

| 0             | 11110       | 0000       |

| 1             | 01001       | 0001       |

| 2             | 10100       | 0010       |

| 3             | 10101       | 0011       |

| 4             | 01010       | 0100       |

| 5             | 01011       | 0101       |

| 6             | 01110       | 0110       |

| 7             | 01111       | 0111       |

| 8             | 10010       | 1000       |

| 9             | 10011       | 1001       |

| A             | 10110       | 1010       |

| В             | 10111       | 1011       |

| С             | 11010       | 1100       |

| D             | 11011       | 1101       |

| E             | 11100       | 1110       |

| F             | 11101       | 1111       |

| l (Idle)      | 11111       | 1010       |

| H (Halt)      | 00100       | 0001       |

| JK (Starting  | 11000 &     | 1101       |

| Delimiter)    | 10001       |            |

| T (Ending     | 01101       | 0101       |

| Delimiter)    |             |            |

| R (Reset)     | 00111       | 0110       |

| S (Set)       | 11001       | 0111       |

| Q (Quiet)     | 00000       | 0010       |

| V (Violation) | 00001       | 0010       |

| v             | 00010       | 0010       |

| v             | 00011       | 0010       |

| v             | 00101       | 0010       |

| v             | 00110       | 0010       |

| v             | 01000       | 0010       |

| v             | 01100       | 0010       |

| v             | 10000       | 0010       |

| V'            |             | 0011       |

| 1'            |             | 1011       |

|               |             |            |

#### Notes:

V' denotes PHY Invalid or an Elasticity Buffer stuff byte.

I' denotes Idle symbol in ILS or an Elasticity Buffer stuff byte.

### **Super Idle Line State**

The Line State Detector recognizes the incoming data to be in the Super Idle Line State upon the reception of eight consecutive Idle symbol pairs nominally (plus 1 symbol pair).

The Super Idle Line State is used to insure synchronization.

### No Signal Detect

The Line State Detector recognizes the incoming data to be in the No Signal Detect state upon the deassertion of the Signal Detect signal. No Signal Detect indicates that the incoming link is inactive.

### **Master Line State**

The Line State Detector recognizes the incoming data to be in the Master Line State upon the reception of eight consecutive Halt-Quiet symbol pairs nominally (plus up to 2 symbol pairs in start up cases).

The Master Line State is used in the handshake sequence of the PHY Connection Management process.

### **Halt Line State**

The Line State Detector recognizes the incoming data to be in the Halt Line State upon the reception of eight consecutive Halt symbol pairs nominally (plus up to 2 symbol pairs in start up cases).

The Halt Line State is used in the handshake sequence of the PHY Connection Management process.

#### **Quiet Line State**

The Line State Detector recognizes the incoming data to be in the Quiet Line State upon the reception of eight consecutive Quiet symbol pairs nominally (plus up to 9 bits of 0 in start up cases).

The Quiet Line State is used in the handshake sequence of the PHY Connection Management process.

#### **Noise Line State**

The Line State Detector recognizes the incoming data to be in the Noise Line State upon the reception of 16 noise symbol pairs.

The Noise Line State indicates that data is not received correctly. A detailed description of a noise event can be found in Section 8.2.

#### **Line State Unknown**

The Line State Detector recognizes the incoming data to be in the Line State Unknown state upon the reception of one inconsistent symbol pair (i.e. data that is not expected). This may be the beginning of a new line state.

Line State Unknown indicates that data is not received correctly. If the condition persists the noise line state may be entered.

### **ELASTICITY BUFFER**

The Elasticity Buffer performs the function of a "variable depth" FIFO to compensate for clock skews between the Receive Clock (RXC±) and the Local Byte Clock (LBC).

Bit 5 (EBOU) of the Receive Condition Register B (RCRB) is set to 1 to indicate an error condition when the Elasticity Buffer cannot compensate for the clock skews.

The Elasticity Buffer will support maximum clock skews of ±50 ppm with a maximum packet length of 4500 bytes.

To make up for the accumulation of frequency disparity between the two clocks, the Elasticity Buffer will insert or delete Idle symbol pairs in the preamble. Data is written into the byte-wide registers of the Elasticity Buffer with the Receive Clock, while data is read from the registers with the Local Byte Clock.

The Elasticity Buffer will recenter (i.e. set the read and write pointers to a predetermined distance from each other) upon the detection of a JK or every four byte times during PHY Invalid (i.e. MLS, HLS, QLS, NLS, NSD) and Idle Line State. To resolve metastability problems, the Elasticity Buffer is designed such that a given register cannot be written and read simultaneously under normal operating conditions. In a symbol-wide station, a 5-bit off boundary JK following after a maximum size frame situation may be produced which may result in a small increase in the probability of an error caused by a metastability condition.

### LINK ERROR DETECTOR

The Link Error Detector provides continuous monitoring of an active link (i.e. during Active and Idle Line States) to insure that it meets the minimum Bit Error Rate requirement as set by the standard or user to remain on the ring.

Upon detecting a link error, the internal 8-bit Link Error Monitor Counter is decremented. The start value for the Link Error Monitor Counter is programmed through the Link Error Threshold Register (LETR). When the Link Error Monitor Counter reaches zero, bit 4 (LEMT) of the Interrupt Condition Register (ICR) is set to 1. The current value of the Link Error Monitor Counter can be read through the Current Link Error Count Register (CLECR). For higher error rates the current value is an approximate count because the counter rolls over.

There are two ways to determine Link Error Rate: polling and interrupt.

#### **Polling**

The Link Error Monitor Counter is set to the value of FF. This start value is programmed through the Link Error Threshold Register (LETR).

Upon detecting a link error, the Current Link Error Counter is decremented.

The Host System reads the current value of the Link Error Monitor Counter via the Current Link Error Count Register (CLECR). The Counter is then reset to FF.

### Interrupt

The Link Error Monitor Counter is set to the value of FF. This start value is programmed through the Link Error Threshold Register (LETR).

Upon detecting a link error, the Line Error Monitor Counter is decremented. When the counter reaches zero, bit 4 (LEMT) of the Interrupt Condition Register (ICR) is set to 1, and the interrupt signal goes low.

The Host System is interrupted when the Link Error Monitor Counter reaches 0.

A state table describing Link Errors in more detail can be found in Section 8.3.

### Miscellaneous Items

When bit 0 (RUN) of the Mode Register (MR) is set to zero, or when the PLAYER device is reset through the Reset pin (RST), the Signal Detect line (TTLSD) is internally forced to zero and the Line State Detector is set to Line State Unknown.

### 3.2 TRANSMITTER BLOCK

The Transmitter Block accepts 10-bit bytes from the Configuration Switch.

The Transmitter Block performs the following operations:

- . Encodes the data from 4B to 5B coding

- Filters out code violations from the data stream

- Is capable of generating Idle, Master, Halt, Quiet, or other user defined symbol pairs

- Converts the data stream from NRZ to NRZI ready for transmission

- · Serializes data

During normal operation, the Transmitter Block presents serial data to the fiber optic transmitter.

While in the External Loopback mode, the Transmitter Block presents serial data to the Clock Recovery Device.

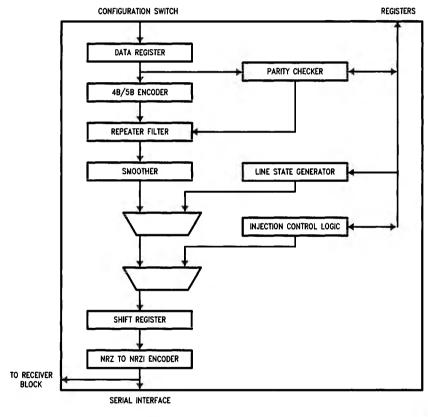

The Transmitter Block consists of the following functional blocks:

Data Registers

Parity Checker

4B/5B Encoder

Repeat Filter

Smoother

Line State Generator

Injection Control Logic

Shift Register

NRZ to NRZI Encoder

See Figure 3-2.

FIGURE 3-2. Transmitter Block Diagram

#### **DATA REGISTERS**

Data from the Configuration Switch is stored in the Data Registers. The 10-bit byte-wide data consists of a parity bit, a control bit, and two 4-bit symbols as shown in Figure 3-3.

| b9         | b8          | b7   | b0   |

|------------|-------------|------|------|

| Parity Bit | Control Bit | Data | Bits |

FIGURE 3-3. Byte-Wide Data

### **PARITY CHECKER**

The Parity Checker verifies that the parity bit in the Data Register represents odd parity (i.e. odd number of 1s).

The parity checking is enabled and disabled through bit 6 (PRDPE) of the Current Transmit State Register (CTSR).

If a parity error occurs, the Parity Checker will set bit 0 (DPE) in the Interrupt Condition Register (ICR) and report the error to the Repeat Filter.

#### **4B/5B ENCODER**

The 4B/5B Encoder converts the two 4-bit symbols from the Configuration Switch into their respective 5-bit codes. See Table 3-2 for the Symbol Encoding list.

### REPEAT FILTER

The Repeat Filter is used to prevent the propagation of code violations in data frames, to the downstream station.

Upon receiving violations in data frames, the Repeat Filter replaces them with two Halt symbol pairs followed by Idle symbols. Thus the code violations are isolated and recovered at each link and will not be propagated throughout the entire ring.

Details on Repeat Filter operation are described in Section 8.4

### **SMOOTHER**

The Smoother is used to keep the preamble length of a frame to a minimum of 6 Idle symbol pairs.

Idle symbols in the preamble of a frame may have been added or deleted by each station to compensate for the difference between the Receive Clock and its Local Clock. The preamble needs to be maintained at a minimum length to allow stations enough time to complete processing of one frame and prepare to receive another. Without the Smoother function, the minimum preamble length (6 Idle symbol pairs) may not be maintained as several stations may consecutively delete Idle symbols.

The Smoother attempts to keep the number of Idle symbol pairs in the preamble at 7 by:

Deleting an Idle symbol pair in preambles which have more than 7 Idle symbol pairs

#### and/o

Inserting an Idle symbol pair in preambles which have less than 7 idle symbol pairs (i.e. Extend State).

The Smoother Counter starts counting upon detecting an Idle symbol pair. It stops counting upon detecting a JK symbol pair.

More details on the operation of the Smoother can be found in Section 8.5.

#### LINE STATE GENERATOR

The Line State Generator allows the transmission of the PHY Request data and can also generate and transmit Idle, Master, Halt, or Quiet symbol pairs which can be used to implement the Connection Management procedures as specified in the FDDI Station Management (SMT) document.

The Line State Generator is programmed through Transmit bits 0 to 2 (TM<2:0>) of the Current Transmit State Register (CTSR).

Based on the setting of these bits, the Transmitter Block operates in the Transmit Modes where the Line State Generator overwrites the Repeat Filter and Smoother outputs. See Table 3-3 for the listing of the Transmit Modes.

TABLE 3-2. 4B/5B Symbol Encoding

| S  | ymbol      | 4B Code | Outgoing 5B |  |

|----|------------|---------|-------------|--|

|    | 0          | 0000    | 11110       |  |

|    | 1          | 0001    | 01001       |  |

|    | 2          | 0010    | 10100       |  |

|    | 3          | 0011    | 10101       |  |

|    | 4          | 0100    | 01010       |  |

| l  | 5          | 0101    | 01011       |  |

|    | 6          | 0110    | 01110       |  |

|    | 7          | 0111    | 01111       |  |

| ]  | 8          | 1000    | 10010       |  |

|    | 9          | 1001    | 10011       |  |

|    | Α          | 1010    | 10110       |  |

|    | В          | 1011    | 10111       |  |

|    | С          | 1100    | 11010       |  |

|    | D          | 1101    | 11011       |  |

|    | E          | 1110    | 11100       |  |

|    | F          | 1111    | 11101       |  |

| N  |            | 0000    | 11110 or    |  |

| 1  |            |         | 11111       |  |

| JK | (Starting  | 1101    | 11000 and   |  |

|    | Delimiter) |         | 10001       |  |

| Т  | (Ending    | 0100 or | 01101       |  |

|    | Delimiter) | 0101    |             |  |

| R  | (Reset)    | 0110    | 00111       |  |

| S  | (Set)      | 0111    | 11001       |  |

**TABLE 3-3. Transmit Modes**

| Active Transmit Mode      | Normal Transmission Mode                                                      |

|---------------------------|-------------------------------------------------------------------------------|

| Off Transmit Mode         | Transmit Quiet symbol pairs<br>and disable the Fiber Optic<br>Transmitter     |

| Idle Transmit Mode        | Transmit Idle symbol pairs                                                    |

| Master Transmit Mode      | Transmit Halt-Quiet symbol pairs                                              |

| Quiet Transmit Mode       | Transmit Quiet symbol pairs                                                   |

| Reserved Transmit<br>Mode | Reserved for future use. If selected, Quiet symbol pairs will be transmitted. |

| Halt Transmit Mode        | Transmit Halt symbol pairs                                                    |

### INJECTION CONTROL LOGIC

The Injection Control Logic replaces the data stream with a programmable symbol pair. This function is used to transmit data other than the normal data frame or Line States.

The Injection Symbols overwrite the Line State Generator (Transmit Modes) and the Repeat Filter and Smoother outputs.

These programmable symbol pairs are stored in the Injection Symbol Register A (ISRA) and Injection Symbol Register B (ISRB). The Injection Threshold Register (IJTR) determines where the Injection Symbol pair will replace the data symbols.

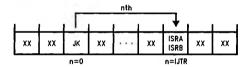

The Injection Control Logic is programmed through the bits 0 and 1 (IC<1:0>) of the Current Transmit State Register (CTSR) to one of the following Injection Modes (see *Figure 3-4*):

- 1. No Injection (i.e. normal operation)

- 2. One Shot

- 3. Periodic

- 4. Continuous

In the No Injection mode, the data stream is transmitted unchanged.

In the One Shot mode, ISRA and ISRB are injected once on the nth byte after a JK, where n is the programmed value specified in the Injection Threshold Register.

In the Periodic mode, ISRA and ISRB are injected every nth symbol.

In the Continuous mode, all data symbols are replaced with the contents of ISRA and ISRB. This is the same as periodic mode with IJTR = 0.

### SHIFT REGISTER

The Shift Regiser converts encoded parallel data to serial data. The parallel data is clocked into the Shift Register by the Transmit Byte Clock (TBC±), and clocked out by the Transmit Bit Clock (TXC±).

### **NRZ TO NRZI ENCODER**

The NRZ to NRZI Encoder converts the serial Non-Return-To-Zero data to Non-Return-To-Zero-Invert-On-One data.

This function can be enabled and disabled through bit 6 (TNRZ) of the Mode Register (MR). When programmed to "0", it converts the bit stream from NRZ to NRZI. When programmed to "1", the bit stream is transmitted NRZ.

### One Shot (Notes 1, 3)

TL/F/10386-5

### Periodic (Notes 2, 3)

TL/F/10386-6

### Continuous (Note 3)

|              |              |                  |              |              | 1            |

|--------------|--------------|------------------|--------------|--------------|--------------|

| ISRA<br>ISRB | ISRA<br>ISRB | <br>ISRA<br>ISRB | ISRA<br>ISRB | ISRA<br>ISRB | ISRA<br>ISRB |

|              |              | <br>             |              |              |              |

TL/F/10386-33

#### Where

ISRA: Injection Symbol Register A ISRB: Injection Symbol Register B

IJTR: Injection Threshold Register

Note 1: In one shot when n+0 the JK is replaced. Note 2: In periodic when n=0 all symbols are replaced.

Note 3: Max value on n = 255.

FIGURE 3-4. Injection Modes

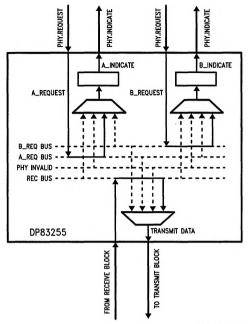

### 3.3 CONFIGURATION SWITCH

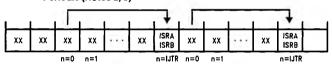

The Configuration Switch consists of a set of multiplexors and latches which allow the PLAYER device to configure the data paths without the need of external logic. The Configuration Switch is controlled through the Configuration Register (CR).

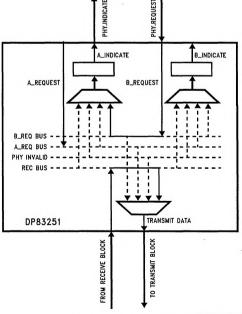

The Configuration Switch has four internal buses, the A\_Request bus, the B\_Request bus, the Receive bus, and the PHY\_Invalid bus. The two Request buses can be driven by external input data connected to the external PHY Port Interface. The Receive bus is internally connected to the Receive Block of the PLAYER device, while the PHY\_Invalid bus has a fixed 10-bit LSU pattern, useful during the connection process. The configuration switch also has three internal multiplexors, each can select any of the four buses to connect to its respective data path. The first two are

HY.INDICATE HY.INDICATE PHY.REQUEST HY.REQUEST A INDICATE R INDICATE A\_REQUEST B\_REQUEST B\_REQ BUS A\_REQ BUS PHY INVALID REC BUS DP83255 TRANSMIT DATA TRANSMIT BLOCK RECEIVE BLOCK FROM 2

TL/F/10386-7

FIGURE 3-5a. Configuration Switch Block

Diagram for DP83255

PHY Port Interface output data paths, A\_Indicate and B\_Indicate, that can drive output data paths of the external PHY Port Interface. The third output data path is connected internally to the Transmit Block.

The Configuration Switch is the same on both the DP83251 device and the DP83255 device. However, the DP83255 has two PHY Port interfaces connected to the Configuration Switch, whereas the DP83251 has one PHY Port Interface. The DP83255 uses the A\_Request and A\_Indicate paths as one PHY Port Interface and the B\_Request and B\_Indicate paths as the other PHY Port interface (see *Figure 3-5a*). The DP83251, having only one port interface, uses the B\_Request and A\_Indicate paths as its external port. The A\_Request and B\_Indicate paths of the DP83251 are null connections and are not used by this device (see *Figure 3-5b*).

FIGURE 3-5b. Configuration Switch Block

Diagram for DP83251

### STATION CONFIGURATIONS

### Single Attach Station (SAS)

The Single Attach Station can be connected to either the Primary or Secondary ring via a Concentrator. Only 1 MAC is needed in a SAS.

Both the DP83251 and DP83255 can be used in a Single Attach Station. The DP83251 can be connected to the MAC via its only PHY Port Interface. The DP83255 can be connected to the MAC via either of the 2 PHY Port Interfaces. See *Figures 3-6* and *3-7*.

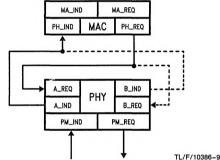

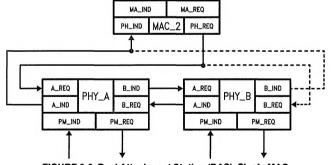

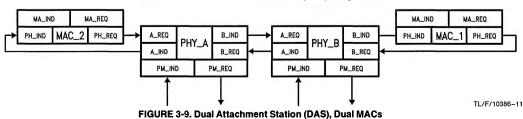

### **Dual Attach Station (DAS)**

A Dual Attach Station can be connected directly to the dual ring. There are two types of Dual Attach Stations: DAS with a Single MAC and DAS with Dual MACs. See *Figures 3-8* and *3-9*.

Although two DP83251s can be connected together to build a Dual Attach Station, it is recommended that the DP83255 is to be used for this type of station configuration.

A DAS with Single MAC can be configured as follows:

- B\_Indicate data of PHY\_A is connected to A\_Request input of PHY\_B. B\_Request input of PHY\_A is connected to A\_Indicate output of PHY\_B.

- The MAC can be connected to either the A\_Request input and the A\_Indicate output of PHY\_A or the B\_Request input and the B\_Indicate output of PHY\_B.

The DAS with Dual MACs can be configured as follows:

- B\_Indicate data of PHY\_A is connected to A\_Request input of PHY\_B. B\_Request input of PHY\_A is connected to A\_Indicate output of PHY\_B.

- The MAC\_1 is connected to the B\_Indicate output and the B\_Request Input of PHY\_B.

- The MAC\_2 is connected to the A\_Indicate output and the A\_Request Input of PHY\_A.

FIGURE 3-6. Single Attach Station Using the DP83251

FIGURE 3-7. Single Attachment Station (SAS)

Using the DP83255

FIGURE 3-8. Dual Attachment Station (DAS), Single MAC

### **CONCENTRATOR CONFIGURATIONS**

There are 2 types of Concentrators: Single Attach and Dual Attach. These Concentrators can be designed with or without the MAC(s). Its configuration is determined based upon its type and the number of active MACs in the Concentrator. Using the PLAYER devices, a Concentrator can be built with many different configurations without the need of any external logic.

Both the DP83251 and DP83255 can be used to build a Single Attach Concentrator. Only the DP83255 is recommended for the Dual Attach Concentrator design.

See Application Note 675, Designing FDDI Concentrators and Application Note 741, Differentiating FDDI Concentrators for futher information.

#### Concepts

A Concentrator is comprised of 2 parts: the Dual Ring Connect portion and the Master Ports.

The Dual Ring Connection portion connects the Concentrator to the dual ring directly or to another Concentrator. If the Concentrator is connected directly to the dual ring, it is a part of the "Dual Ring Tree". If the Concentrator is connected to another Concentrator, it is a "Branch" of the "Dual Ring Tree".

The Master Ports connect the Concentrator to its "Slaves". A Slave could be a Single Attach Station or another Concentrator (thus forming another Branch of the Dual Ring Tree).

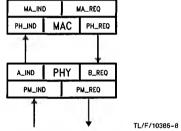

When a MAC in a concentrator is connected to the Primary or Secondary Ring, it is required to be situated at the exit port of that concentrator (i.e. its PH\_IND is connected to the IND Interface of the last Master Port in the Concentrator (PHY\_M n) that is connected to that ring).

A Concentrator can have two MACs connected to both the Primary and Secondary rings. In addition, a Roving MAC can be included in the Concentrator configuration. A Roving MAC can be used to test the stations connected to the Concentrator before allowing them to join the Dual Ring. This may require external multiplexers.

#### **Single Attach Concentrator**

A Single Attach Concentrator is a Concentrator that has only one PHY at the Dual Ring Connect side. It cannot, therefore, be connected directly to the Dual Ring. A Single Attach Concentrator is a Branch to the Dual Ring Tree. It is connected to the ring as a Slave of another Concentrator.

Multiple Single Attach Concentrators can be connected together hierarchically to build multiple levels of branches in a Dual Ring.

The Single Attach Concentrator can be connected to either the Primary or Secondary ring depending on the connection with its Concentrator (the Concentrator that it is connected to a slave).

Figure 3-10 shows a Single Attach Concentrator with a Single MAC.

### **Dual Attach Concentrator**

A Dual Attach Concentrator is a Concentrator that has two PHYs at the Dual Ring Connect side. It is connected directly to the dual ring and is a part of the Dual Ring Tree.

The Dual Attach Concentrator is connected to both the Primary and Secondary rings.

### **Dual Attach Concentrator with Single MAC**

Figure 3-11 shows a Dual Attach Concentrator with a Single MAC.

Because the Concentrator has one MAC, it can only transmit and receive frames on the ring where the MAC is connected. The Concentrator can only repeat frames on the other ring.

### **Dual Attach Concentrator with Dual MACs**

Figure 3-12 shows Dual Attach Concentrator wih Dual MACs.

Because the Concentrator has two MACs, it can transmit and receive frames on both the Primary and Secondary rings.

#### 3.0 Functional Description (Continued) PM\_REQ PM\_IND B\_REQ A\_IND PHY\_S B\_IND MAC PH\_IND A\_REQ PH\_REQ MA\_REQ MA\_IND B\_IND A\_REQ B\_IND A\_REQ B\_IND A\_REQ B\_IND PHY\_M PHY\_M PHY M PHY\_M A\_IND B\_REQ A\_IND B\_REQ A\_IND B\_REQ A\_IND B\_REQ PM\_IND PM\_REQ PM\_IND PM\_REQ PM\_IND PM\_REQ PM\_IND PM\_REQ TL/F/10386-12 FIGURE 3-10. Single Attach Concentrator (SAC), Single MAC PM\_REQ PM\_IND PM\_REQ PM\_IND B\_REO A\_IND B\_REO A\_IND MAC\_1 B\_IND A\_REQ B\_IND A\_REQ PH\_REQ PH\_IND MA\_REO MA\_IND A\_REQ A\_REQ A\_REQ B\_IND A\_REQ B\_IND B\_IND PHY\_M PHY\_M PHY\_M PHY\_M A\_IND B\_REQ A\_IND B\_REQ A\_IND B\_REQ A\_IND B\_REQ PM\_REQ PM\_IND PM\_REQ PM\_REQ PM\_REQ TL/F/10386-13 FIGURE 3-11. Dual Attach Concentrator (DAC), Single MAC MA\_IND MA\_REQ PM\_REQ PM\_IND PM\_REQ PM\_IND PH\_IND MAC\_ PH\_REQ A\_IND B\_REQ B\_REQ A\_IND PHY\_B B\_IND A\_REQ B\_IND PH\_REQ MAC\_1 PH\_IND A\_REQ MA\_REQ MA\_IND B\_IND A\_REQ B\_IND A\_REQ B\_IND A\_REQ B\_IND PHY\_M PHY\_M PHY\_M PHY\_M A\_IND B\_REQ A\_IND B\_REQ A\_IND B\_REQ A\_IND B\_REQ PM\_IND PM\_REQ PM\_IND PM\_REQ PM\_IND PM\_REQ PM\_IND PM\_REQ TL/F/10386-14 FIGURE 3-12. Dual Attach Concentrator (DAC), Dual MACs

### 4.0 Modes of Operation

The PLAYER device can operate in 4 basic modes: RUN, STOP, LOOPBACK, and CASCADE.

### 4.1 RUN MODE

RUN is the normal mode of operation.

In this mode, the PLAYER device is configured to be connected to the media via the Fiber Optic Transmitter and Receiver at the Serial Interface. It is also connected to other PLAYER device(s) and/or BMAC device(s) via the Port A and Port B Interfaces.

While operating in the Run mode, the PLAYER device receives and transmits Line States (Quiet, Halt, Master, Idle) and frames (Active Line State).

### **4.2 STOP MODE**

The PLAYER device operates in the STOP mode while it is being initialized or configured.

The PLAYER device is also reset to the STOP mode automatically when the RST pin (pin 71 on the DP83251 and pin 111 on the DP83255) is set to ground.

When in STOP mode, the PLAYER device performs the following functions:

- · Resets the Repeat Filter.

- · Resets the Smoother.

- · Resets the Receiver Block Line State Counters.

- · Flushes the Elasticity Buffer.

- · Forces Line State Unknown in the Receiver Block.

- Outputs LSU symbol pairs (0 1 0011 1010) through the PHY Data Indicate pins (AIP, AIC, AID <7:0>, BIP, BIC, BID <7:0>).

- Outputs Quiet symbol pairs through the PMD Data Request pins (TXD±).

- Resets all Control Bus register contents to zero or default values.

### 4.3 LOOPBACK MODE

The PLAYER device provides three types of loopback tests: Configuration Switch Loopback, Internal Loopback, and External Loopback. These Loopback modes can be used to test different portions of the device.

### 4.3.1 Configuration Switch Loopback

The Configuration Switch Loopback can be used to test the data paths of the BMAC device(s) that are connected to the PLAYER device before transmitting and receiving data through the network.

In the Configuration Switch Loopback mode, the PLAYER device performs the following functions:

- Selects Port A PHY Request Data, Port B PHY Request Data, or PHY Invalid to connect to Port A PHY Indicate Data via the A\_IND Mux.

- Selects Port A PHY Request Data, Port B PHY Request Data, or PHY Invalid to connect to Port B PHY Indicate Data via the B\_IND Mux.

- Connects data from the Receiver Block to the Transmitter Block via the Transmitter\_Mux. (The PLAYER device is repeating incoming data from the media in the Configuration Switch Loopback mode.)

See Figure 4-1a and 4-1b for block diagrams.

TL/F/10386-42

FIGURE 4-1a. Configuration Switch Loopback for DP83255

FIGURE 4-1b. Configuration Switch Loopback for DP83251 FIGURE 4-1.

### 4.3.2 Internal Loopback

The Internal Loopback mode can be used to test the functionality of the PLAYER device and to test the data paths between the PLAYER and BMAC devices before ring insertion

When in the Internal Loopback mode, the PLAYER device performs the following functions:

- Directs the output data of the Transmitter Block to the input of the Receiver Block through internal paths (see Figure 2-1 PLAYER Device Block Diagram).

- Ignores the PMD Data Indicate pins (RXD± and RXC±),

- Outputs Quiet symbols through the PMD Data Request pins (TXD±), and

Outputs Quiet symbols through the External Loopback Data pins (LBD±).

The level of the Quiet symbols transmitted through the TXC± pins is programmable through the Transmit Quiet Level bit of the Mode Register.

The level of the Quiet symbols transmitted through the LBD± pins is always high, regardless of the Transmit Quiet Level bit of the Mode Register.

If both Internal Loopback and External Loopback modes are selected, Internal Loopback mode will have priority over External Loopback mode.

See Figure 4-2 for a block diagram.

FIGURE 4-2. Internal Loopback

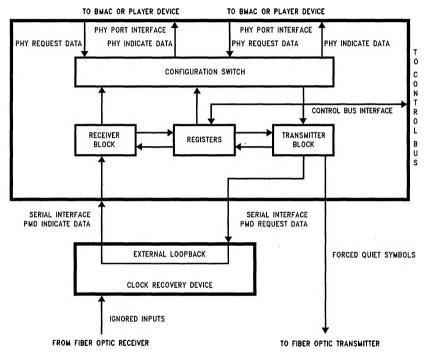

### 4.3.3 External Loopback

The External Loopback mode can be used to test the functionality of the PLAYER device and to test the data paths between the PLAYER, CRD, and BMAC devices before transmitting and receiving data through the network.

When in the External Loopback mode, the PLAYER device performs the following functions:

- Directs the output data of the Transmitter Block to the external Loopback Data pins (LBD±), which are normally connected to the Clock Recovery Device (see Figure 2. PLAYER Device Block Diagram).

- Outputs Quiet symbols through the PMD Data Request pins (TXD±).

The level of the Quiet symbols transmitted through the TXC $\pm$  pins is programmable through the Transmit Quiet Level bit of the Mode Register.

If both Internal Loopback and External Loopback modes are selected, Internal Loopback mode will have priority over External Loopback mode.

See Figure 4-3 for a block diagram.

FIGURE 4-3. External Loopback

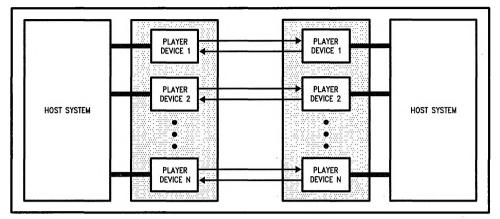

### 4.4 CASCADE MODE

The PLAYER device can operate in the Cascade (parallel) mode—Figure 4-4—which is used in high bandwidth, point-to-point data transfer applications. This is a non-FDDI mode of operation.

### CONCEPTS

In the Cascade mode, multiple PLAYER devices are connected together to provide data transfer at multiples of the FDDI data rate. Two cascaded PLAYER devices provide a data rate twice the FDDI data rate; three cascaded PLAYER devices provide a data rate three times the FDDI data rate, atc.

Multiple data streams are transmitted in parallel over each pair of cascaded PLAYER devices. All data streams start simultaneously and begin with the JK symbol pair on each PLAYER device.

Data is synchronized at the receiver of each PLAYER device by the JK symbol pair. Upon receiving a JK symbol pair, a PLAYER device asserts the Cascade Ready signal to indicate the beginning of data reception.

The Cascade Ready signals of all PLAYER devices are open drain ANDed together to create the Cascade Start signal. The Cascade Start signal is used as the input to indicate that all PLAYER devices have received the JK symbol pair. Data is now being received at every PLAYER device and can be transferred from the cascaded PLAYER devices to the host system.

See Figure 4-5 for more information.

#### **OPERATING RULES**

When the PLAYER device is operating in Cascade mode, the following rules apply:

- Data integrity can be guaranteed if the worst case fiber optic transmission skew between parallel fiber cables is less than 40 ns. This amounts to about 785 meters of fiber, assuming a 1% worst case variance.

- Even though this is a non-FDDI application, the general rules for FDDI frames must be obeyed.

- Data frames must be a minimum of three bytes long (including the JK symbol pair). Smaller frames will cause Elasticity Buffer errors.

- Data frames must have a maximum size of 4500 bytes, with a JK starting delimiter and a (T or R or S)x or x(T or R or S) ending delimiter byte.

- Due to the different clock rates, the JK symbol pair may arrive at different times at each PLAYER device. The total skew between the fastest and slowest cascaded PLAY-ER devices receiving the JK starting delimiter must not exceed 80 ns.

- 4. The first PLAYER device to receive a JK symbol pair will present it to the host system and assert the Cascade Ready signal. The PLAYER device will present one more JK as it waits for the other PLAYER devices to recognize their JK. The maximum number of consecutive JKs that can be presented to the host is 2.

- The Cascade Start signal is set to 1 when all the cascaded PLAYER devices release their Cascade Ready signals,

- 6. Bit 4 (CSE) of the Receive Condition Register B (RCRB) is set to 1 if the Cascade Start signal (CS) is not set before the second falling edge of clock signal LBC from when Cascade Ready (CR) was released. CS has to be set within approximately 80 ns of CR release. This condition signifies that not all cascaded PLAYERs have received their respective JK symbol pair within the allowed skew range.

- If the JK symbols are corrupted in the point-to-point links, some PLAYER devices may not report a Cascaded Synchronization Error.

- 8. To guarantee integrity of the interframe information, the user must put at least 8 Idle symbol pairs between frames. The PLAYER device will function properly with only 4 Idle symbol pairs, however the interframe symbols may be corrupted with random non-JK symbols.

The BMAC device could be used to provide required framing and optical FCS support.

FIGURE 4-4. Parallel Transmission

TL/F/10386-18

TL/F/10386-19

FIGURE 4-5. Cascade Mode of Operation

Note: N is recommended to be less than 3 for this mode. See Application Note 679 for larger values of N.

# 5.0 Registers

The PLAYER device is initialized, configured, and monitored via 32 8-bit registers. These registers are accessible through the Control Bus Interface.

Table 5-1 is a Register Summary List. Table 5-2 shows the contents of each register.

**TABLE 5-1. Register Summary**

| Register       | Register | Register Name                              | Access Rules |              |  |

|----------------|----------|--------------------------------------------|--------------|--------------|--|

| Address Symbol |          | negiote name                               | Read         | Write        |  |

| 00h            | MR       | Mode Register                              | Always       | Always       |  |

| 01h            | CR       | Configuration Register                     | Always       | Always       |  |

| 02h            | ICR      | Interrupt Condition Register               | Always       | Conditional  |  |

| 03h            | ICMR     | Interrupt Condition Mask Register          | Always       | Always       |  |

| 04h            | CTSR     | Current Transmit State Register            | Always       | Conditional  |  |

| 05h            | IJTR     | Injection Threshold Register               | Always       | Always       |  |

| 06h            | ISRA     | Injection Symbol Register A                | Always       | Always       |  |

| 07h            | ISRB     | Injection Symbol Register B                | Always       | Always       |  |

| 08h            | CRSR     | Current Receive State Register             | Always       | Write Reject |  |

| 09h            | RCRA     | Receive Condition Register A               | Always       | Conditional  |  |

| 0Ah            | RCRB     | Receive Condition Register B               | Always       | Conditional  |  |

| 0Bh            | RCMRA    | Receive Condition Mask Register A          | Always       | Always       |  |

| 0Ch            | RCMRB    | Receive Condition Mask Register B          | Always       | Always       |  |

| 0Dh            | NTR      | Noise Threshold Register                   | Always       | Always       |  |

| 0Eh            | NPTR     | Noise Prescale Threshold Register          | Always       | Always       |  |

| 0Fh            | CNCR     | Current Noise Count Register               | Always       | Write Reject |  |

| 10h            | CNPCR    | Current Noise Prescale Count Register      | Always       | Write Reject |  |

| 11h            | STR      | State Threshold Register                   | Always       | Always       |  |

| 12h            | SPTR     | State Prescale Threshold Registger         | Always       | Always       |  |

| 13h            | CSCR     | Current State Count Register               | Always       | Write Reject |  |

| 14h            | CSPCR    | Current State Prescale Count Register      | Always       | Write Reject |  |

| 15h .          | LETR     | Link Error Threshold Register              | Always       | Always       |  |

| 16h            | CLECR    | Current Link Error Count Register          | Always       | Write Reject |  |

| 17h            | UDR      | User Definable Register                    | Always       | Always       |  |

| 18h            | IDR      | Device ID Register                         | Always       | Write Reject |  |

| 19h            | CIJCR    | Current Injection Count Register           | Always       | Write Reject |  |

| 1Ah            | ICCR     | Interrupt Condition Comparison Register    | Always       | Always       |  |

| 1Bh            | CTSCR    | Current Transmit State Comparison Register | Always       | Always       |  |

| 1Ch            | RCCRA    | Receive Condition Comparison Register A    | Always       | Always       |  |

| 1Dh            | RCCRB    | Receive Condition Comparison Register B    | Always       | Always       |  |

| 1Eh            | RR0      | Reserved Register 0                        | Always       | Write Reject |  |

| 1Fh            | RR1      | Reserved Register 1                        | Always       | Write Reject |  |

**TABLE 5-2. Register Content Summary**

| Register | Register | 2      | Bit Symbols |       |        |        |       |       |       |  |  |

|----------|----------|--------|-------------|-------|--------|--------|-------|-------|-------|--|--|

| Address  | Symbol   | D7     | D6          | D5    | D4     | D3     | D2    | D1    | D0    |  |  |

| 00h      | MR       | RNRZ   | TNRZ        | TE    | TQL    | СМ     | EXLB  | ILB   | RUN   |  |  |

| 01h      | CR       | BIE    | AIE         | TRS1  | TRS0   | BIS1   | BIS0  | AIS1  | AIS0  |  |  |

| 02h      | ICR      | UDI    | RCB         | RCA   | LEMT   | CWI    | CCR   | CPE   | DPE   |  |  |

| 03h      | ICMR     | UDIM   | RCBM        | RCAM  | LEMTM  | CWIM   | CCRM  | СРЕМ  | DPEM  |  |  |

| 04h      | CTSR     | RES    | PRDPE       | SE    | IC1    | IC0    | TM2   | TM1   | TM0   |  |  |

| 05h      | IJTR     | IJT7   | IJT6        | IIJ5  | IJT4   | IJT3   | IJT2  | IJT1  | IJTO  |  |  |

| 06h      | ISRA     | RES    | RES         | RES   | IJS4   | IJS3   | IJS2  | IJS1  | IJS0  |  |  |

| 07h      | ISRB     | RES    | RES         | RES   | IJS9   | IJS8   | IJS7  | IJS6  | IJS5  |  |  |

| 08h      | CRSR     | RES    | RES         | RES   | RES    | LSU    | LS2   | LS1   | LS0   |  |  |

| 09h      | RCRA     | LSUPI  | LSC         | NT    | NLS    | MLS    | HLS   | QLS   | NSD   |  |  |

| 0Ah      | RCRB     | RES    | SILS        | EBOU  | CSE    | LSUPV  | ALS   | ST    | ILS   |  |  |

| 0Bh      | RCMRA    | LSUPIM | LSCM        | NTM   | NLSM   | NLSM   | HLSM  | QLSM  | NSDM  |  |  |

| 0Ch      | RCMRB    | RES    | SILSM       | EBOUM | CSEM   | LSUPVM | ALSM  | STM   | ILSM  |  |  |

| 0Dh      | NTR      | RES    | NT6         | NT5   | NT4    | NT3    | NT2   | NT1   | NT0   |  |  |

| 0Eh      | NPTR     | NPT7   | NPT6        | NPT5  | NPT4   | NPT3   | NPT2  | NPT1  | NPT0  |  |  |

| 0Fh      | CNCR     | NCLSCD | CNC6        | CNC5  | CNC4   | CNC3   | CNC2  | CNC1  | CNC0  |  |  |

| 10h      | CNPCR    | CNPC7  | CNPC6       | CNPC5 | CNPC4  | CNPC3  | CNPC2 | CNPC1 | CNPC0 |  |  |

| 11h      | STR      | RES    | ST6         | ST5   | ST4    | ST3    | ST2   | ST1   | ST0   |  |  |

| 12h      | SPTR     | SPT7   | SPT6        | SPT5  | SPT4   | SPT3   | SPT2  | SPT1  | SPT0  |  |  |

| 13h      | CSCR     | SCLSCD | CSC6        | CSC5  | CSC4   | CSC3   | CSC2  | CSC1  | CSC0  |  |  |

| 14h      | CSPCR    | CSPC7  | CSPC6       | CSPC5 | CSPC4_ | CSPC3  | CSPC2 | CSPC1 | CSPC0 |  |  |

| 15h      | LETR     | LET7   | LET6        | LET5  | LET4   | LET3   | LET2  | LET1  | LET0  |  |  |

| 16h      | CLECR    | LEC7   | LEC6        | LEC5  | LEC4   | LEC3   | LEC2  | LEC1  | LEC0  |  |  |

| 17h      | UDR      | RES    | RES         | RES   | RES    | EB1    | EB0   | SB1   | SB0   |  |  |

| 18h      | IDR      | DID7   | DID6        | DID5  | DID4   | DID3   | DID2  | DID1  | DID0  |  |  |

| 19h      | CIJCR    | IJC7   | IJC6        | IJC5  | IJC4   | IJC3   | IJC2  | IJÇ1  | IJC0  |  |  |

| 1Ah      | ICCR     | UDIC   | RCBC        | RCAC  | LEMTC  | CWIC   | CCRC  | CPEC  | DPEC  |  |  |

| 1Bh      | CTSCR    | RESC   | PRDPEC      | SEC   | IC1C   | IC0C   | TM2C  | TM1C  | TMOC  |  |  |

| 1Ch      | RCCRA    | LSUPIC | LSCC        | NTC   | NLSC   | MLSC   | HLSC  | QLSC  | NSDC  |  |  |

| 1Dh      | RCCRB    | RESC   | SILSC       | EBOUC | CSEC   | LSUPVC | ALSC  | STC   | ILSC  |  |  |

| .1Eh     | RR1      | RES    | RES         | RES   | RES    | RES    | RES   | RES   | RES   |  |  |

| 1Fh      | RR2      | RES    | RES         | RES   | RES    | RES    | RES   | RES   | RES   |  |  |

### MODE REGISTER (MR)

The Mode Register is used to initialize and configure the PLAYER device.

In order to minimize interruptions on the network, it is recommended that the PLAYER device first be put in STOP mode (i.e. set the RUN bit to zero) before programming the Mode Register, the Configuration Register, or the Current Transmit State Register.

### **ACCESS RULES**

| ADDRESS | \$   | READ   | WRITE  |            |      |     |     |

|---------|------|--------|--------|------------|------|-----|-----|

| 00h     |      | Always | Always |            |      |     |     |

| D7      | D6   | D5     | D4     | <b>D</b> 3 | D2   | D1  | D0  |

| RNRZ    | TNRZ | TE     | TQL    | СМ         | EXLB | ILB | RUN |

| Bit    | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DO RUN |        | RUN /STOP  0: Enables the STOP mode. Refer to Section 4.2, STOP Mode of Operation, for more information.  1: Normal Operation (i.e. RUN mode).  Note: The RUN bit is automatically set to 0 when the RST pin is asserted (i.e. set to ground).                                                                                                                                                                                                                                                                             |  |  |  |  |

| D1     | ILB    | INTERNAL LOOPBACK:  0: Disables Internal Loopback mode (i.e. normal operation).  1: Enables Internal Loopback mode.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|        |        | Refer to Section 4.3, Loopback Mode of Operation, for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| D2     | EXLB   | EXTERNAL LOOPBACK  0: Disables External Loopback mode (i.e. normal operation).  1: Enables External Loopback mode.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        |        | Refer to Section 4.3, Loopback Mode of Operation, for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| D3     | СМ     | CASCADE MODE:  0: Disables synchronization of cascaded PLAYER devices.  1: Enables the synchronization of cascaded PLAYER devices.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        |        | Refer to Section 4.4, Cascade Mode of Operation, for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D4     | TQL    | TRANSMIT QUIET LEVEL: This bit is used to program the transmission level of the Quiet symbols.  0: Low level Quiet symbols are transmitted through the PMD Data Request pins (i.e. TXD+ = low, TXD- = high).  1: High level Quiet symbols are transmitted through the PMD Data Request pins (i.e. TXD+ = high, TXD- = low).                                                                                                                                                                                                |  |  |  |  |

| D5     | TE     | TRANSMIT ENABLE: The TE bit controls the action of FOTX Enable (TXE) pin independent of the current transmit mode. When TE is 0, the TXE output disables the optical transmitter; when TE is 1, the optical transmitter is disabled during the Off Transmit Mode (OTM) and enabled otherwise. The On and Off level of the TXE is dependent on the FOTX Enable Level (TEL) pin to the PLAYER device. The following rules summarizes the output of TXE:  (1) If TE = 0, then TXE = Off (2) If TE = 1 and OTM, then TXE = On. |  |  |  |  |

| D6     | TNRZ   | TRANSMIT NRZ DATA: 0: Transmits data in Non-Return-To-Zero-Invert-On-Ones format. 1: Transmits data in Non-Return-To-Zero format.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| D7     | RNRZ   | RECEIVE NRZ DATA:  0: Receives data in Non-Return-To-Zero-Invert-On-Ones format.  1: Receives data in Non-Return-To-Zero format.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

### **CONFIGURATION REGISTER (CR)**

The Configuration Register controls the Configuration Switch Block and enables/disables both the A and B Indicate output ports.

Note that the B\_Indicate output port is offered only on the DP83255 (for Dual Attach Stations), and not in the DP83251 (for Single Attach Stations).

For further information, refer to Section 3.3, Configuration Switch.

| ADDRESS | READ   | WRITE  |  |

|---------|--------|--------|--|

| 01h     | Always | Always |  |

| D7  | D6  | D5   | D4   | D3   | D2   | D1   | D0   |

|-----|-----|------|------|------|------|------|------|

| BIE | AIE | TRS1 | TRS0 | BIS1 | BIS0 | AIS1 | AIS0 |

| Bit    | Symbol     |                                                                                                                                                                              |                                             | Description                                                                                                                                                                                              |  |  |  |

|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D0, D1 | AIS0, AIS1 | A_INDICATE SELECTOR <0, 1>: The A_Indicate Selector <0, 1> bits select one of the four Configuration Switch data buses for the A_Indicate output port (AIP, AIC, AID <7:0>). |                                             |                                                                                                                                                                                                          |  |  |  |

|        |            | AIS1                                                                                                                                                                         | AIS0                                        |                                                                                                                                                                                                          |  |  |  |

|        | Į          | 0                                                                                                                                                                            | 0                                           | PHY Invalid Bus                                                                                                                                                                                          |  |  |  |

|        |            | 0                                                                                                                                                                            | 1                                           | Receiver Bus                                                                                                                                                                                             |  |  |  |

|        |            | 1                                                                                                                                                                            | 0                                           | A_Request Bus                                                                                                                                                                                            |  |  |  |

|        |            | 1                                                                                                                                                                            | 1                                           | B_Request Bus                                                                                                                                                                                            |  |  |  |

| D2, D3 | BIS0, BIS1 |                                                                                                                                                                              |                                             | he B_Indicate Selector $<0$ , 1> bits select one of the four $=$ B_Indicate output port (BIP, BIC, BID $<7:0>$ ).                                                                                        |  |  |  |

|        |            | BIS1                                                                                                                                                                         | BIS0                                        |                                                                                                                                                                                                          |  |  |  |

|        |            | 0                                                                                                                                                                            | 0                                           | PHY Invalid Bus                                                                                                                                                                                          |  |  |  |

|        |            | 0                                                                                                                                                                            | 1                                           | Receiver Bus                                                                                                                                                                                             |  |  |  |

|        |            | 1                                                                                                                                                                            | 0                                           | A_Request Bus                                                                                                                                                                                            |  |  |  |

|        |            | 1                                                                                                                                                                            | 1                                           | B_Request Bus                                                                                                                                                                                            |  |  |  |

|        |            | Note: Even though this bit ca<br>any I/Os since the DP83251                                                                                                                  |                                             | cleared in the DP83251 (for Single Attach Stations), it will not affect $B\_$ Indicate port.                                                                                                             |  |  |  |

| D4, D5 | TRS0, TRS1 | TRANSMIT REQUEST SELECTOR <0, 1>: The Transmit Request Selector <0, 1> bits select one of the four Configuration Switch data buses for the input to the Transmitter Block.   |                                             |                                                                                                                                                                                                          |  |  |  |

|        |            | TRS1                                                                                                                                                                         | TRS0                                        |                                                                                                                                                                                                          |  |  |  |

|        |            | 0                                                                                                                                                                            | 0                                           | PHY Invalid Bus                                                                                                                                                                                          |  |  |  |

|        |            | 0                                                                                                                                                                            | 1                                           | Receiver Bus                                                                                                                                                                                             |  |  |  |

|        |            | 1                                                                                                                                                                            | 0                                           | A_Request Bus                                                                                                                                                                                            |  |  |  |

|        |            | 1                                                                                                                                                                            | 1                                           | B_Request Bus                                                                                                                                                                                            |  |  |  |

|        |            | Transmit State Register (CTS                                                                                                                                                 | SR) are set to 00                           | smit Mode (i.e. the Transmit Mode bits (TM < 2:0 > ) of the Current<br>0) and the PHY Invalid Bus is selected, then the PLAYER device will<br>and then continuous Idle symbols due to the Repeat Filter. |  |  |  |

| D6     | AIE        | the port is disable                                                                                                                                                          | ndicate output<br>d.                        | port. The A_Indicate port pins will be at TRI-STATE wher                                                                                                                                                 |  |  |  |

| D7     | BIE        | when the port is d<br>1: Enables the B_In                                                                                                                                    | dicate output<br>isabled.<br>ndicate output | port. The B_Indicate port pins will be at TRI-STATE  port (BIP, BIC, BID < 7:0 > ).  cleared in the DP83251 (for Single Attach Stations), it will not affect                                             |  |  |  |

### INTERRUPT CONDITION REGISTER (ICR)

The Interrupt Condition Register records the occurrence of an internal error event, the detection of Line State, an unsuccessful write by the Control Bus Interface, the expiration of an internal counter, or the assertion of one or more of the User Definable Sense pins.

The Interrupt Condition Register will assert the Interrupt pin (INT) when one or more bits within the register are set to 1 and the corresponding mask bits in the Interrupt Condition Mask Register (ICMR) are also set to 1.

| ADDRESS | READ   | WRITE       |

|---------|--------|-------------|

| 02h     | Always | Conditional |

|   | D7  | D6  | D5  | D4   | D3  | D2  | D1  | D0  |

|---|-----|-----|-----|------|-----|-----|-----|-----|

| l | UDI | RCB | RCA | LEMT | CWI | CCR | CPE | DPE |

| Bit | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

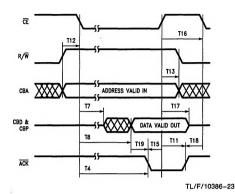

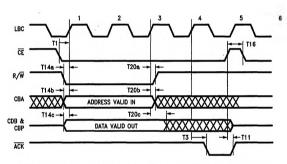

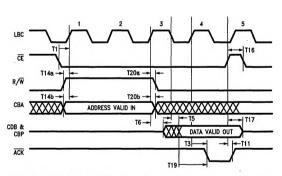

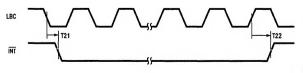

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|