# DP8428/NS32828, DP8429/NS32829 1 Megabit High Speed Dynamic RAM Controller/Drivers

# **General Description**

The DP8428 and DP8429 1M DRAM Controller/Drivers are designed to provide "No-Waitstate" CPU interface to Dynamic RAM arrays of up to 8 Mbytes and larger. The DP8428 and DP8429 are tailored for 32-bit and 16-bit system requirements, respectively. Both devices are fabricated using National's new oxide isolated Advanced Low power Schottky (ALS) process and use design techniques which enable them to significantly out-perform all other LSI or discrete alternatives in speed, level of integration, and power consumption.

Each device integrates the following critical 1M DRAM controller functions on a single monolithic device: ultra precise delay line; 9 bit refresh counter; fall-through row, column, and bank select input latches; Row/Column address muxing logic; on-board high capacitive-load RAS, CAS, Write Enable and Address output drivers; and, precise control signal timing for all the above.

In order to specify each device for "true" worst case operating conditions, all timing parameters are guaranteed while the chip is driving the capacitive load of 88 DRAMs including trace capacitance. The chip's delay timing logic makes use of a patented new delay line technique which keeps AC skew to  $\pm 3$  ns over the full  $V_{\rm CC}$  range of  $\pm 10\%$  and temperature range of  $-55^{\circ}{\rm C}$  to  $+125^{\circ}{\rm C}$ . The DP8428 and DP8429 guarantee a maximum RASIN to CASOUT delay of 80 ns or 70 ns even while driving an 8 Mbyte memory array with error correction check bits included. Two speed selected options of these devices are shown in the switching characteristics section of this document. (Continued)

#### **Features**

- Makes DRAM interface and refresh tasks appear virtually transparent to the CPU making DRAMs as easy to use as static RAMs

- Specifically designed to eliminate CPU wait states up to 10 MHz or beyond

- Eliminates 20 discrete components for significant board real estate reduction, system power savings and the elimination of chip-to-chip AC skewing

- On-board ultra precise delay line

- On-board high capacitive RAS, CAS, WE and Address drivers (specified driving 88 DRAMs directly)

- AC specified for directly addressing up to 8 Mbytes

- Low power/high speed bipolar oxide isolated process

- Downward pin and function compatible with 256k DRAM Controller/Drivers DP8409A, DP8417, DP8418, and DP8419

#### **Contents**

- System and Device Block Diagrams

- Recommended Companion Components

- Device Connection Diagrams and Pin Definitions

- Device Differences—DP8428 vs DP8429

- Mode of Operation (Descriptions and Timing Diagrams)

- Application Description and Diagrams

- DC/AC Electrical Specifications, Timing Diagrams and Test Conditions

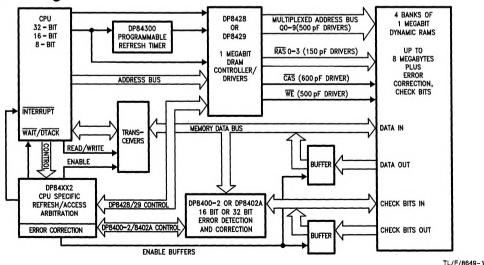

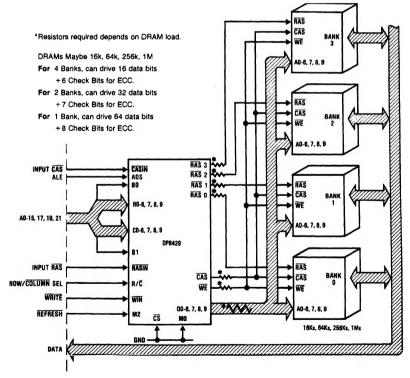

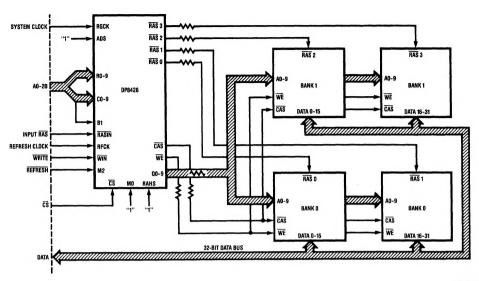

# **System Diagram**

#### General Description (Continued)

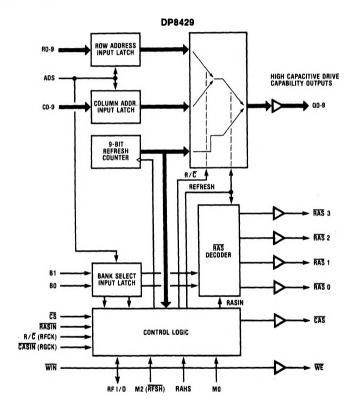

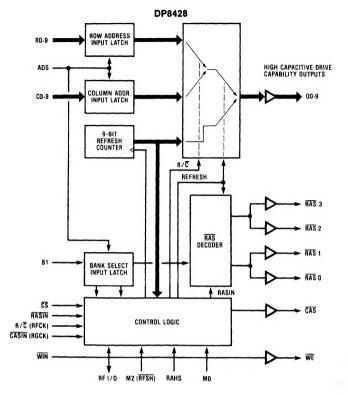

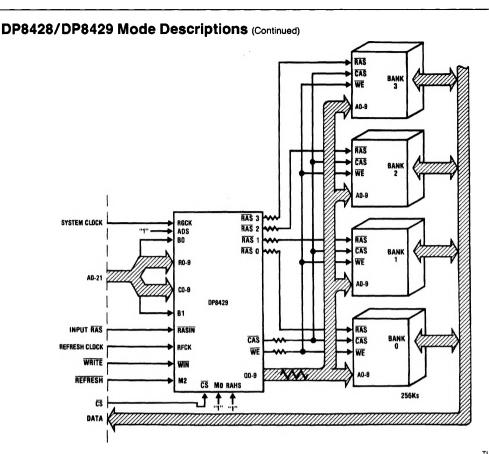

With its four independent RAS outputs and ten multiplexed address outputs, the DP8429 can support up to four banks of 64k, 256k or 1M DRAMs. Two bank select pins, B1 and B0, are decoded to activate one of the RAS signals during an access, leaving the three non-selected banks in the standby mode (less than one tenth of the operating power) with data outputs in TRI-STATE®. The DP8428's one Bank Select pin, B1, enables 2 banks automatically during an access in order to provide an optimum interface for 32-bit microprocessors.

The DP8428 and DP8429 each have two mode-select pins, allowing for two refresh modes and two access modes. Refresh and access timing may be controlled either externally

or automatically. The automatic modes require a minimum of input control signals.

A refresh counter is on-chip and is multiplexed with the row and column inputs. Its contents appear at the address outputs of the DP8428 or DP8429 during any refresh, and are incremented at the completion of the refresh. Row, Column and bank address latches are also on-chip. However, if the address inputs to the DP8428 or DP8429 are valid throughout the duration of the access, these latches may be operated in the fall-through mode.

Each device is available in either the 52 pin Ceramic DIP, or the low cost JEDEC standard 68 pin Plastic Chip Carrier (PCC) package.

# **Functional Block Diagrams**

TL/F/8649-2

# Functional Block Diagrams (Continued)

TL/F/8649-3

#### **System Companion Components**

| Device # | Function                                                         |

|----------|------------------------------------------------------------------|

| DP84300  | Programmable Refresh Timer for DP84xx DRAM Controller            |

| DP84412  | NS32008/16/32 to DP8409A/17/18/19/28/29 Interface                |

| DP84512  | NS32332 to DP8417/18/19/28/29 Interface                          |

| DP84322  | 68000/08/10 to DP8409A/17/18/19/28/29 Interface (up to 8 MHz)    |

| DP84422  | 68000/08/10 to DP8409A/17/18/19/28/29 Interface (up to 12.5 MHz) |

| DP84522  | 68020 to DP8417/18/19/28/29 Interface                            |

| DP84432  | 8086/88/186/188 to DP8409A/17/18/19/28/29 Interface              |

| DP84532  | 80286 to DP8409A/17/18/19/28/29 Interface                        |

| DP8400-2 | 16-Bit Expandable Error Checker/Corrector (E2C2)                 |

| DP8402A  | 32-Bit Error Detector And Corrector (EDAC)                       |

#### **Connection Diagrams Dual-In-Line Package Dual-In-Line Package** 52 RASIN R / C (RFCK) RASIN R / C (RFCK) 51 50 CASÍN (RGCK) cs CASIN (RGCK) · cs RF 1/0 RF 1/0 49 WIN 48 WF RAHS WIN RAHS M2 (RFSH) WE M2 (RFSH) ADS 00 QO ADS RO Q9 RO Q9 CO Q1 CO R1 02 R1 10 10 C1 Q3 C1 11 R2 R2 12 12 C2 GND C2 13 40 DP8428 DP8429 GND GND R3 Q5 Q5 15 38 15 C3 vcc C3 vcc 37 37 16 R4 Q6 R4 Q6 17 36 C4 Q7 C4 07 18 18 08 R5 08 19 19 CAS R9 20 C5 C5 CAS 20 33 RASS R9 c9 21 32 RAS2 C9 RAS2 22 22 RAS1 R6 RAS1 30 RASO 30 RASO 23 23 C6 C6 R7 24 29 NC ВО C7 25 28 <sub>B1</sub> 28 B1 25 **C7** 26 26 27 C8 R8 R8 TL/F/8649-4 TL/F/8649-5 Order Number DP8428D-70, DP8428D-80 or DP8429D-70, DP8429D-80 See NS Package Number D52A **Plastic Chip Carrier Package Plastic Chip Carrier Package** MO CASIN (RGCK) R.C. (RFCK) EASIN C.S RF I/O WIN WE RAHS MO CASIN (RECK) RYC(RECK) CSSIN RT/O RTI/O WIN 90 (RFSH) 8 7 6 5 4 3 2 1 6867666564636261 6 5 4 3 2 1 6867666564636261 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 ADS R0 C0 R1 C1 R2 C2 GND GND R3 C3 R4 C4 R5 C5 R9 59 58 57 56 55 54 53 52 51 50 49 48 47 46 Q9 Q1 Q2 Q3 Q4 GND ADS Q9 Q1 Q2 Q3 Q4 GND GND Q5 Vcc Q6 Q7 Q8 CAS R0 C0 R1 C1 R2 C2 GND GND R3 C3 R4 C4 R5 C5 R9 13 14 15 16 17 18 19 20 21 22 23 24 25 26 GND DP8428 DP8429 Q5 Vcc Vcc Q6 Q7 Q8 CAS 45 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 RASSI TL/F/8649-6 TL/F/8649-7 Order Number DP8428V-70, DP8428V-80 or DP8429V-70, DP8429V-80 See NS Package Number V68A

#### **DP8428 vs DP8429**

The DP8428 DYNAMIC RAM CONTROLLER/DRIVER is identical to the DP8429 with the exception of two functional differences incorporated to improve performance with 32-bit microprocessors.

- 1) Pin 28 (B1) is used to enable/disable a pair of RAS outputs, and pin 29 (B0 on the DP8429) is a no connect. When B1 is low, RASO and RAS1 are enabled such that they both go low during an access. When B1 is high, RAS2 and RAS3 are enabled. This feature is useful when driving words of 32 bits or more since each RAS would be driving only one half of the word. By distributing the load on each RAS line in this way, the DP8428 will meet the same AC specifications driving 2 banks of 32 DRAMs each as the DP8429 does driving 4 banks of 16 bits each.

- 2) The hidden refresh function available on the DP8429 has been disabled on the DP8428 in order to reduce the amount of setup time necessary from CS going low to RASIN going low during an access of DRAM. This parameter, called t<sub>CSRL1</sub>, is 5 ns for the DP8428 whereas it is 34 ns for the DP8429. The hidden refresh function allowed only a very small increase in system performance, at microprocessor frequencies of 10 MHz and above.

#### **Pin Definitions**

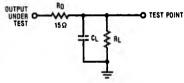

$V_{CC},$  GND, GND -  $V_{CC}=5V$   $\pm\,10\%.$  The three supply pins have been assigned to the center of the package to reduce voltage drops, both DC and AC. There are two ground pins to reduce the low level noise. The second ground pin is located two pins from  $V_{CC}$ , so that decoupling capacitors can be inserted directly next to these pins. It is important to adequately decouple this device, due to the high switching currents that will occur when all 10 address bits change in the same direction simultaneously. A recommended solution would be a 1  $\mu\mathrm{F}$  multilayer ceramic capacitor in parallel with a low-voltage tantalum capacitor, both connected as close as possible to GND and  $V_{CC}$  to reduce lead inductance. See Figure below.

\*Capacitor values should be chosen depending on the particular application.

R0-R9: Row Address Inputs.

C0-C9: Column Address Inputs.

Q0-Q9: Multiplexed Address Outputs - This address is selected from the Row Address Input Latch, the Column Address Input Latch or the Refresh Counter.

RASIN: Row Address Strobe Input - RASIN directly controls the selected RAS output when in an access mode and all RAS outputs during hidden or external refresh.

R/C (RFCK) – In the auto-modes this pin is the external refresh clock input; one refresh cycle should be performed each clock period. In the external access mode it is Row/Column Select Input which enables either the row or column address input latch onto the output bus.

CASIN (RGCK) - In the auto-modes this pin is the RAS Generator Clock input. In external access mode it is the Column Address Strobe input which controls CAS directly once columns are enabled on the address outputs.

ADS: Address (Latch) Strobe Input – Row Address, Column Address, and Bank Select Latches are fall-through with ADS high; latching occurs on high-to-low transition of ADS.

**CS:** Chip Select Input - When high, CS disables all accesses. Refreshing, however, in both modes 0 and 1 is not affected by this pin.

M0, M2 (RFSH): Mode Control Inputs – These pins select one of the four available operational modes of the DP8429 (see Table III).

RFI/0: Refresh Input/Output – In the auto-modes this pin is the Refresh Request Output. It goes low following RFCK indicating that no hidden refresh was performed while RFCK was high. When this pin is set low by an external gate the on-chip refresh counter is reset to all zeroes.

WIN: Write Enable Input.

WE: Write Enable Output - WE follows WIN unconditionally.

RAHS: Row Address Hold Time Select – Selects the t<sub>RAH</sub> to be guaranteed by the DP8428 or DP8429 delay line to allow for the use of fast or slow DRAMs.

CAS: Column Address Strobe Output – In mode 5 and in mode 4 with CASIN low before R/C goes low, CAS goes low automatically after the column address is valid on the address outputs. In mode 4 CAS follows CASIN directly after R/C goes low, allowing for nibble accessing. CAS is always high during refresh.

RAS 0-3: Row Address Strobe Outputs - The enabled RAS output (see Table II) follows RASIN directly during an access. During refresh, all RAS outputs are enabled.

#### Pin Definitions (Continued)

B0, B1: Bank Select Inputs – These pins are decoded to enable one or two of the four RAS outputs during an access (see Table I and Table II).

TABLE I. DP8429 Memory Bank Decode

|    | Select<br>by ADS) | Enabled RAS <sub>n</sub>             |

|----|-------------------|--------------------------------------|

| B1 | В0                |                                      |

| 0  | 0                 | RAS <sub>0</sub>                     |

| 0  | 1                 | RAS <sub>0</sub><br>RAS <sub>1</sub> |

| 1  | 0                 | RAS                                  |

| 1  | 1                 | RAS <sub>3</sub>                     |

TABLE II. DP8428 Memory Bank Decode

|    | Select<br>by ADS) | Enabled RAS <sub>n</sub>                                                   |

|----|-------------------|----------------------------------------------------------------------------|

| B1 | NC                |                                                                            |

| 0  | Х                 | RAS <sub>0</sub> & RAS <sub>1</sub>                                        |

| 1  | X                 | RAS <sub>0</sub> & RAS <sub>1</sub><br>RAS <sub>2</sub> & RAS <sub>3</sub> |

#### **Conditions for All Modes**

#### INPUT ADDRESSING

The address block consists of a row-address latch, a column-address latch, and a resettable refresh counter. The address latches are fall-through when ADS is high and latch when ADS goes low. If the address bus contains valid addresses until after CAS goes low at the end of the memory cycle, ADS can be permanently high. Otherwise ADS must go low while the addresses are still valid.

#### **DRIVE CAPABILITY**

The DP8429 has timing parameters that are specified driving the typical capacitance (including traces) of 88, 5V-only DRAMs. Since there are 4 RAS outputs, each is specified driving one-fourth of the total memory. CAS, WE and the address outputs are specified driving all 88 DRAMs.

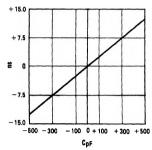

The graph in *Figure 10* may be used to determine the slight variations in timing parameters, due to loading conditions other than 88 DRAMs.

Because of distributed trace capacitance and inductance and DRAM input capacitance, current spikes can be created, causing overshoots and undershoots at the DRAM inputs that can change the contents of the DRAMs or even destroy them. To reduce these spikes, a damping resistor (low inductance, carbon) should be inserted between the DP8429 outputs and the DRAMs, as close as possible to

the DP8429. The damping resistor values may differ depending on how heavily an output is loaded. These resistors should be determined by the first prototypes (not wirewrapped due to the larger distributed capacitance and inductance). Resistors should be chosen such that the transition on the control outputs is critically damped. Typical values will be from  $15\Omega$  to  $100\Omega$ , with the lower values being used with the larger memory arrays. Note that AC parameters are specified with  $15\Omega$  damping resistors. For more information see AN-305 "Precautions to Take When Driving Memories".

#### DP8429 DRIVING ANY 256k or 1M DRAMS

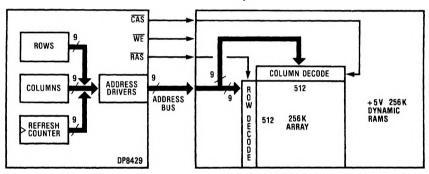

The DP8429 can drive any 256k or 1M DRAMs. 256k DRAMs require 18 of the DP8429's address inputs to select one memory location within the DRAM. RAS-only refreshing with the nine-bit refresh-counter on the DP8429 makes CAS before RAS refreshing, available on 256k DRAMs, unnecessary (see *Figure 1a*).

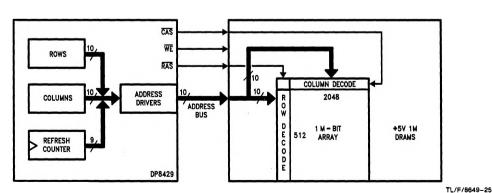

1 Mbit DRAMs require the use of all 10 of the DP8429 Address Outputs (see *Figure 1b*).

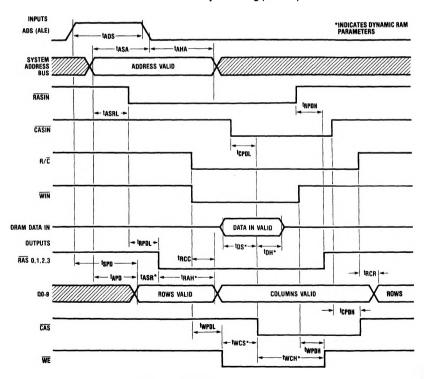

#### READ, WRITE AND READ-MODIFY-WRITE CYCLES

The output signal, WE, determines what type of memory access cycle the memory will perform. If WE is kept high while CAS goes low, a read cycle occurs. If WE goes low before CAS goes low, a write cycle occurs and data at DI (DRAM input data) is written into the DRAM as CAS goes low. If WE goes low later than t<sub>CWD</sub> after CAS goes low, first a read occurs and DO (DRAM output data) becomes valid, then data DI is written into the same address in the DRAM as WE goes low. In this read-modify-write case, DI and DO cannot be linked together. WE always follows WIN directly to determine the type of access to be performed.

#### **POWER-UP INITIALIZE**

When V<sub>CC</sub> is first applied to the DP8429, an initialize pulse clears the refresh counter and the internal control flip-flops.

#### **Mode Features Summary**

- 4 modes of operation: 2 access and 2 refresh

- Automatic or external selected by the user

- Auto access mode provides RAS, row to column change, and then CAS automatically.

- Choice between two different values of t<sub>RAH</sub> in auto-access mode

- CAS controlled independently in external control mode, allowing for nibble mode accessing

- Automatic refreshing can make refreshes transparent to the system

- CAS is inhibited during refresh cycles

TL/F/8649-12

# DP8428/DP8429 Mode Descriptions

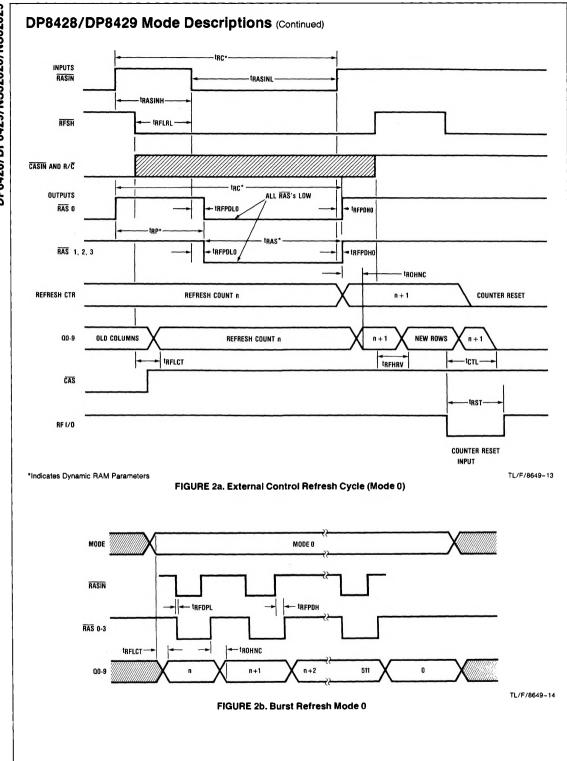

#### MODE 0-EXTERNALLY CONTROLLED REFRESH

Figure 2 shows the Externally Controlled Refresh timing. In this mode the refresh counter contents are multiplexed to the address outputs. All RAS outputs are enabled to follow RASIN so that the row address indicated by the refresh counter is refreshed in all DRAM banks when RASIN goes low. The refresh counter increments when RASIN goes high. RFSH should be held low at least until RASIN goes high (they may go high simultaneously) so that the refresh address remains valid and all RAS outputs remain enabled throughout the refresh.

A burst refresh may be performed by holding RFSH low and toggling RASIN until all rows are refreshed. It may be useful in this case to reset the refresh counter just prior to beginning the refresh. The refresh counter resets to all zeroes when RFI/O is pulled low by an external gate. The refresh counter always counts to 511 before rolling over to zero. If there are 128 or 256 rows being refreshed then Q7 or Q8, respectively, going high may be used as an end-of-burst indicator.

In order that the refresh address is valid on the address outputs prior to the RAS lines going low, RFSH must go low before RASIN. The setup time required is given by  $t_{\rm RFLRL}$  in the Switching Characteristics. This parameter may be adjusted using Figure 10 for loading conditions other than those specified.

TABLE III. DP8428/DP8429 Mode Select Options

| Mode | (RFSH)<br>M2 | МО | Mode of Operation               |

|------|--------------|----|---------------------------------|

| 0    | 0            | 0  | Externally Controlled Refresh   |

| 1    | 0            | 1  | Auto Refresh-Forced             |

| 4    | 1            | 0  | Externally Controlled Access    |

| 5    | 1            | 1  | Auto Access<br>(Hidden Refresh) |

#### DP8428/DP8429 Interface Between System and DRAM Banks

All 9 Bits of Refresh Counter Used

FIGURE 1a, DP8428/DP8429 with 256k DRAMs

All 9 Bits of Refresh Counter Used

FIGURE 1b. DP8428/DP8429 with 1M DRAMs

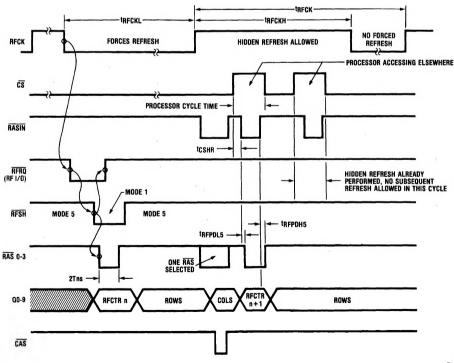

#### MODE 1-AUTOMATIC FORCED REFRESH

In Mode 1 the R/C (RFCK) pin becomes RFCK (refresh cycle clock) and the CASIN (RGCK) pin becomes RGCK (RAS generator clock). If RFCK is high and Mode 1 is entered then the chip operates as if in MODE 0 (externally controlled refresh), with all RAS outputs following RASIN. This feature of Mode 1 may be useful for those who want to use Mode 5 (automatic access) with externally controlled refresh. By holding RFCK permanently high one need only togelle M2 (RFSH) to switch from Mode 5 to external refresh. As with Mode 0, RFI/O may be pulled low by an external gate to reset the refresh counter.

When using Mode 1 as automatic refresh, RFCK must be an input clock signal. One refresh should occur each period of RFCK. If no refresh is performed while RFCK is high, then when RFCK goes low RFI/O immediately goes low to indicate that a refresh is requested. (RFI/O may still be used to reset the refresh counter even though it is also used as a refresh request pin, however, an open-collector gate should be used to reset the counter in this case since RFI/O is forced low internally for a request).

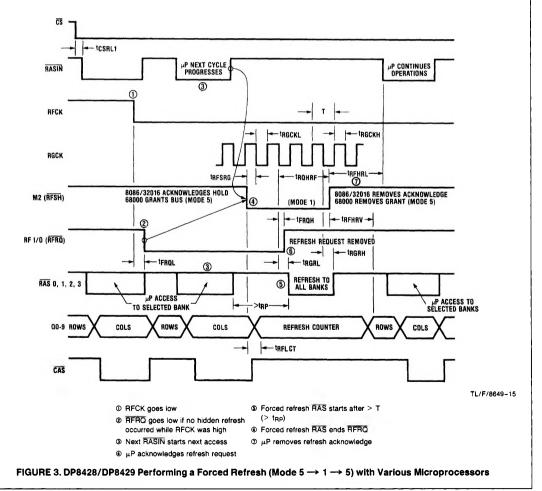

After receiving the refresh request the system must allow a forced refresh to take place while RFCK is low. External logic can monitor RFRQ (RFI/O) so that when RFRQ goes low this logic will wait for the access currently in progress to be completed before pulling M2 (RFSH) low to put the DP8429 in mode 1. If no access is taking place when RFRQ occurs, then M2 may immediately go low. Once M2 is low, the refresh counter contents appear at the address outputs and RAS is generated to perform the refresh.

An external clock on RGCK is required to derive the refresh RAS signals. On the second falling edge of RGCK after M2 is low, all RAS lines go low. They remain low until two more falling edges of RGCK. Thus RAS remains high for one to two periods of RGCK after M2 goes low, and stays low for two periods. In order to obtain the minimum delay from M2 going low to RAS going low, M2 should go low trescribed before the falling edge of RGCK.

The Refresh Request on RFI/O is terminated as RAS goes low. This signal may be used to end the refresh earlier than it normally would as described above. If M2 is pulled high

while the RAS lines are low, then the RASs go high t<sub>RFRH</sub> later. The designer must be careful, however, not to violate the minimum RAS low time of the DRAMs. He must also guarantee that the minimum RAS precharge time is not violated during a transition from mode 1 to mode 5 when an access is desired immediately following a refresh.

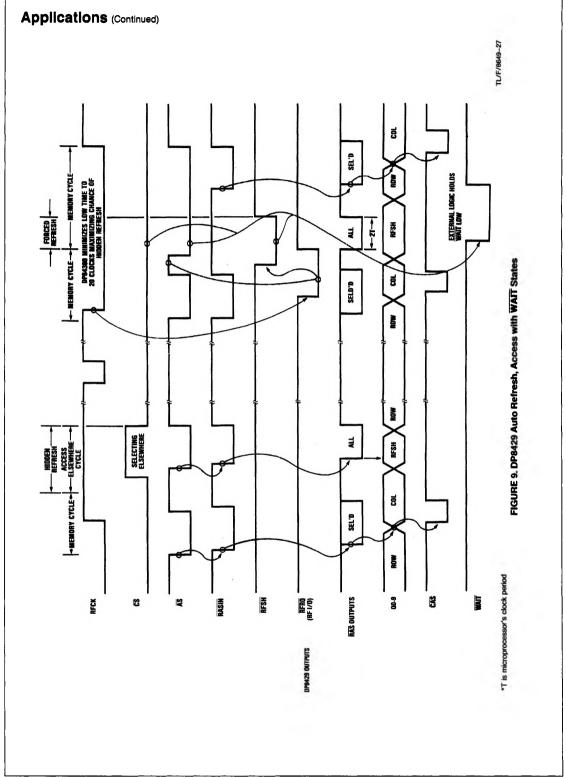

If the processor tries to access memory while the DP8429 is in mode 1, WAIT states should be inserted into the processor cycles until the DP8429 is back in mode 5 and the desired access has been accomplished (see *Figure 9*).

Instead of using WAIT states to delay accesses when refreshing, HOLD states could be used as follows. RFRQ could be connected to a HOLD or Bus Request input to the system. When convenient, the system acknowledges the HOLD or Bus Request by pulling M2 low. Using this scheme, HOLD will end as the RAS lines go low (RFI/O goes high). Thus, there must be sufficient delay from the time HOLD goes high to the DP8429 returning to mode 5, so that the RAS low time of the DRAMs isn't violated as described earlier (see Figure 3 for mode 1 refresh with Hold states).

To perform a forced refresh the system will be inactive for about four periods of RGCK. For a frequency of 10 MHz, this is 400 ns. To refresh 128 rows every 2 ms an average of about one refresh per 16  $\mu s$  is required. With a RFCK period of 16  $\mu s$  and RGCK period of 100 ns, DRAM accesses are delayed due to refresh only 2.5% of the time. If using the Hidden Refresh available in mode 5 (refreshing with RFCK high) this percentage will be even lower.

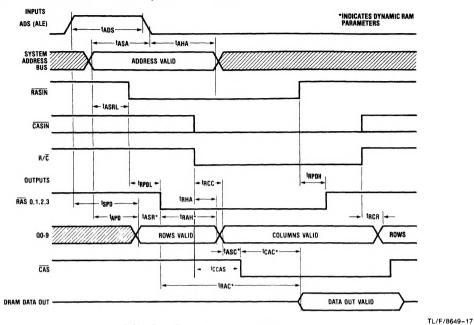

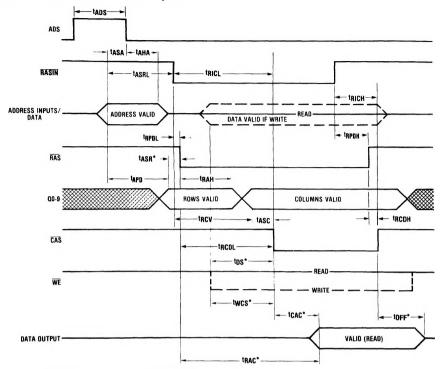

#### MODE 4 - EXTERNALLY CONTROLLED ACCESS

In this mode all control signal outputs can be controlled directly by the corresponding control input. The enabled RAS output follows RASIN, CAS follows CASIN (with R/C low), WE follows WIN and R/C determines whether the row or the column inputs are enabled to the address outputs (see Figure 4).

With R/C high, the row address latch contents are enabled onto the address bus. RAS going low strobes the row address into the DRAMs. After waiting to allow for sufficient row-address hold time (t<sub>RAH</sub>) after RAS goes low, R/C can go low to enable the column address latch contents onto the address bus. When the column address is valid, CAS going low will strobe it into the DRAMs. WIN determines whether the cycle is a read, write or read-modify-write access. Refer to Figures 5a and 5b for typical Read and Write timing using mode 4.

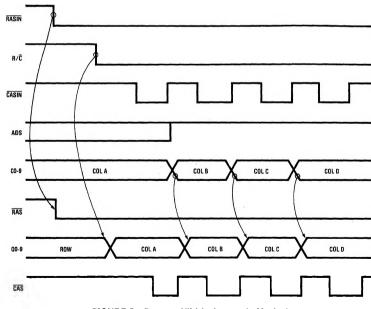

Page or Nibble mode may be performed by toggling CASIN once the initial access has been completed. In the case of page mode the column address must be changed before

TL/F/8649-16

FIGURE 4. Typical Application of DP8429 Using External Control Access and Refresh in Modes 0 and 4

\_\_\_\_

FIGURE 5a. Read Cycle Timing (Mode 4)

FIGURE 5b. Write Cycle Timing (Mode 4)

TL/F/8649-18

CASIN goes low to access a new memory location (see Figure 5c). Parameter t<sub>CPdif</sub> has been specified in order that users may easily determine minimum CAS pulse widths when CASIN is toggling.

#### **AUTOMATIC CAS GENERATION**

CAS is held high when R/C is high even if CASIN is low. If CASIN is low when R/C goes low, CAS goes low automatically, tasc after the column address is valid. This feature eliminates the need for an externally derived CASIN signal to control CAS when performing a simple access (Figure 5a demonstrates Auto-CAS generation in mode 4). Page or nibble accessing may be performed as shown in Figure 5c even if CAS is generated automatically for the initial access.

#### **FASTEST MEMORY ACCESS**

The fastest Mode 4 access is achieved by using the automatic  $\overline{\text{CAS}}$  feature and external delay line to generate the required delay between  $\overline{\text{RASIN}}$  and  $R/\overline{\text{C}}$ . The amount of delay required depends on the minimum  $t_{\text{RAH}}$  of the DRAMs being used. The DP8429 parameter  $t_{\text{DIF1}}$  has been specified in order that the delay between  $\overline{\text{RASIN}}$  and  $R/\overline{\text{C}}$  may be minimized.

$t_{DIF1} = MAXIMUM (t_{RPDL} - t_{RHA})$

where t<sub>RPDL</sub> = RASIN to RAS delay

and  $t_{RHA} = row$  address held from  $R/\overline{C}$  going low.

The delay between  $\overline{\text{RASIN}}$  and  $\text{R}/\overline{\text{C}}$  that guarantees the specified DRAM  $t_{\text{RAH}}$  is given by

MINIMUM  $\overline{RASIN}$  to  $R/\overline{C} = t_{DIF1} + t_{RAH}$ .

#### Example

In an application using DRAMs that require a minimum  $t_{RAH}$  of 15 ns, the following demonstrates how the maximum RASIN to CAS time is determined.

With  $t_{DIF1}$  (from Switching Characteristics) = 7 ns,  $\overline{RASIN}$  to  $R/\overline{C}$  delay = 7 ns + 15 ns = 22 ns.

A delay line of 25 ns will be sufficient.

With Auto-CAS generation, the maximum delay from R/C to CAS (loaded with 600 pF) is 46 ns. Thus the maximum RASIN to CAS time is 71 ns, under the given conditions.

With a maximum RASIN to RAS time (t<sub>RPDL</sub>) of 20 ns, the maximum RAS to CAS time is about 51 ns. Most DRAMs with a 15 ns minimum t<sub>RAH</sub> have a maximum t<sub>RCD</sub> of about 60 ns. Thus memory accesses are likely to be RAS limited instead of CAS limited. In other words, memory access time is limited by DRAM performance, not controller performance.

#### **REFRESHING IN CONJUNCTION WITH MODE 4**

If using mode 4 to access memory, mode 0 (externally controlled refresh) must be used for all refreshing.

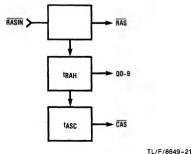

#### MODE 5 - AUTOMATIC ACCESS WITH HIDDEN RE-FRESHING CAPABILITY

Automatic-Access has two advantages over the externally controlled access (mode 4). First, RAS, CAS and the row to column change are all derived internally from one input signal, RASIN. Thus the need for an external delay line (see mode 4) is eliminated.

Secondly, since R/C and CASIN are not needed to generate the row to column change and CAS, these pins can be used for the automatic refreshing function.

#### **AUTOMATIC ACCESS CONTROL**

Mode 5 of the DP8429 makes accessing Dynamic RAM nearly as easy as accessing static RAM. Once row and column addresses are valid (latched on the DP8429 if necessary), RASIN going low is all that is required to perform the memory access.

FIGURE 5c. Page or Nibble Access in Mode 4

TL/F/8649-19

\*Indicates Dynamic RAM Parameters

#### FIGURE 6. Mode 5 Timing

TL/F/8649-20

(Refer to Figure 6) In mode 5 the selected RAS follows RASIN immediately, as in mode 4, to strobe the row address into the DRAMs. The row address remains valid on the DP8429 address outputs long enough to meet the  $t_{RAH}$  requirement of the DRAMs (pin 4, RAHS, of the DP8429 allows the user two choices of  $t_{RAH}$ ). Next, the column address replaces the row address on the address outputs and CAS goes low to strobe the columns into the DRAMs.  $\overline{\text{WIN}}$  determines whether a read, write or read-modify-write is done.

The diagram below illustrates mode 5 automatic control signal generation.

# REFRESHING IN CONJUNCTION WITH MODE 5

When using mode 5 to perform memory accesses, refreshing may be accomplished:

(a) externally (in mode 0 or mode 1)

- b) by a combination of mode 5 (hidden refresh) and mode 1 (auto-refresh)

- or (c) by a combination of mode 5 and mode 0

- (a) Externally Controlled Refreshing in Mode 0 or Mode 1 All refreshing may be accomplished using external refreshes in either mode 0 or mode 1 with R/ $\overline{C}$  (RFCK) tied high (see mode 0 and mode 1 descriptions). If this is desired, the system determines when a refresh will be performed, puts the DP8429 in the appropriate mode, and controls the  $\overline{RASIN}$  signals directly with  $\overline{RASIN}$ . The on-chip refresh counter is enabled to the address outputs of the DP8429 when the refresh mode is entered, and increments when  $\overline{RASIN}$  goes high at the completion of the refresh.

- (b) Mode 5 Refreshing (hidden) with Mode 1 refreshing (auto)

(Refer to Figure 7a) If RFCK is tied to a clock (see mode 1 description), RFI/O becomes a refresh request output and goes low following RFCK going low if no refresh occurred while RFCK was high. Refreshes may be performed in mode 5 when the DP8429 is not selected for access (CS is high) and RFCK is high. If these conditions exist the refresh counter contents appear on the DP8429 address outputs and all RAS lines follow RASIN so that if RASIN goes low (an access other than through the DP8429 occurs), all RAS lines go low to perform the refresh. The DP8429 allows only one refresh of this type for each period of RFCK, since RFCK should be fast enough such that one refresh per period is sufficient to meet the DRAM refresh requirement.

Once it is started, a hidden refresh will continue even if RFCK goes low. However,  $\overline{\text{CS}}$  must be high throughout the refresh (until  $\overline{\text{RASIN}}$  goes high).

These hidden refreshes are valuable in that they do not delay accesses. When determining the duty cycle of RFCK, the high time should be maximized in order to maximize the probability of hidden refreshes. If a hidden refresh doesn't happen, then a refresh request will occur on RFI/O when RFCK goes low. After receiving the request, the system must perform a refresh while RFCK is low. This may be done by going to mode 1 and allowing an automatic refresh (see mode 1 description). This refresh must be completed while RFCK is low, thus the RFCK low time is determined by the worst-case time required by the system to respond to a refresh request.

(c) Mode 5 Refresh (Hidden Refresh) with mode 0 Refresh (External Refresh)

This refresh scheme is identical to that in (b) except that after receiving a refresh request, mode 0 is entered to do the refresh (see mode 0 description). The refresh request is terminated (RFI/O goes high) as soon as mode 0 is entered. This method requires more control than using mode 1 (auto-refresh), however, it may be desirable if the mode 1 refresh time is considered to be excessive.

#### Example

Figure 7b demonstrates how a system designer would use the DP8429 in mode 5 based on certain characteristics of his system.

System Characteristics:

- 1) DRAM used has min t<sub>RAH</sub> requirement of 15 ns and min t<sub>ASR</sub> of 0 ns

- DRAM address is valid from time T<sub>V</sub> to the end of the memory cycle

- four banks of twenty-two 256k memory chips each are being driven

Using the DP8429 (see Figure 7b):

- 1) Tie pin 4 (RAHS) high to guarantee a 15 ns minimum t<sub>RAH</sub> which is sufficient for the DRAMs being used

- Generate RASIN no earlier than time T<sub>V</sub> + t<sub>ASRL</sub> (see switching characteristics), so that the row address is valid on the DRAM address inputs before RAS occurs

- 3) Tie ADS high since latching the DRAM address on the DP8429 is not necessary

- 4) Connect the first 20 system address bits to R0-R9 and C0-C9, and bits 21 and 22 to B0 and B1

- 5) Connect each RAS output of the DP8429 to the RAS inputs of the DRAMs of one bank of the memory array; connect Q0-Q9 of the DP8429 to A0-A9 of all DRAMs; connect CAS of the DP8429 to CAS of all the DRAMs

Figure 7c illustrates a similar example using the DP8428 to drive two 32-bit banks.

TL/F/8649-22

FIGURE 7a. Hidden Refreshing (Mode 5) and Forced Refreshing (Mode 1) Timing

FIGURE 7b. Typical Application of DP8429 Using Modes 5 and 1

TL/F/8649-23

# **Applications**

If one desires a memory interface containing the DP8429 that minimizes the number of external components required, modes 5 and 1 should be used. These two modes provide:

- Automatic access to memory (in mode 5 only one signal, RASIN, is required in order to access memory)

- Hidden refresh capability (refreshes are performed automatically while in mode 5 when non-local accesses are taking place, as determined by CS)

- Refresh request capability (if no hidden refresh took place while RFCK was high, a refresh request is generated at the RFI/O pin when RFCK goes high)

- 4) Automatic forced refresh (If a refresh request is generated while in mode 5, as described above, external logic should switch the DP8429 into mode 1 to do an automatic forced refresh. No other external control signals need be issued. WAIT states can be inserted into the processor machine cycles if the system tries to access memory while the DP8429 is in mode 1 doing a forced refresh).

Some items to be considered when integrating the DP8429 into a system design are:

1) The system designer should ensure that a DRAM access not be in progress when a refresh mode is entered. Simi-

- larly, one should not attempt to start an access while a refresh is in progress. The parameter  $t_{RFHRL}$  specifies the minimum time from  $\overline{RFSH}$  high to  $\overline{RASIN}$  going low to initiate an access.

- One should always guarantee that the DP8429 is enabled for access prior to initiating the access (see t<sub>CSRL1</sub>).

- One should bring RASIN low even during non-local access cycles when in mode 5 in order to maximize the chance of a hidden refresh occurring.

- 4) At lower frequencies (under 10 Mhz), it becomes increasingly important to differentiate between READ and WRITE cycles. RASIN generation during READ cycles can take place as soon as one knows that a processor READ access cycle has started. WRITE cycles, on the other hand, cannot start until one knows that the data to be written at the DRAM inputs will be valid a setup time before CAS (column address strobe) goes true at the DRAM inputs. Therefore, in general, READ cycles can be initiated earlier than WRITE cycles.

- 5) Many times it is possible to only add WAIT states during READ cycles and have no WAIT states during WRITE cycles. This is because it generally takes less time to write data into memory than to read data from memory.

#### **Applications** (Continued)

TL/F/8649-24

FIGURE 7c. Typical Application of DP8428 Using Modes 5 and 1

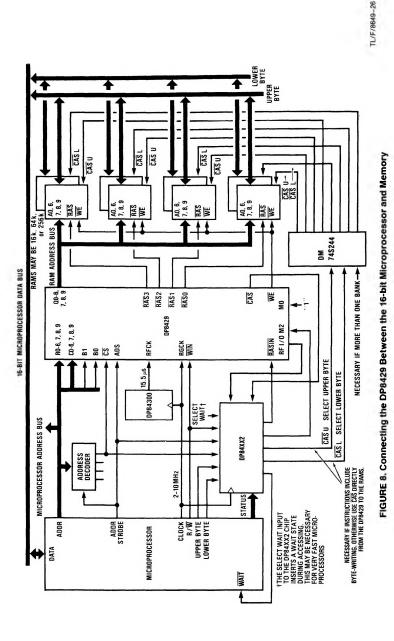

The DP84XX2 family of inexpensive preprogrammed medium Programmable Array Logic devices (PALs) have been developed to provide an easy interface between various microprocessors and the DP84XX family of DRAM controller/ drivers. These PALs interface to all the necessary control signals of the particular processor and the DP8429. The PAL controls the operation of the DP8429 in modes 5 and 1. while meeting all the critical timing considerations discussed above. The refresh clock, RFCK, may be divided down from the processor clock using an IC counter such as the DM74LS393 or the DP84300 programmable refresh timer. The DP84300 can provide RFCK periods ranging from 15.4 us to 15.6 us based on an input clock of 2 to 10 MHz. Figure 8 shows a general block diagram for a system using the DP8429 in modes 1 and 5. Figure 9 shows possible timing diagrams for such a system (using WAIT to prohibit access when refreshing). Although the DP84XX2 PALs are offered as standard peripheral devices for the DP84XX DRAM controller/drivers, the programming equations for these devices are provided so the user may make minor modifications for unique system requirements.

# ADVANTAGES OF DP8429 OVER A DISCRETE DYNAMIC RAM CONTROLLER

The DP8429 system solution takes up much less board space because everything is on one chip (latches, refresh counter, control logic, multiplexers, drivers, and internal delay lines).

- 2) Less effort is needed to design a memory system. The DP8429 has automatic modes (1 and 5) which require a minimum of external control logic. Also programmable array logic devices (PALs) have been designed which allow an easy interface to most popular microprocessors (Motorola 68000 family, National Semiconductor 32032 family, Intel 8086 family, and the Zilog Z8000 family).

- 3) Less skew in memory timing parameters because all critical components are on one chip (many discrete drivers specify a minimum on-chip skew under worst-case conditions, but this cannot be used if more then one driver is needed, such as would be the case in driving a large dynamic RAM array).

- 4) Our switching characteristics give the designer the critical timing specifications based on TTL output levels (low = 0.8V, high = 2.4V) at a specified load capacitance. All timing parameters are specified on the DP8429:

- A) driving 88 DRAM's over a temperature range of 0-70 degrees centigrade (no extra drivers are needed).

- B) under worst-case driving conditions with all outputs switching simultaneously (most discrete drivers on the market specify worst-case conditions with only one output switching at a time; this is not a true worst-case condition!).

# **Switching Characteristics**

All A. C. parameters are specified with the equivalent load capacitances, including traces, of 88 DRAMs organized as 4 banks of 22 DRAMs each. Maximums are based on worst-case conditions including all outputs switching simultaneously. This, in many cases, results in the AC valves shown in the DP84XX DRAM controller data sheet being much looser than true worst case maximum AC delays. The system designer should estimate the DP8429 load in his/her application, and modify the appropriate A. C. parameters using the graph in Figure 10. Two example calculations are provided below.

TL/F/8649-28

FIGURE 10. Change in Propagation Delay relative to "true" (application) load minus AC specified data sheet load

#### Examples

A mode 4 user driving 2 banks of DRAM has the following loading conditions:

CAS - 300 pF Q0-Q9 - 250 pF RAS - 150 pF

A.C. parameters should be adjusted in accordance with *Figure 10* and the specifications given for the 88 DRAM load as follows:

max  $t_{RPDL}$  = 20 ns - 0 ns = 20 ns (since  $\overline{RAS}$  loading is the same as that which is spec'ed)

$\max t_{CPDL} = 32 \text{ ns} - 7 \text{ ns} = 25 \text{ ns}$  $\max t_{CCAS} = 46 \text{ ns} - 7 \text{ ns} = 39 \text{ ns}$

$\max_{BCC} = 41 \text{ ns} - 6 \text{ ns} = 35 \text{ ns}$

min  $t_{\text{RHA}}$  is not significantly effected since it does not involve an output transition

Other parameters are adjusted in a similar manner.

2) A mode 5 user driving one bank of DRAM has the following loading conditions:

CAS - 120 pF

Q0-Q9 - 100 pF

RAS - 120 pF

A. C. parameters should be adjusted as follows:

with RAHS = "1",

$max t_{RICL} = 70 ns - 11 ns = 59 ns$

$max t_{RCDL} = 55 ns + 1 ns - 11 ns = 45 ns$

(the + 1 ns is due to lighter RAS loading; the - 11 ns is due to lighter CAS loading)

$min t_{RAH} = 15 ns + 1 ns = 16 ns$

The additional 1 ns is due to the fact that the RAS line is driving less (switching faster) than the load to which the 15 ns spec applies. The row address will remain valid for about the same time irregardless of address loading since it is considered to be not valid at the beginning of its transition.

TL/F/8649-29

FIGURE 11. Output Load Circuit

# Absolute Maximum Ratings (Note 1) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications. Supply Voltage, V<sub>CC</sub> 7.0V Storage Temperature Range -65°C to +150°C Input Voltage 5.5V

| Operating Conditions |                           |      |      |       |  |  |  |

|----------------------|---------------------------|------|------|-------|--|--|--|

| •                    | •                         | Min  | Max  | Units |  |  |  |

| $V_{CC}$ $T_A$       | Supply Voltage<br>Ambient | 4.50 | 5.50 | V     |  |  |  |

|                      | Temperature               | 0    | + 70 | °C    |  |  |  |

# **Electrical Characteristics** $V_{CC} = 5.0V \pm 10\%, 0^{\circ}C \le T_{A} \le 70^{\circ}C$ unless otherwise noted (Note 2)

150 mA

300°C

| Symbol             | Parameter                          | Conditions                          | Min | Тур   | Max   | Units |

|--------------------|------------------------------------|-------------------------------------|-----|-------|-------|-------|

| V <sub>C</sub>     | Input Clamp Voltage                | $V_{CC} = Min, I_C = -12 mA$        |     | - 0.8 | - 1.2 | V     |

| liH                | Input High Current for all Inputs  | $V_{ N} = 2.5V$                     |     | 2.0   | 100   | μА    |

| I <sub>I</sub> RSI | Output Load Current for RFI/O      | V <sub>IN</sub> = 0.5V, Output high |     | -0.7  | -1.5  | mA    |

| I <sub>IL1</sub>   | Input Low Current for all Inputs** | V <sub>IN</sub> = 0.5V              |     | -0.02 | -0.25 | mA    |

| I <sub>IL2</sub>   | ADS, R/C, CS, M2, RASIN            | V <sub>IN</sub> = 0.5V              |     | -0.05 | -0.5  | mA    |

| V <sub>IL</sub>    | Input Low Threshold                |                                     |     |       | 0.8   | V     |

| V <sub>IH</sub>    | Input High Threshold               |                                     | 2.0 |       |       | V     |

| V <sub>OL1</sub>   | Output Low Voltage*                | I <sub>OL</sub> = 20 mA             |     | 0.3   | 0.5   | V     |

| V <sub>OL2</sub>   | Output Low Voltage for RFI/O       | I <sub>OL</sub> = 8 mA              |     | 0.3   | 0.5   | V     |

| V <sub>OH1</sub>   | Output High Voltage*               | $I_{OH} = -1 \text{ mA}$            | 2.4 | 3.5   |       | V     |

| V <sub>OH2</sub>   | Output High Voltage for RFI/O      | I <sub>OH</sub> = - 100 μA          | 2.4 | 3.5   |       | V     |

| I <sub>1D</sub>    | Output High Drive Current*         | V <sub>OUT</sub> = 0.8V (Note 3)    | -50 | - 200 |       | mA    |

| loD                | Output Low Drive Current*          | V <sub>OUT</sub> = 2.4V (Note 3)    | 50  | 200   |       | mA    |

| Icc                | Supply Current                     | V <sub>CC</sub> = Max               |     | 150   | 240   | mA    |

<sup>\*</sup>Except RFI/O

**Output Current**

Lead Temp. (Soldering, 10 seconds)

# **Switching Characteristics: DP8428 and DP8429**

$V_{CC} = 5.0V \pm 10\%$ , 0°C  $\leq T_A \leq 70$ °C unless otherwise noted (Notes 2, 4, 5), the output load capacitance is typical for 4 banks of 22 DRAMs each or 88 DRAMs, including trace capacitance.

\* These values are Q0-Q9,  $C_L=500$  pF;  $\overline{RAS}0-\overline{RAS}3$ ,  $C_L=150$  pF;  $\overline{WE}$ ,  $C_L=500$  pF;  $\overline{CAS}$ ,  $C_L=600$  pF;  $RL=500\Omega$  unless otherwise noted. See *Figure 11* for test load. Maximum propagation delays are specified with all outputs switching.

#### \*\* Preliminary

| Symbol             | Access Parameter                   | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | *CL |     | **All $C_L = 50 pF$ |     | Units |

|--------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------|-----|-------|

|                    |                                    | The second distriction of the second | Min | Max | Min                 | Max |       |

| t <sub>RICL0</sub> | RASIN to CAS Low Delay (RAHS = 0)  | Figure 6<br>DP8428-80/29-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57  | 97  | 42                  | 85  | ns    |

| t <sub>RICL0</sub> | RASIN to CAS Low Delay (RAHS = 0)  | Figure 6<br>DP8428-70/29-70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57  | 87  | 42                  | 75  | ns    |

| t <sub>RICL1</sub> | RASIN to CAS Low Delay (RAHS = 1)  | Figure 6<br>DP8428-80/29-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48  | 80  | 35                  | 68  | ns    |

| t <sub>RICL1</sub> | RASIN to CAS Low Delay (RAHS = 1)  | Figure 6<br>DP8428-70/29-70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48  | 70  | 35                  | 58  | ns    |

| t <sub>RICH</sub>  | RASIN to CAS High Delay            | Figure 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 37  |                     |     | ns    |

| t <sub>RCDL0</sub> | RAS to CAS Low Delay<br>(RAHS = 0) | Figure 6<br>DP8428-80/29-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43  | 80  |                     |     | ns    |

| †RCDL0             | RAS to CAS Low Delay<br>(RAHS = 0) | Figure 6<br>DP8428-70/29-70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43  | 72  |                     |     | ns    |

<sup>\*\*</sup>Except RFI/O, ADS, R/C, CS, M2, RASIN

# Switching Characteristics: DP8428 and DP8429 (Continued)

$V_{CC} = 5.0V \pm 10\%$ , 0°C  $\leq T_A \leq 70$ °C unless otherwise noted (Notes 2, 4, 5), the output load capacitance is typical for 4 banks of 22 DRAMs each or 88 DRAMs, including trace capacitance.

- \* These values are Q0-Q9,  $C_L=500$  pF;  $\overline{RAS0}-\overline{RAS3}$ ,  $C_L=150$  pF;  $\overline{WE}$ ,  $C_L=500$  pF;  $\overline{CAS}$ ,  $C_L=600$  pF;  $RL=500\Omega$  unless otherwise noted. See *Figure 11* for test load. Maximum propagation delays are specified with all outputs switching.

- \*\* Preliminary

| Symbol             | Access Parameter                                    | Condition                    | *CL |     | **All C <sub>L</sub> = 50 pF |     | Units |

|--------------------|-----------------------------------------------------|------------------------------|-----|-----|------------------------------|-----|-------|

| Symbol             | Access Farameter                                    | Condition                    | Min | Max | Min                          | Max | Units |

| t <sub>RCDL1</sub> | RAS to CAS Low Delay (RAHS = 1)                     | Figure 6<br>DP8428-80/29-80  | 34  | 63  |                              |     | ns    |

| t <sub>RCDL1</sub> | RAS to CAS Low Delay (RAHS = 1)                     | Figure 6<br>DP8428-70/29-70  | 34  | 55  |                              |     | ns    |

| <sup>t</sup> RCDH  | RAS to CAS High Delay                               | Figure 6                     |     | 22  |                              |     | ns    |

| t <sub>RAH0</sub>  | Row Address Hold Time<br>(RAHS = 0, Mode 5)         | Figure 6                     | 25  |     | 25                           |     | ns    |

| t <sub>RAH1</sub>  | Row Address Hold Time<br>(RAHS = 1, Mode 5)         | Figure 6                     | 15  |     | 15                           |     | ns    |

| tasc               | Column Address Set-up Time<br>(Mode 5)              | Figure 6                     | 0   |     | 0                            |     | ns    |

| t <sub>RCV0</sub>  | RASIN to Column Address<br>Valid (RAHS = 0, Mode 5) | Figure 6<br>DP8428-80/29-80  |     | 94  |                              |     | ns    |

| t <sub>RCV0</sub>  | RASIN to Column Address<br>Valid (RAHS = 0, Mode 5) | Figure 6<br>DP8428-70/29-70  |     | 85  |                              |     | ns    |

| t <sub>RCV1</sub>  | RASIN to Column Address<br>Valid (RAHS = 1, Mode 5) | Figure 6<br>DP8428-80/29-80  |     | 76  |                              |     | ns    |

| t <sub>RCV1</sub>  | RASIN to Column Address<br>Valid (RAHS = 1, Mode 5) | Figure 6<br>DP8428-70/29-70  |     | 68  |                              |     | ns    |

| tRPDL              | RASIN to RAS Low Delay                              | Figures 5a, 5b, 6            |     | 21  |                              | 18  | ns    |

| tRPDH              | RASIN to RAS High Delay                             | Figures 5a, 5b, 6            |     | 20  |                              | 17  | ns    |

| tASRL              | Address Set-up to RASIN low                         | Figures 5a, 5b, 6            | 13  |     |                              |     | ns    |

| tAPD               | Address Input to Output<br>Delay                    | Figures 5a, 5b, 6            |     | 36  |                              | 25  | ns    |

| tspD               | Address Strobe High to<br>Address Output Valid      | Figures 5a, 5b               |     | 48  |                              |     | ns    |

| tasa               | Address Set-up Time to ADS                          | Figures 5a, 5b, 6            | 5   |     |                              |     | ns    |

| t <sub>AHA</sub>   | Address Hold Time from ADS                          | Figures 5a, 5b, 6            | 10  |     |                              |     | ns    |

| tADS               | Address Strobe Pulse Width                          | Figures 5a, 5b, 6            | 26  |     |                              |     | ns    |

| twpp               | WIN to WE Output Delay                              | Figure 5b                    |     | 28  |                              |     | ns    |

| tCPDL              | CASIN to CAS Low Delay<br>(R/C low, Mode 4)         | Figure 5b                    | 17  | 33  |                              |     | ns    |

| tCPDH              | CASIN to CAS High Delay (R/C low, Mode 4)           | Figure 5b                    | 13  | 33  |                              |     | ns    |

| tCPdif             | tCPDL - tCPDH                                       | See Mode 4<br>Description    |     | 13  |                              |     | ns    |

| tRCC               | Column Select to Column<br>Address Valid            | Figure 5a                    |     | 41  |                              |     | ns    |

| t <sub>RCR</sub>   | Row Select to Row<br>Address Valid                  | Figures 5a, 5b               |     | 45  |                              |     | ns    |

| t <sub>RHA</sub>   | Row Address Held from<br>Column Select              | Figure 5a                    | 7   |     |                              |     | ns    |

| tccas              | R/C Low to CAS Low Delay<br>(CASIN Low, Mode 4)     | Figure 5a<br>DP8428-80/29-80 |     | 50  |                              |     | ns    |

| tccas              | R/C Low to CAS Low Delay<br>(CASIN Low, Mode 4)     | Figure 5a<br>DP8428-70/29-70 |     | 46  |                              |     | ns    |

| t <sub>DIF1</sub>  | Maximum (t <sub>RPDL</sub> - t <sub>RHA</sub> )     | See Mode 4<br>Description    |     | 7   |                              |     | ns    |

| t <sub>DIF2</sub>  | Maximum (t <sub>BCC</sub> - t <sub>CPDL</sub> )     |                              |     | 13  |                              |     | ns    |

# Switching Characteristics: DP8428 and DP8429 (Continued)

$V_{CC}$  = 5.0V ± 10%, 0°C <  $T_A$  < 70°C unless otherwise noted (Notes 2, 4, 5). The output load capacitance is typical for 4 banks of 22 DRAMs each or 88 DRAMs, including trace capacitance.

- \* These values are Q0-Q9,  $C_L=500~pF$ ;  $\overline{RAS0}-\overline{RAS3}$ ,  $C_L=150~pF$ ;  $\overline{WE}$ ,  $C_L=500~pF$ ;  $\overline{CAS}$ ,  $C_L=600~pF$ ;  $RL=500\Omega$  unless otherwise noted. See *Figure 11* for test load. Maximum propagation delays are specified with all outputs switching.

- \*\*Preliminary

| Symbol                | Refresh Parameter                                                                | Condition                                      | *   | *CL **All C <sub>L</sub> = 50 |     | **All C <sub>L</sub> = 50 pF |       |

|-----------------------|----------------------------------------------------------------------------------|------------------------------------------------|-----|-------------------------------|-----|------------------------------|-------|

| Oyboi                 |                                                                                  |                                                | Min | Max                           | Min | Max                          | Units |

| tRC                   | Refresh Cycle Period                                                             | Figure 2a                                      | 100 |                               |     |                              | ns    |

| <sup>†</sup> RASINL,H | Pulse Width of RASIN during Refresh                                              | Figure 2a                                      | 50  |                               |     |                              | ns    |

| tRFPDL0               | RASIN to RAS Low Delay during Refresh (Mode 0)                                   | Figure 2a                                      |     | 28                            |     |                              | ns    |

| t <sub>RFPDL5</sub>   | RASIN to RAS Low Delay during Hidden Refresh                                     | Figure 7                                       |     | 38                            |     |                              | ns    |

| t <sub>RFPDH0</sub>   | RASIN to RAS High Delay during Refresh (Mode 0)                                  | Figure 2a                                      |     | 35                            |     |                              | ns    |

| tRFPDH5               | RASIN to RAS High Delay during Hidden Refresh                                    | Figure 7                                       |     | 44                            |     |                              | ns    |

| <sup>†</sup> RFLCT    | RFSH Low to Counter<br>Address Valid                                             | Figures 2a, 3<br>ĈŜ = X                        |     | 38                            |     |                              | ns    |

| <sup>t</sup> RFLRL    | RFSH Low Set-up to RASIN<br>Low (Mode 0), to get<br>Minimum t <sub>ASR</sub> = 0 | Figure 2a                                      | 12  |                               |     |                              | ns    |

| <sup>t</sup> RFHRL    | RFSH High Setup to Access RASIN Low                                              | Figure 3                                       | 25  |                               |     |                              | ns    |

| t <sub>RFHRV</sub>    | RFSH High to Row<br>Address Valid                                                | Figure 3                                       |     | 43                            |     |                              | ns    |

| t <sub>ROHNC</sub>    | RAS High to New Count<br>Valid                                                   | Figure 2a                                      |     | 42                            |     |                              | ns    |

| <sup>t</sup> RST      | Counter Reset Pulse Width                                                        | Figure 2a                                      | 60  |                               |     |                              | ns    |

| <sup>t</sup> CTL      | RFI/O Low to Counter<br>Outputs All Low                                          | Figure 2a                                      |     | 100                           |     | *                            | ns    |

| trfckl,H              | Minimum Pulse Width of RFCK                                                      | Figure 7                                       | 100 |                               |     |                              | ns    |

| Т                     | Period of RAS Generator<br>Clock                                                 | Figure 3                                       | 30  |                               |     |                              | ns    |

| <sup>†</sup> RGCKL    | Minimum Pulse Width Low of RGCK                                                  | Figure 3                                       | 15  |                               |     |                              | ns    |

| <sup>t</sup> RGCKH    | Minimum Pulse Width High of RGCK                                                 | Figure 3                                       | 15  |                               |     |                              | ns    |

| <sup>t</sup> FRQL     | RFCK Low to Forced RFRQ<br>(RFI/O) Low                                           | Figure 3<br>C <sub>L</sub> = 50 pF<br>RL = 35k |     | 66                            |     |                              | ns    |

| t <sub>FRQH</sub>     | RGCK Low to Forced RFRQ<br>High                                                  | Figure 3<br>C <sub>L</sub> = 50 pF<br>RL = 35k |     | 55                            |     |                              | ns    |

# Switching Characteristics: DP8428 and DP8429 (Continued)

$V_{CC} = 5.0V \pm 10\%$ , 0°C  $\leq T_A \leq 70$ °C unless otherwise noted (Notes 2, 4, 5). The output load capacitance is typical for 4 banks of 22 DRAMs each or 88 DRAMs, including trace capacitance.

\* These values are Q0-Q9,  $C_L = 500$  pF;  $\overline{RAS0}$ - $\overline{RAS3}$ ,  $C_L = 150$  pF;  $\overline{WE}$ ,  $C_L = 500$  pF;  $\overline{CAS}$ ,  $C_L = 600$  pF;  $RL = 500\Omega$  unless otherwise noted. See *Figure 11* for test load. Maximum propagation delays are specified with all outputs switching.

\*\*Preliminary

| Symbol               | Refresh Parameter                                                                  | Condition                               | •   | CL  | **All C <sub>L</sub> = 50 pF |     | Units |

|----------------------|------------------------------------------------------------------------------------|-----------------------------------------|-----|-----|------------------------------|-----|-------|

| Symbol               | Non oan Farameter                                                                  | Condition                               | Min | Max | Min                          | Max | J     |

| tRGRL                | RGCK Low to RAS Low                                                                | Figure 3                                | 20  | 41  |                              |     | ns    |

| t <sub>RGRH</sub>    | RGCK Low to RAS High                                                               | Figure 3                                | 20  | 48  |                              |     | ns    |

| tRQHRF.              | RFSH Hold Time from RGCK                                                           | Figure 3                                | 2T  |     |                              |     | ns    |

| <sup>†</sup> RFRH    | RFSH High to RAS High<br>(Ending Forced Refresh<br>early)                          | (See Mode 1<br>Description)             |     | 42  |                              |     | ns    |

| tRFSRG               | RFSH Low Set-up to<br>RGCK Low (Mode 1)                                            | (See Mode 1<br>Description)<br>Figure 3 | 12  |     |                              |     | ns    |

| t <sub>CSHR</sub>    | CS High to RASIN Low for Hidden Refresh                                            | Figure 7                                | 10  |     |                              |     | ns    |

| tCSRL1<br>for DP8429 | CS Low to Access RASIN<br>Low (Using Mode 5 with<br>Auto Refresh Mode)             | Figure 3                                | 34  |     |                              |     | ns    |

| tCSRL1<br>for DP8428 | CS Low to Access RASIN<br>Low (Using Mode 5 with<br>Auto Refresh Mode)             | Figure 3                                | 5   |     |                              |     | ns    |

| tCSRL0               | CS Low to Access RASIN Low (Using Modes 4 or 5 with externally controlled Refresh) | (See Mode 5<br>Description)             | 5   |     |                              |     | ns    |

| t <sub>RKRL</sub>    | RFCK High to RASIN low for hidden Refresh                                          |                                         | 50  |     |                              |     | ns    |

Input Capacitance T<sub>A</sub> = 25°C (Note 2)

| Symbol          | Parameter                                 | Condition | Min | Тур | Max | Units |

|-----------------|-------------------------------------------|-----------|-----|-----|-----|-------|

| C <sub>IN</sub> | Input Capacitance ADS, R/C, CS, M2, RASIN |           |     | 8   |     | pF    |

| C <sub>IN</sub> | Input Capacitance All Other Inputs        |           |     | 5   |     | pF    |