# DP84522 Dynamic RAM Controller Interface Circuit for the 68020 CPU

### General Description

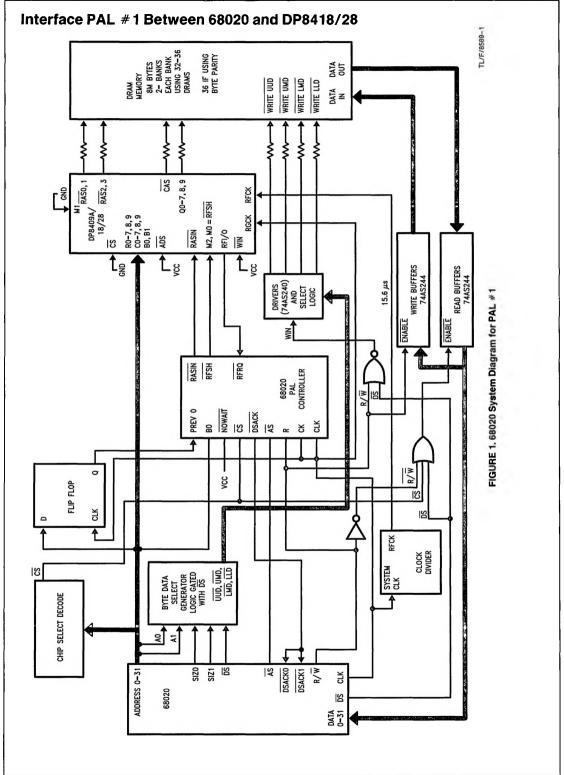

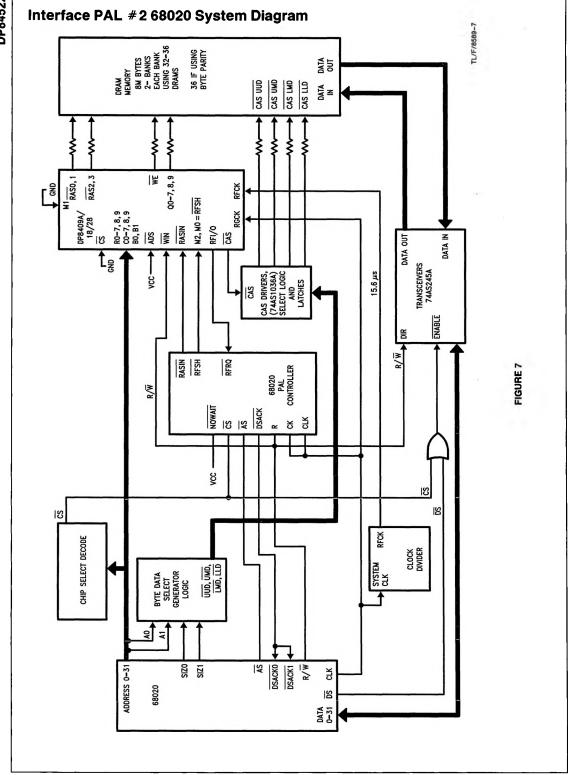

This is a Programmable Array Logic (PAL®) device designed to allow an easy interface between the 68020 microprocessor and the National Semiconductor DP8417, DP8418, DP8419, DP8428 or DP8429 dynamic memory controllers.

This PAL supplies all the control signals needed to perform memory read, write, and refresh operations up to a frequency of 16.7 MHz.

#### **Features**

- □ Provides a 3 or 4 chip solution for the 68020/DP8418 (or DP8428) dynamic RAM interface (1 or 2 PALs, DP8418, and clock divider)

- □ Works with all speed versions of the 68020 up to 16.7 MHz

- □ Allows operation of 68020 at 12.5 MHz with 1 WAIT state with standard 120 ns 256k DRAMs

- □ Controls DP8418/28 mode 5 accesses and mode 1 or 0 forced refreshes automatically

- Allows memory interleaving if desired

- □ CPU WAIT states are automatically inserted during contention between memory interleaving/DRAM accesses/ DRAM refreshes

- ☐ Uses standard National Semiconductor PALs (i.e., DMPAL16R4A; the user may want to use faster versions of these PALs at higher CPU operating frequen-

- □ The PAL programming equations are provided with comments for easy user modification to his specific requirements

# **Functional Description**

The following description applies only to the DP8418 or DP8428 since "RFI/O" going low initiates a mode 0 externally controlled forced refresh. This forced refresh resets the internal refresh request logic on the DP8418 or DP8428, but will not reset the internal logic on the DP8409A.

A memory cycle starts when chip select (CS) and the address strobe (AS) become true. RASIN is supplied from the PALs to the DP8418 DRAM controller, which then supplies RAS to the selected RAS bank. After the necessary row address hold time, the DP8418 switches the address outputs to the column address. The DP8418 then supplies the required CAS signal to the DRAM.

The first PAL (PAL #1) supports byte operations by producing four WRITE enables, one for each possible byte of the 32 bit word (upper, upper middle, lower middle, and lower write enable). These WRITE enables are produced externally from the 68020 "DATA STROBE" and "READ/WRITE"

outputs. Since it is possible that all WRITE cycles may be LATE WRITE cycles ("WRITE ENABLE" occurring after "COLUMN ADDRESS STROBE") memory buffers should be used instead of transceivers to separate the data in from the data out of the DRAMs.

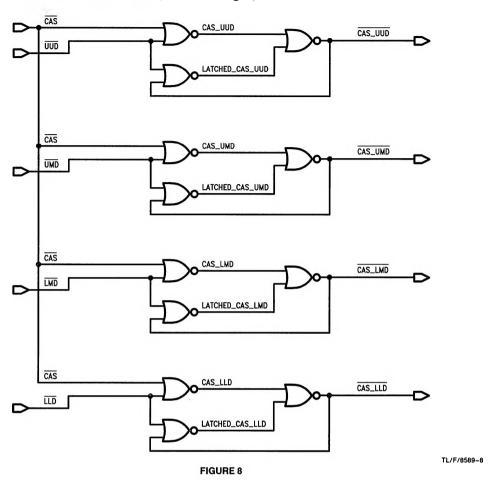

The second PAL (PAL #2) supports byte operations by producing four COLUMN ADDRESS STROBES, one for each of the possible bytes of the 32-bit word. This PAL terminates the DP8418 "RASIN" input early but holds the DRAM data valid by latching the byte "CAS's" externally. This method of supporting byte writes allows transceivers to be used, or to directly connect the DRAM data in and data out pins to the 68020 data bus I/O pins.

Hidden REFRESH cycles are not allowed in this set of PALs because of the need for adequate RAS precharge times in all circumstances and the desire not to be inserting WAIT states into access cycles of other system elements.

These PALs perform externally controlled forced refreshes automatically (mode 0). A refresh cycle occurs when the DP8418 input RFCK transitions low and the RFIO signal goes low requesting a refresh cycle. The PAL responds by pulling RFSH low (M2 and M0) if there are no current DRAM accesses in progress. If a DRAM access is in progress the PAL waits until the current access is completed before performing the forced refresh cycle. If an access is requested during the forced refresh cycle WAIT states are automatically inserted into the access cycle until the refresh cycle is completed and adequate RAS precharge has been completed. The pending DRAM access cycle is then performed. The input signal "NOWAIT" allows one to vary the amount of time required to do a refresh (see the description of the "NOWAIT" input in the pin description section). In one of the timing diagrams the "RFSH" output was tied to the "NOWAIT" input to decrease the length of the refresh cycle but still insert one wait state in normal DRAM access cycles (see Figure 5).

The first PAL (PAL #1) supports memory interleaving to guarantee adequate RAS precharge time during two consecutive accesses to the same DRAM bank. This is performed by looking at the lower address bit or bits. A2 and/or A3. If the processor is sequentially accessing the DRAM each RAS output will have plenty of precharge time. But if the system tries to access the same bank twice in a row the access will be delayed until adequate RAS precharge time has been met. During this time WAIT states will automatically be inserted into the pending access cycle.

The second PAL (PAL #2) guarantees adequate RAS precharge time (one and one half system clock periods) by ending the DP8418 "RASIN" input early. The DRAM data is held valid by externally latching the DRAM "CAS" input as explained earlier. This has the additional benefit of sim-

#### Functional Description (Continued)

plifying the memory interface of the 68020 by eliminating the external components needed for interleaving, though as one approaches 16.7 MHz the interleaving circuitry may again become necessary to guarantee adequate "RAS" precharge time.

For PAL #1 an external "D type" flip-flop or another PAL could be used for the support of memory interleaving. If one is not using memory interleaving (10 MHz or below) the "PREVO" input can be used for some other function and the equations of "RASIN" that employ "PREVO" can be adjusted.

The PAL equations for this interface are written in the National Semiconductor PLANTM format, which differs from the standard PALASMTM format.

**EXAMPLE: PLAN FORMAT**

/RASIN := RFSH\*/2D\*/AS

This translates as, "RASIN" is low after the rising edge of the input clock given that "RFSH" was high and "2D" was low and "AS" was low a setup time before the clock transitions high (here RASIN, 2D, and RFSH are outputs of the PAL and AS is an input).

**EXAMPLE: PALASM FORMAT**

RASIN := /RFSH\*2D\*AS

The above expression means the same as the PLAN format expression except it is written in PALASM format. In other words; "RASIN" will go low after the rising edge of the clock given that "RFSH" was high, "2D" was low, and "AS" was low a setup time before the clock transitions high (here RASIN, 2D, and RFSH are outputs of the PAL and AS is an input).

Depending on the specific type of PALs and logic used the user can calculate the speed requirements for the DRAM at the specified processor frequency as follows:

CALCULATION OF DRAM "tRAC" RAS ACCESS TIME AND "tGAC" CAS ACCESS TIME REQUIRED FOR A 12.5 MHz 68020, 1 WAIT STATE, MICROPROCESSOR SYSTEM

- #1) RASIN generation time = "S0" + "S1" + 1 combinational output delay of the PAL generating the "RASIN" output (assume DMPAL16R4B) = 80 ns + 15 ns = 95 ns maximum

- #2) RASIN to RAS out delay of the DP8418 = 20 ns maximum (used to determine "tRAC")

- #3) RASIN to CAS out delay of the DP8418 DRAM contoller driving a load of 2 banks of 256k DRAMs, each bank containing 36 (32 DRAMs plus byte parity) = 72 **DRAMs**

Since this is under the specified load in the data sheet (approximately 88 DRAMs) approximately 3 ns can be subtracted from the data sheet number, giving 80 ns -3 ns = 77 ns maximum (used to determine " $t_{CAC}$ ")

- #4) 74AS244 buffer delay = 7 ns maximum

- #5) Data setup time required from the falling edge of "S4" clock = 10 ns maximum

A normal 12.5 MHz 68020 access cycle (with 1 WAIT state inserted) contains 4 clock periods of 80 ns per period.

The required DRAM "tRAC" (row access time) can be calculated from

```

S0 + S1 + S2 + S3 + SW1 + SW2 + S4

(minimum 1/2 period) - #1 - #2 - #4 - #5

= 40 + 40 + 40 + 40 + 40 + 40 + 35

-95-20-7-10=143 \text{ ns}

```

The required DRAM "tcAc" (column access time) can be calculated from

```

S0 + S1 + S2 + S3 + SW1 + SW2 + S4

(minimum 1/2 period) - #1 - #3 - #4 - #5

= 40 + 40 + 40 + 40 + 40 + 40 + 35

-95-77-7-10=86 \text{ ns}

```

The DRAMs selected for this system must satisfy both the "tRAC and tCAC" requirements. Therefore the DRAMs must have a "tRAC" (row access time) less then or equal to 143 ns and a "t<sub>CAC</sub>" (column access time) less than or equal to 86 ns to be used in this system, under worst case conditions, for a 1 WAIT state 12.5 MHz 68020 system. Common 120 ns 64k or 256k DRAMs meet this specification. If one is using PAL #2, producing external "CAS's" and not using any external transceivers he could possibly use 150 ns DRAMs in the above example.

If one is using PAL #2, the calculated "tRAC" and "tCAC" may differ from the actual system values, depending upon the external circuitry used to produce the byte "CAS's". The DP8418 "RASIN-CAS" low will be approximately 10-15 ns less than the value given in the data sheet because of the small loading on the DP8418 "CAS" output. The external circuitry needed to produce the byte "CAS's" should be loaded such that the column address (from DP8418) is valid when "CAS" goes low. For this reason "RASIN-byte CAS" may be longer than the value used in the "tRAC, tCAC" calculations, and therefore may give a smaller "tRAC, tCAC" than was calculated.

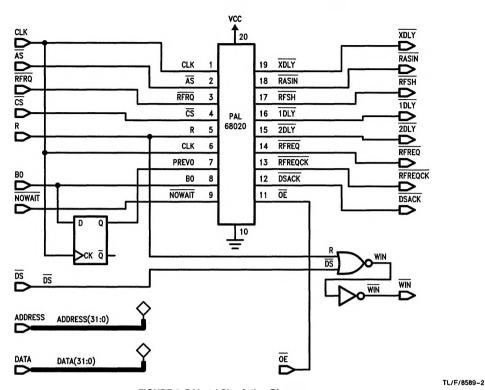

## 68020 PAL Inputs and Outputs

(Pin number of the PAL on the left)

PAL #1 Inputs

1) "CK" This is the system clock. 2) "AS" Address strobe from 68020.

3) "RFRQ" This is the refresh request from the DP8418.

4) "CS" This is the chip select (see system block diagram).

5) "R" READ/WRITE output pin from the 68020.

6) "CLK" The system clock.

7) "PREVO" This output holds the previously accessed DRAM "RAS" bank.

8) "B0" This input is the address bit "A2" and is used to determine which "RAS" bank the system is accessing.

9) "NOWAIT" This PAL always inserts one WAIT state into every 68020 access cycle. This input.

## 68020 PAL Inputs and Outputs (Continued)

if low, allows the DRAM to be accessed with no wait states inserted into the access cycle. This input also, if low during a refresh, shortens the length of the refresh cycle by one clock period. This causes the RAS pulse width (during a refresh) and the RAS precharge time (after a refresh) to be shorter.

11) "OE"

This input enables the PAL outputs.

PAL #1 Outputs

19) "XDLY"

This signal is used to guarantee one period of "RFSH" high to "RASIN" low time and to guarantee two periods of RAS precharge time in consecutive accesses to the same DRAM bank.

18) "RASIN"

This signal causes RAS (or RASs) to go low during a DRAM access or refresh.

17) "RFSH"

This signal initiates a DRAM Refresh.

16) "TDLY"

A delay that is used internally. A delay that is used internally.

15) "2DLY" 14) "RFREQ"

Refresh request (from the DP8418) syn-

chronized to the system clock.

13) "RFREQCK"

This input synchronizes "RFREQ" to the falling edge of the input system clock "CLK" and is used in arbitrating between refreshes and accesses (see

"RASIN" equations).

12) "DSACK"

This output goes to the 68020 "DSACKO, T" data acknowledge input. This output allows WAIT states to be inserted into DRAM access cycles during access/refresh/RAS precharge con-

tention.

### Interface PAL #1 Boolean Equations

This PAL will work up to 16.7 MHz with the 68020. This PAL uses mode 0 (M0 = M1 = M2 = low) for doing externally controlled forced refreshes, guaranteeing more than 2.5 periods of RGCK RAS pulse width ("NOWAIT" = high), If "NOWAIT" is low the refresh is shortened by one clock period. This PAL will only work with the DP8417/18/19/28/29 since it uses mode 0 to reset the RFSH request (RFIO) signal.

#### DMPAL16R4A

CS R CK AS RFRQ CLK PREVO BO TIAWON\ /OE /DSACK /RFREQCK /RFREQ /2DLY /1DLY /RFSH /RASIN /XDLY VCC

IF (VCC) /XDLY = RFSH\*/2DLY\*RASIN\*PREVO\*BO

+RFSH\*/2DLY\*RASIN\*/PREVO\*/BO

+/RFSH\*1DLY\*/2DLY\*/RASIN\*NOWAIT\*/CLK

+/RFSH\*1DLY\*2DLY\*RASIN\*RFREQ\*/NOWAIT

+/XDLY\*/RFSH\*RFREQ

+/XDLY\*RASIN\*/AS\*CLK

IF (VCC) /RASIN = /RFSH\*RFREQ\*/1DLY

+/RASIN\*/RFSH\*/2DLY\*XDLY

+RFSH\*RFREQCK\*/AS\*/CS\*PREVO\*/BO\*CLK

+RFSH\*RFREQCK\*/AS\*/CS\*/PREVO\*BO\*CLK

+RFSH\*RFREQCK\*/AS\*/CS\*2DLY\*XDLY\*CLK

+/RASIN\*RFSH\*/AS\*/CS

+/RASIN\*/CLK

IF (VCC) /RFREQCK = /RFREQ\*/CLK

+/RFREQCK\*/RFREQ

IF (/CS) /DSACK = /CS\*RFSH\*/RASIN\*NOWAIT\*/CLK ;One WAIT state

+/DSACK\*/CS\*RFSH\*/RASIN\*/AS

+/CS\*RFSH\*/AS\*/NOWAIT\*XDLY

/RFSH := /RFREQ\*RASIN\*/1DLY\*/2DLY

+/RFREQ\*RASIN\*1DLY

+/RFSH\*/RFREQ

+/RFSH\*/RASIN

+/RFSH\*/1DLY

/1DLY := /RFSH\*2DLY\*/RFREQ

+/RFSH\*/1DLY\*2DLY\*XDLY

+RFSH\*/RASIN

/2DLY := /RFSH\*/1DLY

+/RFSH\*2DLY\*/RFREQ\*/NOWAIT

+RFSH\*/RASIN\*/1DLY

+RFSH\*/RASIN\*/NOWAIT

/RFREQ := /RFRQ

;Same bank interleave

:Same bank interleave

;"/XDLY" low during RFSH

:"/XDLY" low during RFSH

:Hold "/XDLY" low

:Hold "/XDLY" low

:RFSH "/RASIN"

;Hold "/RASIN" low

:Start "/RASIN"

;Start "/RASIN"

:After idle states

:Hold "/RASIN" low

;Hold "/RASIN" low

:Start from falling clock

; edge

:Hold "/DSACK" low

;No WAIT state in access

;Start RFSH

:Start RFSH

:Hold RFSH low

:Hold RFSH low ;Hold RFSH low

;Start "/IDLY" during RFSH

;Continue "/IDLY" during RFSH ;Start "/IDLY" during /RASIN

;Start "/2DLY" during RFSH ;Shorten RFSH

;Start "/2DLY" during /RASIN

:Shorten access

;Synchronize to system clock

# Interface PAL #1 Between 68020 and DP8418/28 (Continued)

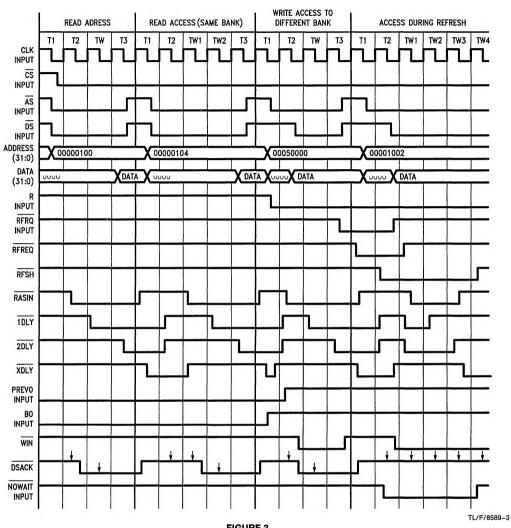

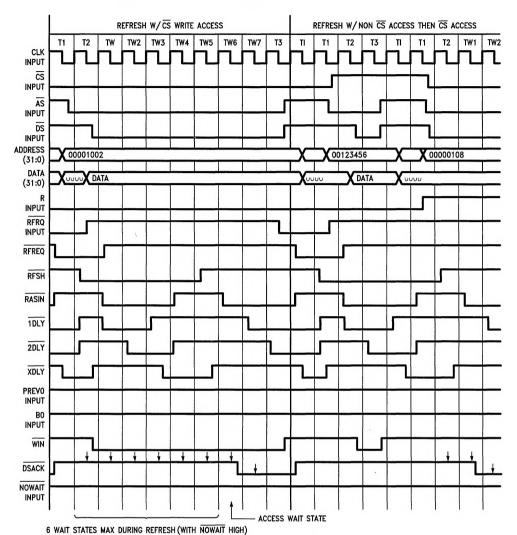

FIGURE 2. PAL #1 Simulation Diagram

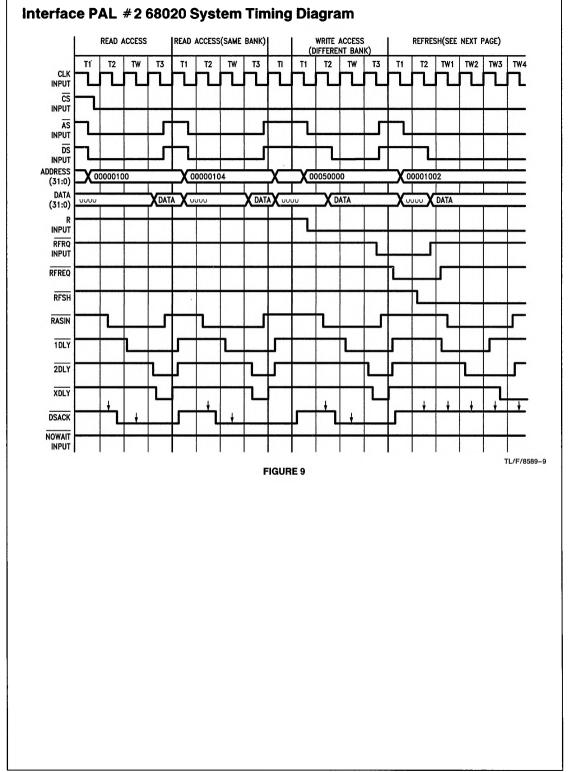

## Interface PAL #1 System Timing Diagram

FIGURE 3

# Interface PAL #1 System Timing Diagram (Continued)

FIGURE 4

TL/F/8589-4

TL/F/8589-5

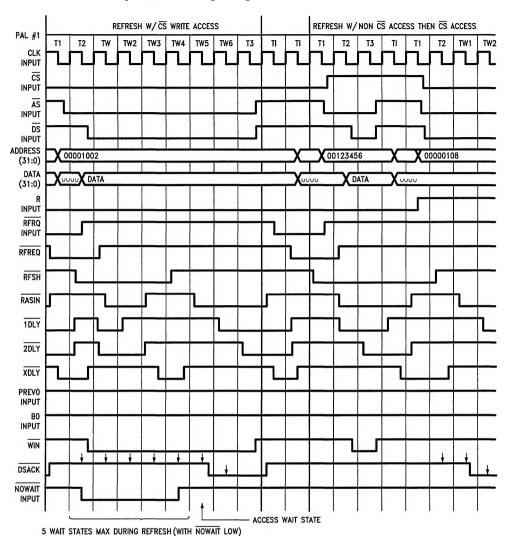

# Interface PAL #1 System Timing Diagram (Continued)

FIGURE 5

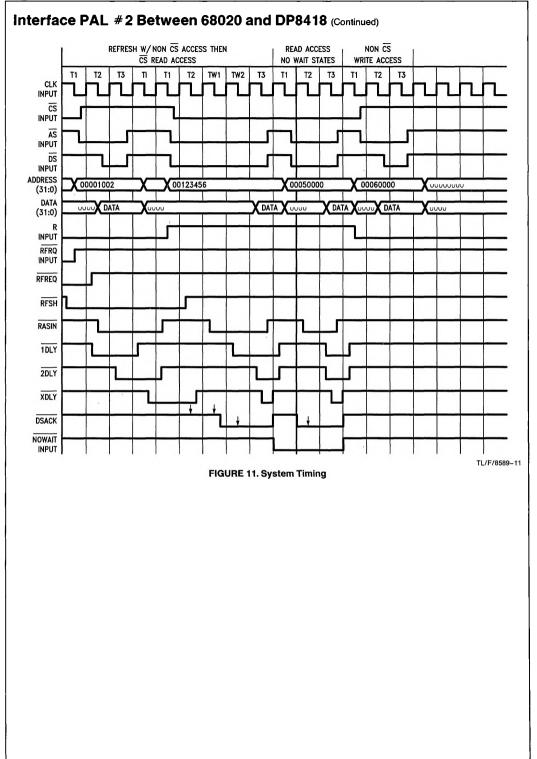

#### Interface PAL #1 System Timing Diagram (Continued) REFRESH W/NON CS ACCESS THEN READ ACCESS NON CS CS READ ACCESS NO WAIT STATES WRITE ACCESS T1 TW1 TW2 T1 T2 T3 TI T2 T3 T1 T2 **T3** T1 T2 T3 CLK INPUT $\overline{cs}$ INPUT AS INPUT DS INPUT ADDRESS 00001002 00123456 00050000 00060000 บุบบบบบบบ (31:0) DATA DATA XUUUU X DATA UUUU DATA DATA Y UUUU ใบบบบ UUUU (31:0)INPUT RFRQ INPUT RFREQ RFSH RASIN 1DLY 2DLY XDLY PREV0 INPUT во INPUT WIN DSACK NOWAIT INPUT TL/F/8589-6

FIGURE 6

#### Interface PAL #2 Boolean Equations

This PAL is similar to PAL #1 but ends "RASIN" one half period earlier than PAL #1 and relies on the external generation of byte "CAS's" to hold the data valid during 68020 READ access cycles.

DMPAL16R4A

CK /AS /RFRQ /CS R CLK NC1 NC2 /NOWAIT GND

/OE /DSACK /RFREQCK /RFREQ /2DLY /1DLY /RFSH /RASIN /XDLY VCC

IF (VCC) /XDLY = RFSH\*/2DLY\*/AS

+/RFSH\*1DLY\*/2DLY\*/RASIN\*NOWAIT\*/CLK

+/RFSH\*1DLY\*2DLY\*RASIN\*RFREQ\*/NOWAIT

+/RFSH\*/XDLY\*RFREQ

+/XDLY\*RASIN\*/AS\*CLK

IF (VCC) /RASIN = /RFSH\*RFREQ\*/1DLY

+/RFSH\*/RASIN\*/2DLY\*XDLY

+/RFSH\*/RASIN\*/CLK

+RFSH\*RFREQCK\*/AS\*/CS\*XDLY\*CLK

+RFSH\*RFREQCK\*/AS\*/CS\*2DLY\*XDLY\*CLK

+RFSH\*/RASIN\*/AS\*/CS\*XDLY

+RFSH\*/RASIN\*CLK

IF (VCC) /RFREQCK = /RFREQ\*/CLK

+/RFREQCK\*/RFREQ

IF (VCC) /DSACK = /CS\*RFSH\*/RASIN\*NOWAIT\*/CLK :One WAIT state

+/DSACK\*/CS\*RFSH\*/RASIN\*/AS

+/CS\*RFSH\*/AS\*/NOWAIT\*XDLY

/RFSH := /RFREQ\*RASIN\*/1DLY\*/2DLY

+/RFREQ\*RASIN\*1DLY

+/RFSH\*/RFREQ +/RFSH\*/RASIN

+/RFSH\*/1DLY

/1DLY := /RFSH\*2DLY\*/RFREQ

+/RFSH\*/lDLY\*2DLY\*XDLY

+RFSH\*/RASIN

/2DLY := /RFSH\*/1DLY

+/RFSH\*2DLY\*/RFREQ\*/NOWAIT

+RFSH\*/RASIN\*/1DLY

+RFSH\*/RASIN\*/NOWAIT

/RFREQ := /RFRQ

;"/XDLY" during access

;"/XDLY" during RFSH

;"/XDLY" during RFSH

;Hold "/XDLY" low

;Hold "/XDLY" low

:RFSH "/RASIN"

:Hold in RFSH

:Hold in RFSH

;Start "/RASIN"

:After idle states

:Hold "/RASIN" low

;Hold "/RASIN" low

;Start from falling clock

; edge

:Hold "/DSACK" low

;No WAIT state in access

:Start RFSH

:Start RFSH

;Hold RFSH low ;Hold RFSH low

;Hold RFSH low

:Start "/IDLY" during RFSH

;Continue "/IDLY" during RFSH

;Start "/1DLY" during /RASIN

;Start "/2DLY" during RFSH

;Shorten RFSH

;Start "/2DLY" during /RASIN

;Shorten access

;Synchronize to system clock

# Interface PAL #2 CAS Driver, Select Logic, and Latches

## Interface PAL #2 Between 68020 and DP8418

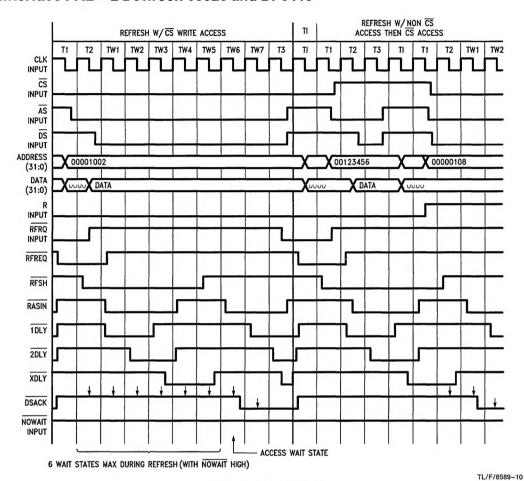

FIGURE 10. System Timing