# National Semiconductor

# DP8463B (2,7) ENDEC

# **General Description**

120

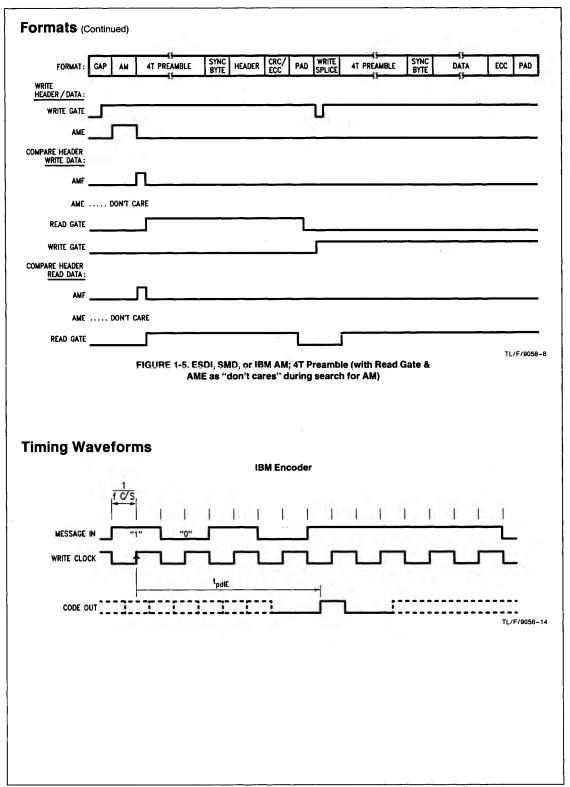

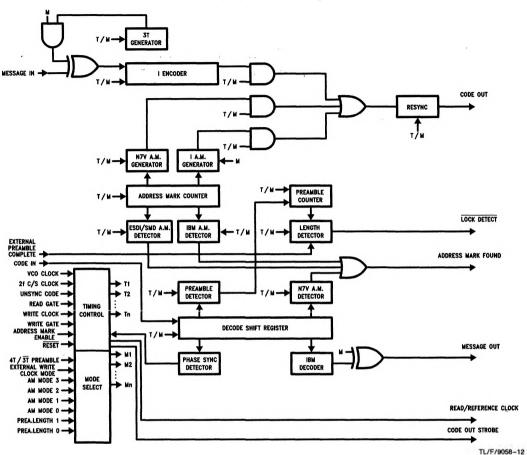

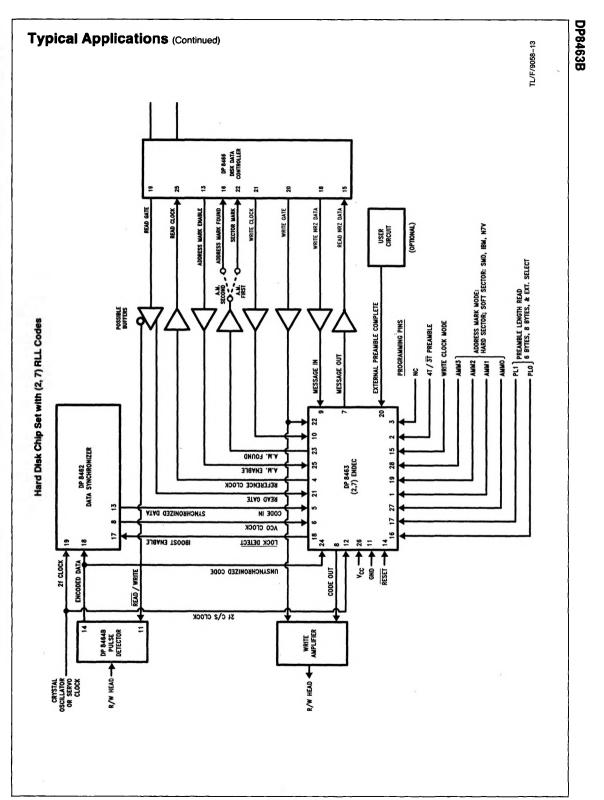

The DP8463B (2,7) ENDEC performs the encoding and decoding for a disk memory system using a (2,7) Run-Length-Limited (RLL) code. This code gives a disk system the ability to record up to 50% more message data in the same media space without any increase in the Flux Changes per Inch (FCI) density, when compared to a system using Modified Frequency Modulation (MFM) coding. The DP8463B also performs other functions of writing or reading format segments that can not be done by a disk data controller. These additional functions include the writing and reading of Preambles (PLL synchronization fields) and various soft-sector format Address Marks that are compatible with (2,7) RLL code. The user may also select different lengths of preamble to count before the DP8463B issues a Lock Detect signal. The encoded CODE OUT output is automatically resynchronized to the 2f CRYSTAL/SERVO CLOCK for perfect periodic writing regardless of the duty cycle of the WRITE CLOCK input and regardless of the phase relationship between the WRITE CLOCK and the 2f CRYSTAL/SERVO CLOCK. The READ/REFERENCE CLOCK output is switched between clock sources without generating any short pulses. In addition to the detecting of standard ESDI and SMD Address Marks, there is an optional noise tolerant mode that allows the recognizing of an address mark gap even with a bit or two of noise.

The DP8463B is compatible with the Storage Module Drive (SMD) and Enhanced Small Device Interface (ESDI) functional specifications, and has a format mode similar to the one used in ST-506 devices. The Input/Output (I/O) of the DP8463B are active-high, except LOCK DETECT, so inverting line drivers should be used for interfacing with the active-low I/O of ESDI. The term "Message" is used to designate unencoded data, also referred to as NRZ Data in disk literature. The term "Code" designates the encoded data.

#### Features

Up to 50% increase in message data density over MFM DP8463E

- Encodes and decodes using IBM (2,7) Message/Code Table

- Programmable Formats

- Hard Sector

- Soft Sector with Address Mark preceding Preamble

- Soft Sector with Address Mark following Preamble

- Programmable Address Marks

- ESDI 3-Byte transitionless gap, preceding Preamble

- ESDI 3-Byte transitionless gap, noise tolerant

- SMD 3-Byte transitionless gap, preceding Preamble

- SMD 3-Byte transitionless gap, noise tolerant

- IBM 2-Byte gap with three transitions, preceding Preamble

- N7V 2-Byte Address Mark with code word not in message/code table that does not violate (2,7) code constraints, following Preamble (Above gap lengths are in message-bytes)

- Programmable Preamble length counted before LOCK DETECT issued

- Externally determined (e.g., from DP8462 Data Synchronizer)

- 6 Message Bytes

- 8 Message Bytes

- Code output is resynchronized to 2f CRYSTAL/SERVO CLOCK

- Glitchless Multiplexer is used to switch between READ/ REFERENCE CLOCK sources

- Strobe available to clock CODE OUT output into external register

- ADDRESS MARK FOUND appears after first "1" bit following Address Mark

- Message Data Rate to 20 Megabits/second (Code rate = 40 Mb/s)

- Compatible with ESDI

- Compatible with SMD

- Compatible with DP8462 Data Synchronizer

- Compatible with DP8466 Disk Data Controller

- 2-micron dual metal CMOS

- Single +5V Supply

- Packages

- 28-pin Dual-In-Line Package

- --- 28-pin Plastic Chip Carrier

### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage          | -0.5V to +7.0V                   |

|-------------------------|----------------------------------|

| Input or Output Voltage | -0.5V to V <sub>CC</sub> $+0.5V$ |

| Storage Temperature     | -65°C to +150°C                  |

| Lead Temperature        | 260°C                            |

# Recommended Operating Conditions

Temperature Range  $(T_A)$ ESD rating is to be determined. +0.0°C to +70°C

# **DC Electrical Characteristics**

$V_{CC} = +5V \pm 10\%$ ; Min./Max. limits apply across temperature range T<sub>A</sub> unless otherwise specified.

| Symbol             | Parameter                    | Conditions                                                                      | Min                   | Max  | Units |

|--------------------|------------------------------|---------------------------------------------------------------------------------|-----------------------|------|-------|

| VIH                | High Level<br>Input Voltage  |                                                                                 | 2.25                  |      | v     |

| VIL                | Low Level<br>Input Voltage   |                                                                                 |                       | 0.65 | v     |

| V <sub>OH1</sub>   | High Level<br>Output Voltage | $V_I = V_{CC} \text{ or GND}$<br>$I_O = 20 \mu\text{A}$                         | V <sub>CC</sub> - 0.1 |      | v     |

| V <sub>OH2</sub>   | High Level<br>Output Voltage | $V_{I} = V_{CC} \text{ or GND}$<br>$I_{OH} = -4.0 \text{ mA}$                   | 3.5                   |      | v     |

| V <sub>OL1</sub>   | Low Level<br>Output Voltage  | $V_I = V_{CC} \text{ or GND}$<br>$I_O = 20 \ \mu A$                             |                       | 0.1  | v     |

| V <sub>OL2</sub>   | Low Level<br>Output Voltage  | $V_{I} = V_{CC} \text{ or GND}$<br>$I_{OL} = +4 \text{ mA}$                     |                       | 0.4  | v     |

| ιн                 | High Level<br>Input Current  | $V_{I} = V_{CC}$                                                                |                       | + 10 | μΑ    |

| I <sub>CC</sub> DY | Supply Current,<br>Dynamic   | $V_I = V_{CC} \text{ or GND}$<br>$T_A = 25^{\circ}C, f_{VCO} = 40 \text{ Mb/s}$ |                       | 60   | mA    |

| I <sub>CC</sub> SB | Supply Current,<br>Standby   | $V_{I} = V_{CC} \text{ or GND}$<br>$T_{A} = 25^{\circ}C, f_{VCO} = 1Mb/s$       |                       | 10   | mA    |

| Ð                    |

|----------------------|

| œ                    |

| 4                    |

| S.                   |

| $\underline{\omega}$ |

|                      |

| Symbol             | Parameter                                                                      | Part No.          | Min | Тур | Max  | Units                   |

|--------------------|--------------------------------------------------------------------------------|-------------------|-----|-----|------|-------------------------|

| fDATA              | Maximum Message Data Frequency<br>(NRZ Data)                                   | DP8463B-12        | 12  |     |      | Mb/s                    |

| fvco<br>fc/s       | Maximum VCO Frequency<br>Maximum CRYSTAL/SERVO CLOCK<br>frequency              | DP8463B-12        | 24  |     |      | Mb/s                    |

| t <sub>MISU</sub>  | Set-Up Time of MESSAGE IN Before<br>WRITE CLOCK Positive Edge                  |                   | 10  |     |      | ns                      |

| <sup>t</sup> мiн   | Hold Time of MESSAGE IN After WRITE<br>CLOCK Positive Edge                     |                   | 10  |     |      | ns                      |

| <sup>t</sup> MOSU  | Set-Up Time of MESSAGE OUT Before<br>READ/REFERENCE CLOCK Positive Edge        |                   | 24  |     |      | ns                      |

| <sup>t</sup> мон   | Hold Time of MESSAGE OUT After READ/<br>REFERENCE CLOCK Positive Edge          |                   | 14  |     |      | ns                      |

| <sup>t</sup> CISU  | Set-Up Time of CODE IN Before VCO<br>CLOCK Positive Edge                       | 61-2 <sup>-</sup> | 7   |     |      | ns                      |

| <sup>t</sup> CIH   | Hold Time of CODE IN After VCO CLOCK Positive Edge                             |                   | 10  |     |      | ns                      |

| tcosu              | Set-Up Time of CODE OUT Before CODE<br>OUT STROBE Positive Edge                |                   | 10  |     |      | ns                      |

| tсон               | Hold Time of CODE OUT After CODE OUT<br>STROBE Positive Edge                   |                   | 5   |     |      | ns                      |

| t <sub>PWUC</sub>  | Pulse Width of UNSYNCHRONIZED CODE                                             |                   | 10  |     |      | ns                      |

| tpwpc              | Pulse Width of EXTERNAL PREAMBLE<br>COMPLETE                                   |                   | 4   |     |      | VCO<br>Clock<br>Periods |

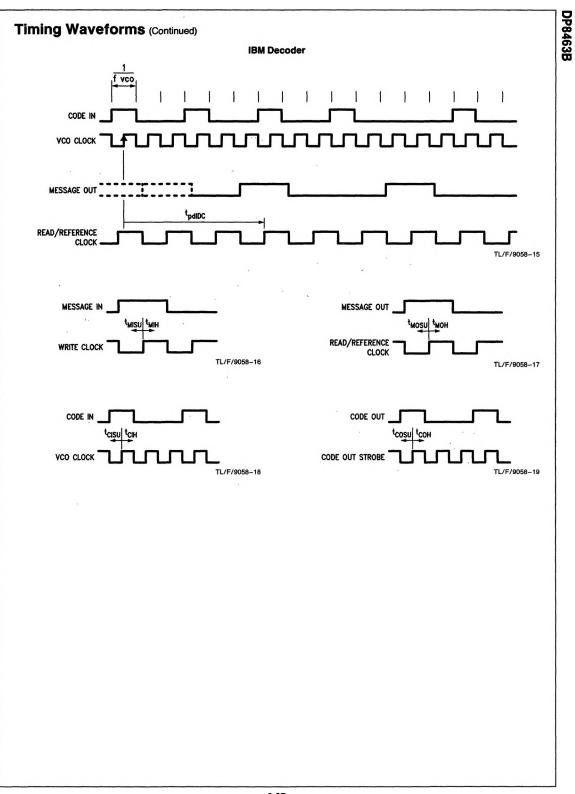

| <sup>t</sup> pdIE  | Propagation Delay of IBM Encoder from<br>WRITE CLOCK Positive Edge to CODE OUT |                   | 7   |     | 7    | Code<br>Bits            |

|                    |                                                                                |                   | +5  |     | + 45 | ns                      |

| t <sub>pdIDC</sub> | Propagation Delay of IBM Decoder from<br>VCO CLOCK Postive Edge to             | -                 | 5.5 |     | 5.5  | Code<br>Bits            |

|                    | READ/REFERENCE CLOCK Positive Edge                                             |                   | +5  |     | + 62 | ns                      |

| WCL                | WRITE CLOCK Low                                                                |                   | 20% | -   | 80%  | WRITE                   |

| wсн                | WRITE CLOCK High                                                               |                   | 20% |     | 80%  | CLOCH<br>Period         |

\_\_\_\_\_

Note 1. Mb/s = Megabits/second

15 M 10

- -

I

Code bit = period of 2f or VCO Clock

1.1

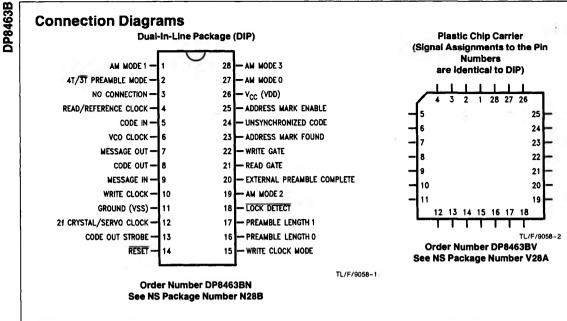

# Pin Descriptions

| Pin No  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11      | GROUND (V <sub>SS</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 26      | V <sub>CC</sub> (V <sub>DD</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| INPUT S | GINALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5       | <b>CODE IN.</b> This is the encoded data output of the data synchronizer (e.g., DP8462). Each flux transition on the disk is a high level signal here with a width of one VCO clock period. The CODE IN is read by the DP8463B at the time of the positive going edge of the VCO CLOCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6       | VCO CLOCK. This is the VCO clock output of the data synchronizer (e.g., DP8462). During the read mode, the VCO CLOCK is phase locked to the flux transitions on the disk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9       | MESSAGE IN. This is the unencoded "write data"<br>from the disk data controller (e.g., DP8466).<br>MESSAGE IN is read into the DP8463B by the<br>positive going edge of the WRITE CLOCK input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10      | WRITE CLOCK. This clock strobes the<br>MESSAGE IN "write data" into the encoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12      | 2f CRYSTAL/SERVO CLOCK (2f C/S CLOCK).<br>This is the clock output of a disk drive's dedicated<br>servo track or the buffered output of a crystal<br>oscillator. This signal is the reference clock for<br>generating the CODE OUT signal when the<br>WRITE CLOCK MODE pin is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14      | <b>RESET.</b> An active low input resets various flip-<br>flops when the next 2f C/S CLOCK positive edge<br>occurs, so RESET should have a pulse width of<br>two 2f C/S CLOCK periods. The DP8463B should<br>be reset after each time power is applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20      | EXTERNAL PREAMBLE COMPLETE. With PL1<br>and PL0 both low, an "active" level on this pin<br>signals the DP8463B that the reading of the<br>preamble, for phase locking purposes, is<br>complete. The DP8463B then switches into its<br>normal decoding mode and issues an active low<br>LOCK DETECT signal. This mode could be used<br>for short preamble lengths in conjunction with the<br>DP8462. The DP8462 Lock Detect output would<br>be connected to the EXTERNAL PREAMBLE<br>COMPLETE (observing polarities, see pin 28).<br>The DP8462 will issue a "Lock Detect" after<br>counting 16 code ones (3 to 4 Message Bytes<br>depending upon which preamble pattern is used,<br>3T or 4T). The DP8463B must receive at least two<br>4T preamble patterns before an EXTERNAL<br>PREAMBLE COMPLETE signal is received. The<br>"active" level of this pin is determined by the<br>state of pin 28, ADDRESS MODE 3. |

| Pin No | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21     | <b>READ GATE.</b> An active high level input places<br>the DP8463B in the read mode. During this mode:<br>the source of the READ/REFERENCE CLOCK is<br>switched to the VCO CLOCK/2, the address mark<br>is searched for (if selected), the length of the<br>preamble is counted as programmed, and the<br>CODE IN signal is decoded and output as<br>MESSAGE OUT at the appropriate time per the<br>programming of the mode pins.                                                                                                                                                                                                                                                                                                                                                                                         |

| 22     | WRITE GATE. An active high level input places<br>the DP8463B in the write mode. During this mode<br>the MESSAGE IN data is encoded and output as<br>CODE OUT, and during the programmed time<br>(when selected), the preamble and address<br>marks appear at CODE OUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24     | <b>UNSYNCHRONIZED CODE.</b> This is the encoded data output of the pulse detector (e.g., DP8464B). A flux transition on the disk produces an active high pulse for this pin. This input is used to detect the ESDI, SMD, and IBM address marks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 25     | ADDRESS MARK ENABLE (AME). An active<br>high level, while WRITE GATE is also active high,<br>will write the address mark prescribed by the AM<br>MODE pins. The AME must be high for the<br>complete address mark. An active high level of<br>AME while WRITE GATE and READ GATE are<br>both iow causes the 8463B to search for an<br>Address Mark when in the ESDI Mode (AM2 &<br>AM1 low). An active high level of AME when<br>READ GATE is active high causes the 8463B to<br>search for an AM when in the SMD Mode (AM2<br>low, AM1 high).                                                                                                                                                                                                                                                                            |

| PROGR  | AMMING INPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1      | ADDRESS MARK MODE 1 (AM MODE 1).<br>Defined in Table I. A logic "1" is a high level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2      | 4T/3T PREAMBLE MODE. A high level places<br>the DP8463B in the mode to generate and detect<br>"4T" preamble patterns (i.e., 1000 in code which<br>is four time periods). In this mode, the MESSAGE<br>IN input is inverted in the DP8463B before being<br>encoded so that a 4T preamble can be generated<br>from an all zeros MESSAGE IN data stream. The<br>output of the decoder is also inverted in this mode<br>so the double inversion is transparent to the user.<br>The double inversion is always done in this mode,<br>not just during the preamble.<br>A low level input on this pin places the DP8463B<br>in the mode to accept the "3T" pattern as the<br>preamble (3T pattern is 100 in code). The Input/<br>Output is not inverted in this mode. If the 3T<br>preamble pattern is used with the IBM code, a |

# Pin Descriptions (Continued)

į,

| Pin No       |                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PROGR        | AMM                                                                                               | ING II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NPUTS (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 2<br>(Cont.) | gene<br>durin<br>MES<br>and to<br>output<br>zeros<br>of W<br>conti<br>MES<br>gene<br>activ<br>PRE | arate.<br>Ing whi<br>SAGE<br>SAGE<br>Inte DI<br>Inte DI<br>I | impossible for a disk data controller to<br>Therefore there is a special mode<br>ch the disk data controller's input to<br>E IN is ignored by the encoder section<br>78463B internally generates a 3T code<br>long as the MESSAGE IN input is all<br>a 3T preamble starts after the initiation<br>GATE going active (high) and<br>until the first "1" is seen at the<br>E IN pin. This mode of internally<br>a 3T preamble with IBM code is<br>by having high levels on the two<br>.E LENGTH 0 and PREAMBLE<br>I pins (16 & 17). |  |  |  |  |  |

| 3            | NOC                                                                                               | CONN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>ECTION.</b> This pin must be left open-<br>r tied to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 15           | WRI<br>autor<br>enco<br>the 2<br>enco<br>flop t<br>level<br>WRI<br>In thi<br>from                 | TE CL<br>matic<br>oder. 1<br>oder. 1<br>that po<br>that po<br>WRI1<br>TE CL<br>is moo<br>the e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>OCK MODE.</b> A low level enables the<br>resynchronization circuitry for the IBM<br>'he WRITE CLOCK is resynchronized to<br>CLOCK and used for clocking the IBM<br>'he same 2f C/S is used to clock a flip-<br>rovides the CODE OUT signal. A high<br>ITE CLOCK MODE input allows the<br>OCK to directly clock the IBM encoder.<br>Je the CODE OUT signal comes directly<br>neoder and does not get strobed out by<br>CLOCK.                                                                                                  |  |  |  |  |  |

| 16           | PRE<br>lengt<br>low L<br>pins<br>prea                                                             | AMBL<br>th of p<br>-OCK<br>also c<br>mble (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>LE LENGTH 0 (PL0).</b> This input and<br>E LENGTH 1 (PL1) determine the<br>reamble that is read before an active<br>DETECT signal is issued. These two<br>control the internal generation of a 3T<br>pattern for use with an all zeros<br>I N input.                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 1            | PL1                                                                                               | PL1 PL0 LENGTH OF PREAMBLE/<br>OTHER FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|              | 0                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Length Set by External<br>Preamble Complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|              | 0                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6 Message Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| i            | 1<br>1                                                                                            | 0<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8 Message Bytes'<br>6 Message Bytes/Generate<br>3T Preamble Internally                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 17           | PREAMBLE LENGTH 1 (PL1). See pin 16.                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 19           | ADD                                                                                               | RESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MODE 2. Defined in Table I.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 27           | ADD                                                                                               | RESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MODE 0. Defined in Table I.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 28           | of thi<br>of the<br>COM<br>Table<br>type<br>MOD<br>activ                                          | is pin<br>e pin 2<br>IPLET<br>e 1 fui<br>of the<br>)E 3 is<br>e high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MODE 3. Defined in Table I. The level<br>also determines the active level polarity<br>20 EXTERNAL PREAMBLE<br>"E input. This is possible since the<br>action is a Don't Care for all except one<br>N7V Address Mark. If ADDRESS<br>high or open-circuited, then pin 20 is<br>h If ADDRESS MODE 3 is low, then pin<br>e low.                                                                                                                                                                                                      |  |  |  |  |  |

| Pin No | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTPU  | TSIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4      | READ/REFERENCE CLOCK. This is the clock<br>that is provided to the disk data controller where it<br>is typically labelled "read clock". It is, however,<br>necessary for both reading and writing. The<br>source of the clock is different during reading<br>compared to writing. When READ GATE is active<br>(high) the READ/REFERENCE CLOCK is the<br>VCO CLOCK divided-by-two. The MESSAGE<br>OUT data is read by the disk data controller using<br>the positive going edge of READ/REFERENCE<br>CLOCK. When READ GATE is inactive (low), the<br>READ/REFERENCE clock is the 2f C/S CLOCK<br>divided-by-two. This clock is used by the disk data<br>controller as the timing source for its WRITE<br>DATA and WRITE CLOCK outputs. |

| 7      | MESSAGE OUT. This is the "Read Data" input to<br>the disk data controller. A high level represents a<br>"one" of decoded (NRZ) data. It is read by the<br>controller using the positive going edge of the<br>READ/REFERENCE CLOCK. MESSAGE OUT is<br>held at a low level when READ GATE is inactive<br>(low) and other intervals specified in Table I.                                                                                                                                                                                                                                                                                                                                                                                |

| 8      | <b>CODE OUT.</b> A high level for a 2f clock period is<br>output for each "1" in code that is to be written on<br>the disk as a flux transition by a write amplifier<br>containing a write flip-flop that changes state<br>every time a positive going pulse edge is<br>received. Since (2,7) code always has at least two<br>zeros between adjacent ones, this output is a<br>Return-to-Zero (RZ) code. If the CODE OUT is to<br>be sent to another register, instead of directly to<br>the Write Amplifier, it can be clocked out by using<br>the CODE OUT STROBE.                                                                                                                                                                  |

| 13     | <b>CODE OUT STROBE.</b> The positive going edge of<br>this signal should be used as the clock input to an<br>external shift register for applications where the<br>CODE OUT is transformed before being sent to<br>the Write Amplifier, e.g., for precompensation of<br>some code patterns on some tracks.                                                                                                                                                                                                                                                                                                                                                                                                                            |