# DS1004 5-Tap High Speed Silicon Delay Line

#### www.dalsemi.com

## **FEATURES**

- All-silicon timing circuit

- Five delayed clock phases per input

- Precise tap-to-tap nominal delay tolerances of ±0.75 and ±1 ns

- Input-to-tap 1 delay of 5 ns

- Nominal Delay tolerances of  $\pm 1.5$  ns

- Leading and trailing edge precision preserves the input symmetry

- CMOS design with TTL compatibility

- Standard 8-pin DIP and 150 mil 8-pin SOIC

- Vapor phase, IR and wave solderable

- Available in Tape and Reel

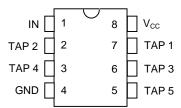

## **PIN ASSIGNMENT**

DS1004M 8-Pin DIP (300-mil) See Mech. Drawings Section

DS1004Z 8-Pin SOIC (150-mil) See Mech. Drawings Section

## PIN DESCRIPTION

TAP 1-5 - TAP Output Number

$V_{CC}$  - +5V Supply GND - Ground IN - Input

#### DESCRIPTION

The DS1004 is a 5-tap all silicon delay line which can provide 2, 3, 4, or 5 ns tap-to-tap delays within a standard part family. The device is Dallas Semiconductor's fastest 5-tap delay line. It is available in a standard 8-pin DIP and 150 mil 8-pin mini-SOIC. The device features precise leading and trailing edge accuracies and has the inherent reliability of an all-silicon delay line solution.

The DS1004 is specified for tap-to-tap tolerances as shown in Table 1. Each device has a minimum input-to-tap 1 delay of 5 ns. Subsequent taps (taps 2 through 5) are precisely delayed by 2, 3, 4, or 5 ns. See Table 1 for details. Input to Tap Tolerance over temperature and voltage is  $\pm 1.5$  ns in addition to the nominal delay tolerance. Nominal tap-to-tap tolerances range from  $\pm 0.75$  ns to  $\pm 1.0$  ns. Each output is capable of driving up to 10 LS loads.

For customers needing non-standard delay values, the Late Package Program (LPP) is available. Customers may contact Dallas Semiconductor at (972) 371–4348 for further details.

1 of 6 092500

## PART NUMBER TOLERANCE TABLE Table 1

| PART      | INPUT-TO-TA          | AP TOLERANCE                     | TAP-TO-TAP TOLERANCE |                                  |  |

|-----------|----------------------|----------------------------------|----------------------|----------------------------------|--|

| NUMBER    | NOMINAL <sup>1</sup> | OVER TEMP & VOLTAGE <sup>2</sup> | NOMINAL <sup>1</sup> | OVER TEMP & VOLTAGE <sup>2</sup> |  |

| DS1004M-2 | 1.5 ns               | ±3.0 ns                          | ±0.75 ns             | ±1.5 ns                          |  |

| DS1004M-3 | 1.5 ns               | ±3.0 ns                          | ±0.75 ns             | ±1.5 ns                          |  |

| DS1004M-4 | 1.5 ns               | ±3.0 ns                          | ±1.0 ns              | ±1.75 ns                         |  |

| DS1004M-5 | 1.5 ns               | ±3.0 ns                          | ±1.0 ns              | ±1.75 ns                         |  |

| DS1004Z-2 | 1.5 ns               | ±3.0 ns                          | ±0.75 ns             | ±1.5 ns                          |  |

| DS1004Z-3 | 1.5 ns               | ±3.0 ns                          | ±0.75 ns             | ±1.5 ns                          |  |

| DS1004Z-4 | 1.5 ns               | ±3.0 ns                          | ±1.0 ns              | ±1.75 ns                         |  |

| DS1004Z-5 | 1.5 ns               | ±3.0 ns                          | ±1.0 ns              | ±1.75 ns                         |  |

## **NOTES:**

- 1. Nominal conditions are  $+25^{\circ}$ C and  $V_{CC} = +5.0V$

- 2. Temperature and voltage variations cover the range from  $V_{CC}$ =5.0V  $\pm$  5% and temperature range from 0°C to +70°C.

- 3. Delay accuracy for both leading and trailing edges.

## PART NUMBER DELAY TABLE Table 2

| PART      | NOMINAL VALUES (FOR REFERENCE ONLY) |           |           |           |           |  |  |  |

|-----------|-------------------------------------|-----------|-----------|-----------|-----------|--|--|--|

| NUMBER    | INPUT-TO-                           | INPUT-TO- | INPUT-TO- | INPUT-TO- | INPUT-TO- |  |  |  |

|           | TAP1                                | TAP2      | TAP3      | TAP4      | TAP5      |  |  |  |

| DS1004M-2 | 5 ns                                | 7 ns      | 9 ns      | 11 ns     | 13 ns     |  |  |  |

| DS1004M-3 | 5 ns                                | 8 ns      | 11 ns     | 14 ns     | 17 ns     |  |  |  |

| DS1004M-4 | 5 ns                                | 9 ns      | 13 ns     | 17 ns     | 21 ns     |  |  |  |

| DS1004M-5 | 5 ns                                | 10 ns     | 15 ns     | 20 ns     | 25 ns     |  |  |  |

| DS1004Z-2 | 5 ns                                | 7 ns      | 9 ns      | 11 ns     | 13 ns     |  |  |  |

| DS1004Z-3 | 5 ns                                | 8 ns      | 11 ns     | 14 ns     | 17 ns     |  |  |  |

| DS1004Z-4 | 5 ns                                | 9 ns      | 13 ns     | 17 ns     | 21 ns     |  |  |  |

| DS1004Z-5 | 5 ns                                | 10 ns     | 15 ns     | 20 ns     | 25 ns     |  |  |  |

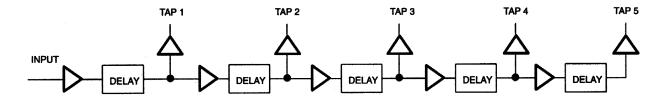

## **LOGIC DIAGRAM**

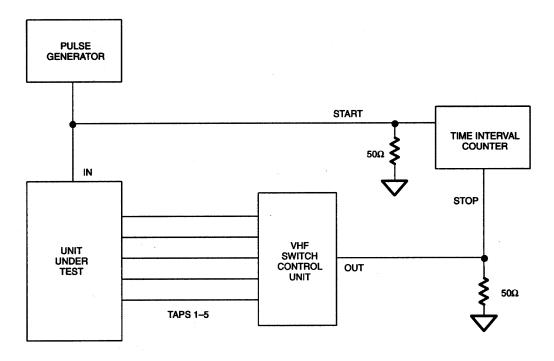

## **DS1004 TEST CIRCUIT** Figure 1

## **TEST SETUP DESCRIPTION**

Figure 1 illustrates the hardware configuration used for measuring the timing parameters of the DS1004. The input waveform is produced by a precision pulse generator under software control. Time delays are measured by a time interval counter (20 ps resolution) connected to the output. The DS1004 output taps are selected and connected to the interval counter by a VHF switch control unit. All measurements are fully automated with each instrument controlled by the computer over an IEEE 488 bus.

## **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground -1.0V to +7.0V Operating Temperature  $0^{\circ}C$  to  $70^{\circ}C$  Storage Temperature  $-55^{\circ}C$  to  $+125^{\circ}C$

Soldering Temperature See J-STD-020A Specification

Short Circuit Output Current 50 mA for 1 second

## DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}\text{C to }70^{\circ}\text{C}; V_{CC} = 5.0\text{V} \pm 5\%)$

| = 0 === 0 :: :: 0 :: = 0 ::: :: : : : : |          |                           |      |      | $(3 \ 3 \ 13 \ 3 \ 3)$ |       |       |  |  |

|-----------------------------------------|----------|---------------------------|------|------|------------------------|-------|-------|--|--|

| PARAMETER                               | SYM      | TEST                      | MIN  | TYP  | MAX                    | UNITS | NOTES |  |  |

|                                         |          | CONDITION                 |      |      |                        |       |       |  |  |

| Supply Voltage                          | $V_{CC}$ |                           | 4.75 | 5.00 | 5.25                   | V     | 1     |  |  |

| Active Current                          | $I_{CC}$ | V <sub>CC</sub> =5.25V    |      | 35   | 75                     | mA    |       |  |  |

|                                         |          | Period=1 μs               |      |      |                        |       |       |  |  |

| High Level Input                        | $V_{IH}$ |                           | 2.2  |      | $V_{CC} + 0.5$         | V     | 1     |  |  |

| Voltage                                 |          |                           |      |      |                        |       |       |  |  |

| Low Level Input                         | $V_{IL}$ |                           | -0.5 |      | 0.8                    | V     | 1     |  |  |

| Voltage                                 |          |                           |      |      |                        |       |       |  |  |

| Input Leakage                           | $I_{I}$  | $0.0V \le V_I \le V_{CC}$ | -1.0 |      | 1.0                    | μA    |       |  |  |

| High Level Output                       | $I_{OH}$ | V <sub>CC</sub> =4.75V    |      |      | -1.0                   | mA    |       |  |  |

| Current                                 |          | $V_{OH}=4V$               |      |      |                        |       |       |  |  |

| Low Level Output                        | $I_{OL}$ | V <sub>CC</sub> =4.75V    | 12   |      |                        | mA    |       |  |  |

| Current                                 |          | $V_{OL}=0.5V$             |      |      |                        |       |       |  |  |

## **AC ELECTRICAL CHARACTERISTICS**

$(T_A = 25^{\circ}C; V_{CC} = 5V \pm 5\%)$

| PARAMETER         | SYMBOL            | MIN                           | TYP     | MAX | UNITS | NOTES |

|-------------------|-------------------|-------------------------------|---------|-----|-------|-------|

| Period            | $t_{PERIOD}$      | 4 (t <sub>WI</sub> )          |         |     | ns    | 3     |

| Input Pulse Width | $t_{ m WI}$       | 40% of Tap 5 t <sub>PLH</sub> |         |     | ns    | 3     |

| Input to Tap 1    | $t_{\rm PLH},$    |                               | Table 1 |     | ns    | 2     |

| Output Delay      | $t_{ m PHL}$      |                               |         |     |       |       |

| Tap-to-Tap Delays | $t_{PLH}$         |                               | Table 1 |     | ns    | 2     |

| Output Rise or    | t <sub>OR</sub> , |                               | 2.0     | 2.5 | ns    |       |

| Fall Time         | $t_{OF}$          |                               |         |     |       |       |

| Power-up Time     | $t_{\mathrm{PU}}$ |                               |         | 100 | ms    |       |

## **CAPACITANCE**

$(T_A = 25^{\circ}C)$

| PARAMETER         | SYMBOL   | MIN | TYP | MAX | UNITS | NOTES |

|-------------------|----------|-----|-----|-----|-------|-------|

| Input Capacitance | $C_{IN}$ |     |     | 10  | pF    |       |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### **NOTES:**

- 1. All voltages are referenced to ground.

- 2. V<sub>CC</sub>=5V and 25°C. Delay accuracy on both the rising and falling edges within tolerances given in Table 1.

- 3. Pulse width and duty cycle specifications may be exceeded, however, accuracy will be application sensitive with respect to decoupling, layout, etc.

#### **TEST CONDITIONS**

## **INPUT:**

Ambient Temperature:  $25^{\circ}\text{C} \pm 3^{\circ}\text{C}$ Supply Voltage (V<sub>CC</sub>):  $5.0\text{V} \pm 0.1\text{V}$

Input Pulse: High =  $3.0V \pm 0.1V$

$Low = 0.0V \pm 0.1V$

Source Impedance: 50 ohm max.

Rise and Fall Time: 3.0 ns max. (measured between 0.6V and 2.4V)

Pulse Width: 500 ns Pulse Period: 1 µs

Output Load

Capacitance: 15 pF

## **OUTPUT:**

Each output is loaded with the equivalent of one 74F04 input gate. Data is measured at the 1.5V level on the rising and falling edge.

#### NOTE:

Above conditions are for test only and do not restrict the devices under other data sheet conditions.

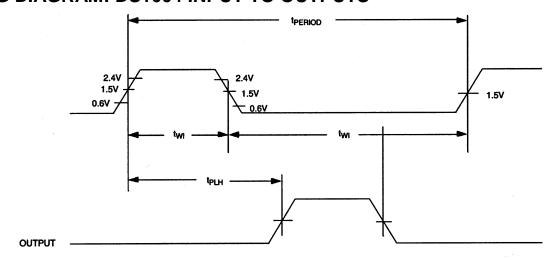

## TIMING DIAGRAM: DS1004 INPUT TO OUTPUTS

## **TERMINOLOGY**

**Period:** The time elapsed between the leading edge of the first pulse and the leading edge of the following pulse.

$t_{WI}$  (Pulse Width): The elapsed time on the pulse between the 1.5V point on the leading edge and the 1.5V point on the trailing edge or the 1.5V point on the trailing edge and the 1.5V point on the leading edge.

**t**<sub>RISE</sub> (**Input Rise Time**): The elapsed time between the 20% and the 80% point on the leading edge of the input pulse.

$t_{FALL}$  (Input Fall Time): The elapsed time between the 80% and the 20% point on the trailing edge of the input pulse.

$\mathbf{t}_{PLH}$  (**Time Delay, Rising**): The elapsed time between the 1.5V point on the leading edge of the input pulse and the 1.5V point on the leading edge of the output pulse.

**t**<sub>PHL</sub> (**Time Delay, Falling**): The elapsed time between the 1.5V point on the falling edge of the input pulse and the 1.5V point on the falling edge of the output pulse.