# PRELIMINARY

**National** Semiconductor

# DS36C200 Dual High Speed Bi-Directional Differential Transceiver

# **General Description**

The DS36C200 is a dual transceiver device optimized for high data rate and low power applications. This device provides a single chip solution for a dual high speed bi-directional interface. Also, both control pins may be routed together for single bit control of datastreams. Both control pins are adjacent to each other for ease of routing them together. The DS36C200 is compatible with IEEE 1394 physical layer and may be used as an economical solution with some considerations. Please reference the application information on 1394 for more information. The device is in a 14-lead small outline package. The differential driver outputs provides low EMI with its low output swings typically 210 mV. The receiver offers  $\pm$  100 mV threshold sensitivity, in addition to common mode noise protection.

## Features

- Optimized for DSS to DVHS interface link

- IEEE 1394 signaling

- Operates above 100 Mbps

- Bi-directional transceivers

- 14-lead SOIC package

- Ultra low power dissipation

- ± 100 mV receiver sensitivity

- Low differential output swing typical 210 mV

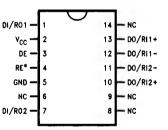

## **Connection Diagram**

TL/F/12621-1

Order Number DS36C200M See NS Package Number M14A

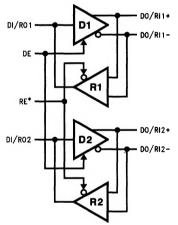

# **Functional Diagram**

TL/F/12621-2

Absolute Maximum Ratings (Note 1) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> ) | -0.3V to +6V                      |

|-----------------------------------|-----------------------------------|

| Enable Input Voltage (DE, RE*)    | -0.3V to (V <sub>CC</sub> + 0.3V) |

| Voltage (DI/RO)                   | -0.3V to (V <sub>CC</sub> + 0.3V) |

| Voltage (DO/RI±)                  | -0.3V to (V <sub>CC</sub> + 0.3V) |

| Maximum Package Power Dissi       | pation @+25°C                     |

| M Package                         | TBD mW                            |

| Derate M Package                  | TBD mW/°C above +25°C             |

| Storage Temperature Range         | -65°C to +150°C                   |

|                                   |                                   |

Lead Temperature Range (Soldering, 4 sec.) + 260°C ESD Rating (HBM 1.5 kΩ, 100 pF) (Note 4) ≥2.5 kV

# **Recommended Operating** Conditions

|                                   | Min   | Тур   | Max   | Units |

|-----------------------------------|-------|-------|-------|-------|

| Supply Voltage (V <sub>CC</sub> ) | + 4.5 | + 5.0 | + 5.5 | v     |

| Receiver Input Voltage            | 0     |       | 2.4   | v     |

| Operating Free Air                |       |       | Xy I  |       |

| Temperature (T <sub>A</sub> )     | 0     | 25    | 70    | °C    |

|                                   |       |       |       |       |

# **Electrical Characteristics**

Over supply voltage and operating temperature ranges, unless otherwise specified (Notes 2, 3 and 7)

| Symbol           | Parameter Conditions             |                                                     | Pin         | Min   | Тур  | Max   | Units |

|------------------|----------------------------------|-----------------------------------------------------|-------------|-------|------|-------|-------|

| DIFFERENT        | IAL DRIVER CHARACTERISTI         | CS                                                  |             | +     |      |       |       |

| V <sub>OD</sub>  | Output Differential Voltage      | $R_L = 55\Omega$                                    |             | 172   | 210  | TBD   | m۷    |

| ΔV <sub>OD</sub> | V <sub>OD</sub> Magnitude Change | Figure 1                                            |             | 0     | 4    | 35    | m∨    |

| VOH              | Output High Voltage              |                                                     |             |       | 1.36 | 1.6   | V     |

| VoL              | Output Low Voltage               | ÷                                                   |             | 0.9   | 1.15 |       | V     |

| VOS              | Offset Voltage                   |                                                     | DO+,<br>DO- | 0.9   | 1.25 | 1.6   | V     |

| ΔV <sub>OS</sub> | Offset Magnitude Change          |                                                     |             | 0     | 5    | 25    | mV    |

| lozd             | TRI-STATE® Leakage               | $V_0 = V_{CC}$ or GND                               |             | 0     | ±1   | ±10   | μA    |

| IOXD             | Power-Off Leakage                | $V_0 = V_{CC} = GND = 0V$                           |             | 0     | ±1   | ±10   | μΑ    |

| IOSD             | Output Short Circuit Current     |                                                     |             |       | -6   | -9    | mA    |

| IFFERENT         | IAL RECEIVER CHARACTERIS         | TICS                                                |             |       |      |       |       |

| V <sub>TH</sub>  | Input Threshold High             |                                                     |             |       |      | +100  | mV    |

| V <sub>TL</sub>  | Input Threshold Low              |                                                     | RI+,<br>RI- | - 100 |      |       | mV    |

| I <sub>IN</sub>  | Input Current                    | $V_{IN} = +2.4V$ , or 0V                            |             | - 10  | ±1   | + 10  | μA    |

| V <sub>OH</sub>  | Output High Voltage              | I <sub>OH</sub> = −400 μA                           |             | 3.8   | 4.9  |       | v     |

|                  | - ÷                              | Inputs Open                                         |             | 3.8   | 4.9  |       | V     |

|                  |                                  | Inputs Terminated, $R_t = 55\Omega$                 | RO          | 3.8   | 4.9  |       | v     |

|                  |                                  | Inputs Shorted, V <sub>OD</sub> = 0V                |             |       | 4.9  |       | v     |

| VOL              | Output Low Voltage               | $I_{OL} = 2.0 \text{ mA}, V_{ID} = -200 \text{ mV}$ |             |       | 0.3  | 0.5   | V     |

| IOSR             | Output Short Circuit Current     | V <sub>OUT</sub> = 0V                               |             | -15   | -60  | - 100 | mA    |

| Symbol          | Parameter            | Conditions                           | Pin             | Min   | Тур  | Max | Unita |

|-----------------|----------------------|--------------------------------------|-----------------|-------|------|-----|-------|

| DEVICE CHA      | RACTERISTICS         |                                      |                 | -     |      |     |       |

| VIH             | Input High Voltage   |                                      |                 | 2.0   |      | Vcc | v     |

| VIL             | Input Low Voltage    |                                      |                 | GND   |      | 0.8 | V     |

| IJн             | Input High Current   | $V_{IN} = V_{CC} \text{ or } 2.4 V$  | DI, DE<br>RE*   |       | ±1   | ±10 | μA    |

| l <sub>IL</sub> | Input Low Current    | V <sub>IN</sub> = GND or 0.4V        |                 |       | ±1   | ±10 | μA    |

| V <sub>CL</sub> | Input Clamp Voltage  | $I_{CL} = -18 \text{ mA}$            |                 | - 1.5 | -0.8 |     | V     |

| ICCD            | Power Supply Current | No Load; DE = RE* = V <sub>CC</sub>  |                 |       | 3    | 7   | mA    |

|                 |                      | $R_L = 55\Omega; DE = RE^* = V_{CC}$ | V <sub>CC</sub> |       | 10   | TBD | mA    |

| ICCR            |                      | $DE = RE^* = 0V$                     |                 |       | 5    | 7   | mA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

Note 2: Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except  $V_{OD}$  and  $V_{ID}$ . Note 3: All typicals are given for  $V_{CC} = +5.0V$  and  $T_A = +25^{\circ}C$ .

Note 4: ESD Rating: HBM (1.5 kΩ, 100 pF) ≥ 2.5 kV

EIAJ (0Ω, 200 pF) ≥ TBD

Note 5: CL includes probe and fixture capacitance.

Note 6: Generator waveform for all tests unless otherwise specified: f = 1 MHz,  $Z_O = 50\Omega$ ,  $t_f \le 1 \text{ ns}$ ,  $t_f \le 1 \text{ ns}$  (0%-100%).

Note 7: The DS36C200 is a current mode device and only function with datasheet specification when a resistive load is applied to the drivers outputs.

Switching Characteristics Over supply voltage and operating temperature ranges, unless otherwise specified (Note 5)

| Symbol            | Paraméter                                  | Conditions                                   | Min | Тур   | Max       | Units |

|-------------------|--------------------------------------------|----------------------------------------------|-----|-------|-----------|-------|

| IFFERENTI         | AL DRIVER CHARACTERISTICS                  | ·                                            |     |       | - 11 - 11 |       |

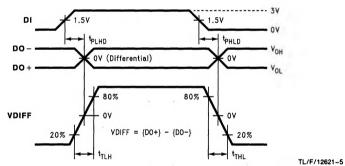

| <sup>t</sup> PHLD | Differential Propagation Delay High to Low | R <sub>L</sub> = 55Ω, C <sub>L</sub> = 50 pF | 1.5 | . 3.4 | 6         | ns    |

| <sup>t</sup> PLHD | Differential Propagation Delay Low to High | (Figures 2 and 3)                            | 1.5 | 3.50  | 6         | ns    |

| tsKD              | Differential Skew  tPHLD-tPLHD             |                                              | 0.1 | 0.1   | 2         | ns    |

| tTLH              | Transition Time Low to High                |                                              | 0   | 0.5   | 2         | ns    |

| <b>t</b> THL      | Transition Time High to Low                |                                              | 0   | 0.5   | 2         | ns    |

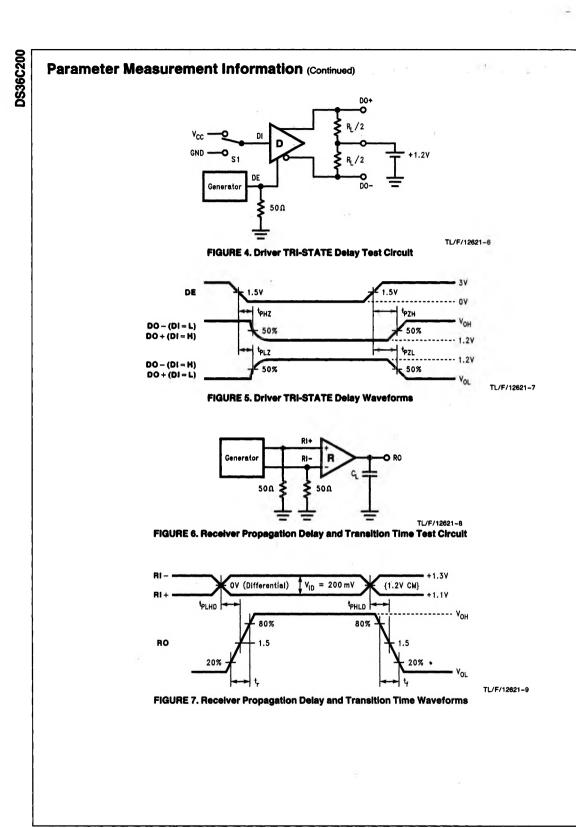

| <sup>t</sup> PHZ  | Disable Time High to Z                     | $R_L = 55\Omega$                             | 0.3 | 5     | 20        | ns    |

| tPLZ              | Disable Time Low to Z                      | (Figures 4 and 5)                            | 0.3 | 5     | 20        | ns    |

| t <sub>PZH</sub>  | Enable Time Z to High                      |                                              | 0.3 | 10    | 30        | ns    |

| tPZL              | Enable Time Z to Low                       |                                              | 0.3 | 10    | 30        | ns    |

| IFFERENTI         | AL RECEIVER CHARACTERISTICS                |                                              |     |       |           |       |

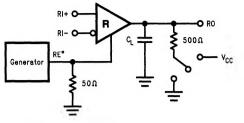

| <sup>t</sup> PHLD | Differential Propagation Delay High to Low | $C_{L} = 50  pF, V_{ID} = 200  mV$           | 1.5 | 3.4   | 6         | ns    |

| t <sub>PLHD</sub> | Differential Propagation Delay Low to High | (Figures 6 and 7)                            | 1.5 | 3.5   | 6         | ns    |

| tSKD              | Differential Skew  tPHLD-tPLHD             |                                              | 0.1 | 0.1   | 2         | ns    |

| t <sub>r</sub>    | Rise Time                                  | *                                            | 0   | 0.5   | 2.5       | ns    |

| tr                | Fall Time                                  |                                              | 0   | 0.5   | 2.5       | ns    |

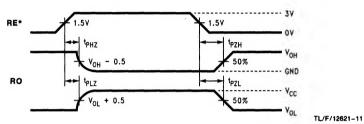

| t <sub>PHZ</sub>  | Disable Time High to Z                     | C <sub>L</sub> = 5 pF                        | 1   | 10    | 20        | ns    |

| t <sub>PLZ</sub>  | Disable Time Low to Z                      | (Figures 8 and 9)                            | 1   | 10    | 20        | ns    |

| t <sub>PZH</sub>  | Enable Time Z to High                      |                                              | 0.3 | 10    | 30        | ns    |

| t <sub>PZL</sub>  | Enable Time Z to Low                       |                                              | 0.3 | 10    | 30        | ns    |

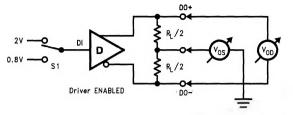

TL/F/12621-3

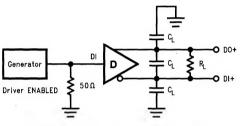

TL/F/12621-4

## **Parameter Measurement Information**

FIGURE 1. Differential Driver DC Test Circuit

FIGURE 2. Differential Driver Propagation Delay and Transition Time Test Circuit

FIGURE 3. Differential Driver Propagation Delay and Transition Time Waveforms

# Parameter Measurement Information (Continued)

FIGURE 8. Receiver TRI-STATE Delay Test Circuit

TL/F/12621-10

FIGURE 9. Receiver TRI-STATE Delay Waveforms

-----

1

# DS36C200

# **Application Information**

## TRUTH TABLES

The DS36C200 has two enable pins DE and RE\*, however, the driver and receiver should never be enabled simultaneously. Enabling both could cause multiple channel contention. It is recommended to route the enables together on the PC board. This will allow a single bit [DE/RE\*] to control the chip. This DE/RE\* bit toggles the DS36C200 between Receive mode and Transmit mode. When the bit is asserted HIGH the device is in Transmit mode. When the bit is asserted LOW the device is in Receive mode. The mode determines the function of the I/O pins: DI/RO, DO/RI+,

| Receive Mode |     |                      |    |  |  |

|--------------|-----|----------------------|----|--|--|

| Input(s)     |     | input/Output         |    |  |  |

| DE           | RE* | [RI+] — [RI—]        | RO |  |  |

| ٢            | L   | > +100 mV            | н  |  |  |

| L            | L   | < – 100 mV           | L  |  |  |

| L            | L   | 100 mV > & > −100 mV | Х  |  |  |

and DO/RI-. Please note that some of the pins have been identified by its function in the corresponding mode in the three tables below. For example, in Transmit mode the DO/RI+ pin is identified as DO+. This was done for clarity in the tables only and should not be confused with the pin identification throughout the rest of this document. Also note that a logic low on the DE/RE\* bit corresponds to a logic low on both the DE pin and the RE\* pin. Similarly, a logic high on the DE/RE\* bit corresponds to a logic high on both the DE pin and the RE\* pin.

### **Transmit Mode**

| Inp | out(s) | Inpu        |     |     |

|-----|--------|-------------|-----|-----|

| DE  | RE*    | DI          | DO+ | DO- |

| н   | н      | L           | L   | н   |

| н   | н      | н           | н   | L   |

| н   | н      | 2 > & > 0.8 | x   | x   |

H = Logic high level

L = Logic low level

X = Indeterminant state

| TABLE I. Device Pin Descriptions |                        |              |                                                                                                      |  |  |

|----------------------------------|------------------------|--------------|------------------------------------------------------------------------------------------------------|--|--|

| Pin #                            | Name<br>(In mode only) | Mode         | Description                                                                                          |  |  |

| 3                                | DE                     | Transmit     | Driver Enable: When asserted low driver is disabled. And when asserted high driver is enabled.       |  |  |

| 1, 7                             | DI                     |              | TTL/CMOS driver input pins                                                                           |  |  |

| 10, 13                           | DO+                    |              | Noninverting driver output pin                                                                       |  |  |

| 11, 12                           | DO-                    |              | Inverting driver output pin                                                                          |  |  |

| 4                                | RE*                    | Receive      | Receiver Enable: When asserted low receiver is enabled. And when asserted high receiver is disabled. |  |  |

| 1, 7                             | RO                     |              | Receiver output pin                                                                                  |  |  |

| 10, 13                           | Ri+                    |              | Positive receiver input pin                                                                          |  |  |

| 11, 12                           | RI-                    |              | Negative receiver input pin                                                                          |  |  |

| 5                                | GND                    | Transmit and | Ground pin                                                                                           |  |  |

| 2                                | V <sub>CC</sub>        | Receive      | Positive power supply pin, $+5V \pm 10\%$                                                            |  |  |

## TARLE I Device Pin Descriptions

## **IEEE 1394**

The DS36C200 drives and receives IEEE 1394 physical layer signal levels. The current mode driver is cabpable of driving a 55  $\Omega$  load with V<sub>OD</sub> between 172 mV and TBD mV. The DS36C200 is not designed to work with a link layer controller IC requiring full 1394 physical layer compliancy to the standard. No clock generator, no arbitration, and no encode/decode logic is provided with this device. For a 1394

link where speed sensing, bus arbitration, and other functions are not required, a controller and the DS36C200 will provide a cost effective, high speed dedicated link. This is shown in Figure 10A. In applications that require fully compliant 1394 protocol, a link layer controller and physical layer controller will be required as shown in Figure 10B. The physical layer controller supports up to three DC36C200 devices (not shown).

DS36C200

http://www.national.com