# DSPAUDIOEVM with DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB User's Guide

Document Number: DSP56720DBUG

Rev. 4 06/2008

#### How to Reach Us:

#### **Home Page:**

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

+1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@ hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2008. All rights reserved.

Document Number: DSP56720DBUG

Rev. 4, 06/2008

# **Contents**

# **About This Book**

|                                                       | Audience Organization Revision History Documentation Available Conventions Definitions, Acronyms, and Abbreviations                                                 | v<br>v<br>vi     |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Chap<br>Over                                          |                                                                                                                                                                     |                  |

| 1.1<br>1.1.1<br>1.1.2<br>1.2<br>1.2.1<br>1.2.2<br>1.3 | Introduction1-Daughterboard1-Motherboard1-Debugger Interfaces1-OnCETM Debugger1-Symphony Debugger Interface1-Configuration, Installation, and Power-Up Procedures1- | 1<br>1<br>2<br>2 |

|                                                       | oter 2<br>iguring the DSPAUDIOEVM Motherboard                                                                                                                       |                  |

| 2.1<br>2.2<br>2.3<br>2.4                              | DSPAUDIOEVM Motherboard Overview 2- Configuration Jumpers 2- Controls and Switches 2- Signal Headers and Connectors 2-                                              | 1<br>6           |

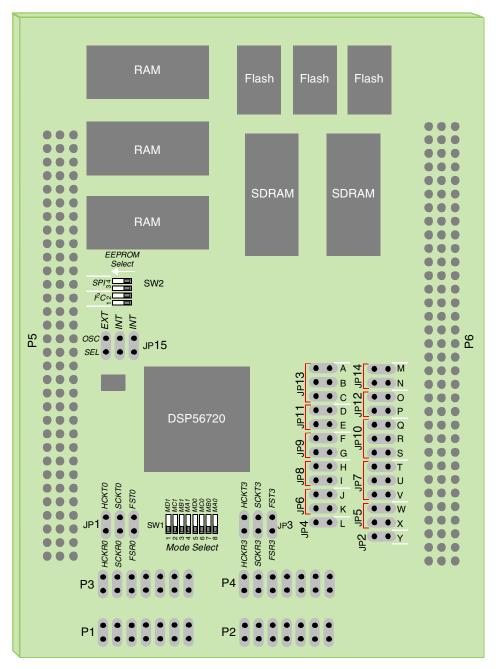

|                                                       | oter 3<br>iguring the DSP56720/DSP56724 Daughterboard                                                                                                               |                  |

| 3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2                   | DSP56720/DSP56724 Daughterboard Overview 3- Configuring Control Jumpers 3- Configuring DIP Switches 3- SW1: DSP Boot Mode Select 3- SW2: EEPROM Select 3-           | 1<br>5<br>5      |

| Chap<br>Conf                                          | oter 4<br>iguring the DSP56721/DSP56725 Daughterboard                                                                                                               |                  |

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2                   | DSP56721/DSP56725 Daughterboard Overview 4- Configuring Control Jumpers 4- Configuring DIP Switches 4- SW1: EEPROM Select 4- SW2: DSP Boot Mode Select 4-           | 1<br>6<br>6      |

DSPAUDIOEVM with DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB, Rev. 4

# Chapter 5 Getting Started

| 5.1        | Running the External Memory Self-Test | 5-1 |  |  |  |  |  |

|------------|---------------------------------------|-----|--|--|--|--|--|

| 5.2        | Running the Audio Passthru Demo       |     |  |  |  |  |  |

| App<br>Pro | pendix A<br>gramming the MCUs         |     |  |  |  |  |  |

| A.1        | Configuring the Motherboard           | A-1 |  |  |  |  |  |

| A.2        | Programming the CONFIG MPU (GP32)     | A-2 |  |  |  |  |  |

| A.3        | Programming the DEBUG MPU (JB16)      | A-2 |  |  |  |  |  |

| A.4        | Troubleshooting Tips                  | A-4 |  |  |  |  |  |

DSPAUDIOEVM with DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB User's Guide, Rev. 4

iv Freescale Semiconductor

#### **About This Book**

Use this document to install and configure a DSP56720, DSP56721, DSP56724, or DSP56725 daughterboard onto a DSPAUDIOEVM motherboard. Together, the daughterboard and motherboard comprise a hardware and software development platform for DSP5672x devices.

#### **Audience**

This document is intended for engineers and programmers who want to prototype and test systems using DSP5672x devices.

# Organization

To install the DSP56720, DSP56721, DSP56724, or DSP56725 daughterboard onto the DSPAUDIOEVM motherboard, follow the procedures in this document.

Chapter 1 Overview Describes the evaluation board set (daughterboard, motherboard), available

debuggers, and basic configure/install/power-up plan.

Chapter 2 Configuring the DSPAUDIOEVM Motherboard

Shows how to configure the DSPAUDIOEVM motherboard.

Chapter 3 Configuring the DSP56720 or DSP56724 Daughterboard

Shows how to configure the DSP56720 or DSP56724 daughterboard.

Chapter 4 Configuring the DSP56721 or DSP56725 Daughterboard

Shows how to configure the DSP56721 or DSP56725 daughterboard.

Chapter 5 Getting Started

Describes how to complete the installation procedure, and pass audio using a passthru code or perform an external memory test.

Appendix A Programming the MCUs

Shows how to program the microcontrollers (CONFIG, DEBUG) on the motherboard

# **Revision History**

The following table summarizes revisions to this document.

#### **Revision History**

| Revision | Date                                                  | Description |  |  |

|----------|-------------------------------------------------------|-------------|--|--|

| 4        | 4 June 2008 Updated to include DSP56724 and DSP56725. |             |  |  |

DSPAUDIOEVM with DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB User's Guide, Rev. 4

Freescale Semiconductor

#### **About This Book**

#### **Documentation Available**

#### **Documentation Available**

| Order Number | Document                                                     | Description                                                                              |

|--------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------|

| DSP56720FS   | Symphony <sup>TM</sup> Audio<br>DSP56720/DSP56721 Fact Sheet | Provides a brief overview of DAP56720/DSP56721 features and benefits.                    |

| DSP56720PB   | Symphony DSP56720 Dual-Core Audio<br>Processor Product Brief | Provides a detailed overview of the DSP56720 device.                                     |

| DSP56721PB   | Symphony DSP56721 Dual-Core Audio<br>Processor Product Brief | Provides a detailed overview of the DSP56721 device.                                     |

| DSP56720RM   | Symphony Audio DSP56720/DSP56721<br>Reference Manual         | Provides detailed hardware-oriented information about the DSP56720 and DSP56721 devices. |

| DSP56724FS   | Symphony <sup>TM</sup> Audio<br>DSP56724/DSP56725 Fact Sheet | Provides a brief overview of DAP56720/DSP56721 features and benefits.                    |

| DSP56724PB   | Symphony DSP56724 Dual-Core Audio<br>Processor Product Brief | Provides a detailed overview of the DSP56720 device.                                     |

| DSP56725PB   | Symphony DSP56725 Dual-Core Audio<br>Processor Product Brief | Provides a detailed overview of the DSP56721 device.                                     |

| DSP56724RM   | Symphony Audio DSP56724/DSP56725<br>Reference Manual         | Provides detailed hardware-oriented information about the DSP56720 and DSP56721 devices. |

| DSP56300FM   | DSP56300 Family Manual                                       | Provides the instruction set for the DSP563xx and DSP5672x devices.                      |

#### Conventions

This document uses the following notational conventions:

- Courier monospaced type indicate commands, command parameters, code examples, expressions, datatypes, and directives.

- *Italic type* indicates replaceable command parameters.

# Definitions, Acronyms, and Abbreviations

The following list defines the acronyms and abbreviations used in this document. As this template develops, this list will be generated from the document. As we develop more group resources, these acronyms will be easily defined from a common acronym dictionary. Please note that while the acronyms are in solid caps, terms in the definition should be initial capped ONLY IF they are trademarked names or proper nouns.

DSP Digital Signal Processor

EVM or EVB Evaluation Module or Evaluation Board

JTAG Joint Test Access Group (a standard test interface)

OnCE<sup>TM</sup> On-Chip Emulation

PPI Parallel Port Interface

DSPAUDIOEVM with DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB User's Guide, Rev. 4

vi Freescale Semiconductor

# Chapter 1 Overview

#### 1.1 Introduction

The DSPAUDIOEVM evaluation board (called the motherboard) and the DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB board (called the daughterboard) demonstrate the abilities of the DSP5672x family of digital signal processors, and also serve as a hardware platform for the development of applications that use these devices.

Used together, the DSPAUDIOEVM and a DSP5672x daughterboard perform the following functions:

- Allow you to become familiar with the features of the specific DSP architecture.

- Serve as a platform for real-time software development. The tool suite enables you to develop and simulate routines, download the software to on-chip or on-board RAM, and then run and debug the software using a debugger through the OnCE<sup>TM</sup> port. The breakpoint features of the OnCE port enable you to easily specify break conditions and to execute your developed software at full speed, until the break conditions are satisfied. The ability to examine and modify all user-accessible registers, memory, and peripherals through the OnCE port simplifies development problems.

- Serve as a platform for hardware development. The hardware platform enables you to connect external hardware peripherals. The on-board peripherals can be disabled, providing you with the ability to reassign any and all of the DSP's peripherals. The OnCE port's unobtrusive design means that all of the memory on the board and on the DSP chip is available to you.

# 1.1.1 Daughterboard

Different daughterboards are available that support the DSP5672x digital signal processor family. Each daughterboard connects to the motherboard using two 96-pin connectors and, depending on the DSP, also contains external SRAM, FLASH or EEPROM. For more information about specific daughterboards, refer to their specific chapter in this document.

#### 1.1.2 Motherboard

The motherboard has a variety of digital and analog audio I/O including:

- Four switchable S/PDIF inputs (two optical and two coaxial)

- Four simultaneous S/PDIF outputs (three coaxial and one coaxial/optical)

- Twelve analog output channels (six stereo RCA-type connectors)

- Two analog microphone inputs

- Two analog inputs (one stereo RCA-type connectors)

- Headphone output (can mix any combination of analog signals using a switch array)

The motherboard uses an included external universal power supply (100–220 VAC, 50–60 Hz). The power supply uses an IEC three-pin power connector for the AC supply. You must supply your own AC cable to connect the included motherboard power supply to the region-specific AC power connection.

DSPAUDIOEVM with DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB User's Guide, Rev. 4

Freescale Semiconductor 1-1

#### Overview

There are two HC08 Freescale microcontrollers included on the motherboard. The two microcontrollers each have a dedicated function (either debug or config) and are re-flashable if a field upgrade is required on the EVM. User programming of these two microcontrollers is possible but is not supported by Freescale Semiconductor. Table 1-1 describes the uses of the on-board microcontrollers.

Table 1-1. On-Board Microcontrollers

| Microcontroller | Description                                                                                                                                                                                                                                                                                       |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Config MPU      | An HC908GP32 microcontroller pre-programmed with software to enable all of the on-board AKM components and clocking mode changes. This "config" microcontroller also controls the mute functionality of the final audio outputs and the switching of the inputs sourced to the DSP daughterboard. |

| Debug MPU       | An HC908JB16 microcontroller which is pre-programmed with software to allow communication (from a host PC to the DSP) via the serial RS232 and USB ports in conjunction with the supplied SDI debugger software.                                                                                  |

# 1.2 Debugger Interfaces

# 1.2.1 OnCE<sup>TM</sup> Debugger

The motherboard supports multiple debugger interfaces. The Freescale high-speed parallel port OnCE command converter tool is embedded in the DSPAUDIOEVM (no special cables are required). An IEEE Std 1284<sup>TM</sup> parallel port cable is included in the EVM kit for convenience. Also included is a OnCE header, for use with external command converters.

The OnCE interface can be used with the Freescale Symphony Studio tool set. To get the latest software and documentation, go to http://www.freescale.com/symphonystudio.

# 1.2.2 Symphony Debugger Interface

In addition to OnCE debugging, the motherboard includes a real-time Symphony Debugger Interface (SDI). This debugger uses either an RS-232 or USB interface and allows SPI or I<sup>2</sup>C communication to the DSP from a PC, for real-time debugging and configuration of the DSP. SDI software and documentation are available on Freescale's website (go to http://www.freescale.com/symphony and click on the Software Tools link.)

SDI version 2.5 or higher is required for use with a DSP56720 or DSP56721 daughterboard and may require an update to the motherboard firmware for proper operation. Only revision D motherboards are shipped from the factory with the SDI 2.5-compatible firmware. The firmware update is included in the online SDI download. Use the procedures in Section Appendix A, "Programming the MCUs," to update the motherboard firmware.

#### NOTE

The SDI debugger software is designed for use with the Software Architecture contained within the ROM of the DSP. The SDI debugger is not designed for use as a stand-alone, general purpose debugger.

DSPAUDIOEVM with DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB User's Guide, Rev. 4

1-2 Freescale Semiconductor

# 1.3 Configuration, Installation, and Power-Up Procedures

To configure the motherboard and daughterboard evaluation system to run using the included sample code, follow the steps shown in Table 1-2.

Table 1-2. Configuration, Installation, and Power-Up Procedures

| Step | Description                                               | See this section                                             |

|------|-----------------------------------------------------------|--------------------------------------------------------------|

| 1    | Configure the motherboard.                                | Chapter 2, "Configuring the DSPAUDIOEVM Motherboard"         |

| 2    | Configure the daughterboard.                              | Chapter 3, "Configuring the DSP56720/DSP56724 Daughterboard" |

| 3    | Install the daughterboard onto the motherboard.           | Chapter 5, "Getting Started"                                 |

| 4    | Connect the power supply to the motherboard and power up. |                                                              |

| 5    | Install/connect all peripherals, cables, and equipment.   |                                                              |

| 6    | Run the passthru code.                                    |                                                              |

| 7    | Observe LEDs.                                             |                                                              |

| 8    | Power down.                                               |                                                              |

Freescale Semiconductor 1-3

Overview

DSPAUDIOEVM with DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB User's Guide, Rev. 4

1-4 Freescale Semiconductor

# **Chapter 2 Configuring the DSPAUDIOEVM Motherboard**

#### 2.1 DSPAUDIOEVM Motherboard Overview

There are eleven jumper blocks on the motherboard that allow you to select various board configurations. Table 2-1 describes how to use this chapter's sections to configure your DSPAUDIOEVM motherboard.

Table 2-1. Configuring the DSPAUDIOEVM Motherboard

| For Information About                 | Go to                                                                                |                            |

|---------------------------------------|--------------------------------------------------------------------------------------|----------------------------|

| Meet the DSPAUDIOEVM motherboard      | Section 2.1, "DSPAUDIOEVM Motherboard Overview"                                      | on page 2-1                |

| Configure jumpers                     | Section 2.2, "Configuration Jumpers"                                                 | on page 2-1                |

| Configure other controls and switches | Section 2.3, "Controls and Switches"<br>Section 2.4, "Signal Headers and Connectors" | on page 2-6<br>on page 2-7 |

# 2.2 Configuration Jumpers

Set or verify the settings for jumpers JP1–JP11 on the motherboard using the tables and figures in this section.

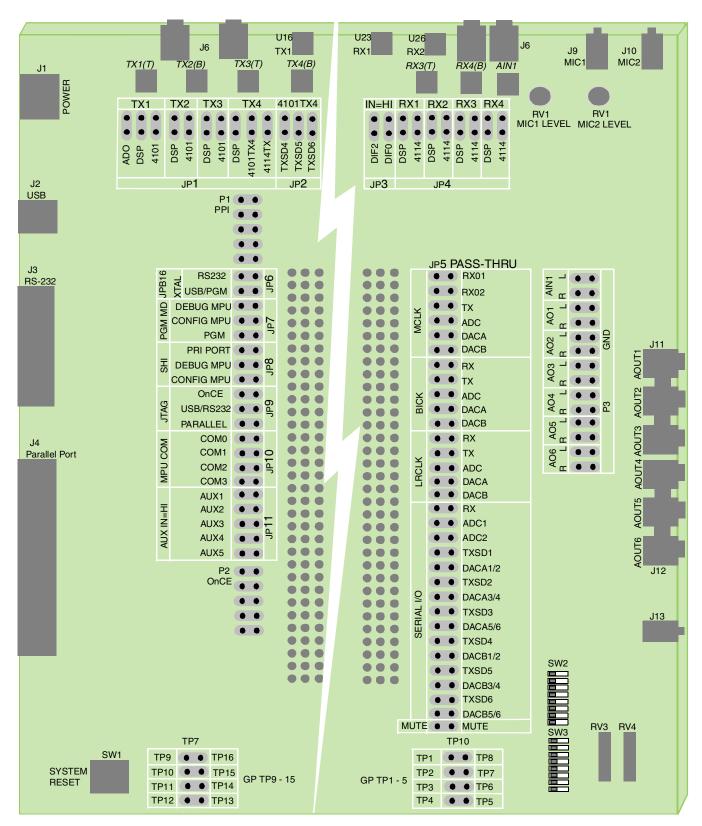

Table 2-2 lists the jumpers on the DSPAUDIOEVM motherboard; to locate the jumpers, see Figure 2-1.

Freescale Semiconductor 2-1

#### Configuring the DSPAUDIOEVM Motherboard

Figure 2-1. Locate Jumpers/Switches on DSPAUDIOEVM

DSPAUDIOEVM with DSP56720DB, DSP56721DB, DSP56724DB, or DSP56725DB User's Guide, Rev. 4

**Table 2-2. Jumper Options**

| Function                          | Jumper | Position                                                                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                                                                             |  |  |  |  |  |

|-----------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| JP1                               |        |                                                                                                                                                                                                                                                                                                                                              | Use JP1 to select the S/PDIF output source. The output may be the daughterboard (DSP), AKM 4101 S/PDIF transmitter, or AKM 4114 S/PDIF receiver.                                                                        |  |  |  |  |  |

| TX2 • 4101<br>• • DSP<br>• • 4101 |        | ADO                                                                                                                                                                                                                                                                                                                                          | This jumper is not supported by the DSP56720 or the DSP56721 daughterboard.                                                                                                                                             |  |  |  |  |  |

| TX3                               | JP1    | DSP                                                                                                                                                                                                                                                                                                                                          | The DSP option for each TX set allows for direct connection to the internal S/PDIF transmitter of the DSP. See the board-specific schematic to determine which DSP signal is connected in this position.                |  |  |  |  |  |

|                                   | JFI    | 4101                                                                                                                                                                                                                                                                                                                                         | The 4101 option for each TX set allows for connection of the I2S outputs from the DSP to the AKM 4101 S/PDIF transmitter. See the board-specific schematic to determine which DSP signal is connected in this position. |  |  |  |  |  |

|                                   |        | 4101TX4                                                                                                                                                                                                                                                                                                                                      | To send one of the S/PDIF signals (TXSD4, TXSD5, or TXSD6) to the TX4 output, select the S/PDIF signal (using a jumper in JP2) and select TX4 (using the 4101TX4 jumper in the TX4 section of JP1).                     |  |  |  |  |  |

|                                   |        | 4114TX4                                                                                                                                                                                                                                                                                                                                      | The 4114TX jumper option on TX4 allows direct connection of the S/PDIF receiver to S/PDIF out.                                                                                                                          |  |  |  |  |  |

| JP2                               | JP2    | TXSD4<br>TXSD5<br>TXSD6                                                                                                                                                                                                                                                                                                                      | <b>TXSD5</b> See the board-specific schematic to determine which DSP signals                                                                                                                                            |  |  |  |  |  |

| JP3 IN=HI ODIF2 ODIF0             | JP3    | The JP3 jumper allows for hardware configuration of the AKM 4114 S/PDIF receiver. The default setting is for software control mode, where the AKM 4114 is configured by the Freescale HC908GP32 configuration microcontroller on the motherboard. See the AKM 4114 manual for details on using this jumper to configure the S/PDIF receiver. |                                                                                                                                                                                                                         |  |  |  |  |  |

| JP4  RX1  DSP  4114               |        |                                                                                                                                                                                                                                                                                                                                              | The JP4 jumper controls the S/PDIF receiver input source to allow direct routing to the daughterboard (using the DSP jumper setting) or to select connection to the AKM 4114.                                           |  |  |  |  |  |

| RX2 DSP 4114                      | JP4    | DSP                                                                                                                                                                                                                                                                                                                                          | The DSP option connects the S/PDIF signal directly to the internal S/PDIF receiver of the DSP.                                                                                                                          |  |  |  |  |  |

| RX3                               |        | 4114                                                                                                                                                                                                                                                                                                                                         | The 4114 option routes the incoming S/PDIF signal through the AKM 4114 S/PDIF receiver and to the I2S signals of the DSP.                                                                                               |  |  |  |  |  |

|                                   |        |                                                                                                                                                                                                                                                                                                                                              | See the board-specific schematics to determine which DSP signals are available for each jumper option.                                                                                                                  |  |  |  |  |  |

Freescale Semiconductor 2-3

#### Configuring the DSPAUDIOEVM Motherboard

**Table 2-2. Jumper Options (continued)**

| Function                                            | Jumper | Position                       | Description                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------|--------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLK    MCLK                                        | JP5    | _                              | The JP5 jumper block provides convenient access to critical audio clocks and data lines. The JP5 jumpers can be removed to allow rerouting of the audio signals within the board and also to allow for expansion to external boards. For example, the JP5 header could be used to connect to an external audio codec board for evaluation of a DSP with a specific audio codec. |

| JP6 JB16 EXTAL ■ RS232 ■ USB/PGM                    |        |                                | Use the JP6 jumper to select the appropriate JB16 clock source.  CAUTION  Only one JP6 jumper should be connected at any one time. Using the                                                                                                                                                                                                                                    |

|                                                     | JP6    |                                | wrong jumper setting can cause SDI communications to fail or cause a reduction in the data transfer rate.                                                                                                                                                                                                                                                                       |

|                                                     |        | RS232                          | To use an RS-232 interface with the SDI debugger, install a jumper at the RS232 position.                                                                                                                                                                                                                                                                                       |

|                                                     |        | USB/PGM                        | Use this jumper if you are using the USB interface with the SDI debugger or to reprogram the debug and configuration microcontrollers.                                                                                                                                                                                                                                          |

| PGM MD  JP7  • • DEBUG MPU  • • CONFIG MPU  • • PGM | JP7    | DEBUG MPU<br>CONFIG MPU<br>PGM | Use the JP7 jumpers to re-program the on-board microcontrollers (Debug MPU, Config MPU). See Appendix A, "Programming the MCUs" for more details regarding re-programming the on-board mircocontrollers.                                                                                                                                                                        |

### **Table 2-2. Jumper Options (continued)**

| Function                     | Jumper   | Position Description |                                                                                                                                                                                               |  |  |

|------------------------------|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 120                          |          |                      | Use the JP8 jumpers to select SDI debugger modes.                                                                                                                                             |  |  |

| JP8  • • PPI PORT            |          |                      | CAUTION                                                                                                                                                                                       |  |  |

| SHI • DEBUG MPU • CONFIG MPU |          |                      | Only one jumper should be installed at a time in any of the three JP8 jumper positions (DEBUG MPU, PPI PORT, CONFIG MPU).                                                                     |  |  |

|                              | JP8      | PPI PORT             | Placing a jumper in the PPI PORT position allows for control via P1, the PPI header. This header can be used with legacy development tools or can be connected to an external microcontroler. |  |  |

|                              |          | DEBUG MPU            | The default selection is to use the SDI debugger (jumper in DEBUG MPU position).                                                                                                              |  |  |

|                              |          | CONFIG MPU           | Not currently supported                                                                                                                                                                       |  |  |

| JP9                          |          |                      | Use the JP9 jumpers to select the OnCE debugger interface.                                                                                                                                    |  |  |

| • • OnCE                     |          |                      | CAUTION                                                                                                                                                                                       |  |  |

| JTAG • USB/RS32 • PARALLEL   |          |                      | Only one jumper should be installed at a time in any of the allowed JP9 jumper positions.                                                                                                     |  |  |

|                              | JP9      | OnCE                 | To connect an <i>external</i> OnCE/JTAG debugger interface to the board via the P2, the OnCE header, install a jumper in the OnCE jumper position.                                            |  |  |

|                              | PARALLEL |                      | Install a jumper in the PARALLEL position of the JP9 jumper and connect the EVM to a host PC with a parallel cable to use the on-board parallel OnCE interface.                               |  |  |

|                              |          | USB/232              | Not currently supported.                                                                                                                                                                      |  |  |

Freescale Semiconductor 2-5

#### Configuring the DSPAUDIOEVM Motherboard

**Table 2-2. Jumper Options (continued)**

| Function | Jumper | Position                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   |                                            |                              |                                       |                    |                |     |   |   |   |   |      |      |      |                   |  |  |   |             |  |   |                  |          |           |           |           |        |   |

|----------|--------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------|------------------------------|---------------------------------------|--------------------|----------------|-----|---|---|---|---|------|------|------|-------------------|--|--|---|-------------|--|---|------------------|----------|-----------|-----------|-----------|--------|---|

| JP10     | JP10   | _                                    | The JP10 jumpers provide a communication port between the debug microcontroller and the configuration microcontroller.  If using the SDI debugger interface, install all JP10 jumpers (positions COM0 - COM3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |                                            |                              |                                       |                    |                |     |   |   |   |   |      |      |      |                   |  |  |   |             |  |   |                  |          |           |           |           |        |   |

| JP11     |        | signal w<br>debugg<br><b>Note:</b> V | 11 jumper allow when not using the reference of the refer | he Symelected<br>umper inality of | phony [<br>as show<br>s install<br>the EV! | Debugge<br>In belowed, the I | er Interf<br>v.<br>Aux4 ju<br>erboard | ace (SI<br>mper co | OI)<br>ontrols |     |   |   |   |   |      |      |      |                   |  |  |   |             |  |   |                  |          |           |           |           |        |   |

|          |        | _                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                 |                                            |                              |                                       |                    |                |     |   |   |   |   |      |      |      | Input<br>Selected |  |  | 1 |             |  | = |                  |          |           |           |           |        |   |

|          |        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                            |                              |                                       |                    |                |     |   |   |   |   | Aux5 | Aux4 | Aux3 | Aux2              |  |  |   |             |  |   |                  |          |           |           |           |        |   |

|          | JP11   |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                            | RX1                          |                                       | 0                  | 0              | 0   | 0 | - |   |   |      |      |      |                   |  |  |   |             |  |   |                  |          |           |           |           |        |   |

|          | 0      |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                            | RX2                          |                                       | 0                  | 0              | 0   | 1 |   |   |   |      |      |      |                   |  |  |   |             |  |   |                  |          |           |           |           |        |   |

|          |        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                            |                              |                                       |                    | RX3            | 1   | 0 | 0 | 1 | 0 |      |      |      |                   |  |  |   |             |  |   |                  |          |           |           |           |        |   |

|          |        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                            |                              |                                       |                    |                | RX4 |   | 0 | 0 | 1 | 1    |      |      |                   |  |  |   |             |  |   |                  |          |           |           |           |        |   |

|          |        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                            |                              |                                       |                    |                |     |   |   |   |   |      |      |      |                   |  |  |   | AIN1 48 KHz |  | 0 | 1                | 0        | 0         |           |           |        |   |

|          |        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AIN1 96 KHz                       |                                            | 0                            | 1                                     | 0                  | 1              |     |   |   |   |   |      |      |      |                   |  |  |   |             |  |   |                  |          |           |           |           |        |   |

|          |        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SDI debugger selects input        | 0                                          | Х                            | Х                                     | Х                  | Х              |     |   |   |   |   |      |      |      |                   |  |  |   |             |  |   |                  |          |           |           |           |        |   |

|          |        | 1                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                            |                              |                                       |                    |                |     |   |   |   |   |      |      |      |                   |  |  |   |             |  | ' | 1 = jumper is ir | nstalled | , 0 = jun | nper is r | not insta | alled. | • |

## 2.3 Controls and Switches

Other devices allow you additional control of the microphone and headphone functions. See Figure 2-1 for control and switch locations.

**Table 2-3. Controls and Switches**

| Function                | Control or<br>Switch | Description                                                                                                                                                                                                                                                                           |  |  |

|-------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Microphone Gain Control | RV1, RV2             | The RV1 and RV2 potentiometers control the input levels for MIC1 and MIC2 respectively. To prevent damage, always start with these controls in a low setting, turned all the way counter-clockwise. These inputs can be monitored directly by using the on-board headphone amplifier. |  |  |

Table 2-3. Controls and Switches (continued)

| Function                 | Control or<br>Switch | Description                                                                                                                                                                                                                                                                                                         |

|--------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Headphone Volume Select  | RV3, RV4             | The RV3 and RV4 sliders control volume and balance adjustment for the headphone amplifier. To prevent damage to the headphones or your hearing, always start with the sliders in a low-volume position.                                                                                                             |

| Headphone Channel Select | SW2, SW3             | The SW2 and SW3 switches control which analog output is routed to the on-board headphone amplifier. Moving the switch to the right (the ON position) enables the corresponding channel. Multiple switches/channels can be enabled at one time, and the signals are summed into the corresponding headphone channel. |

# 2.4 Signal Headers and Connectors

Signal headers and connectors allow external debugger connections, analog output signal measurement, and GPIO access. Headers and connectors are listed in Table 2-4.

**Table 2-4. Signal Headers and Connectors**

| Function | Connector or Header | Description                                                                                                                                                                                                                                          |                                        |                                                                        |   |                                             |  |  |

|----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------|---|---------------------------------------------|--|--|

| PPI      |                     | The PPI header connections allow for backwards compatibility with legacy software tool sets, and also allow                                                                                                                                          |                                        | <b>P1</b> – PPI                                                        |   |                                             |  |  |

|          |                     | easy access to the SHI port signals from the DSP. To use the PPI header, JP8 must have a jumper installed                                                                                                                                            | NC (Pin 1)                             | *                                                                      | * | SS/HA2                                      |  |  |

|          | P1                  | in the PPI PORT location.                                                                                                                                                                                                                            | GND                                    | *                                                                      | * | SCK/SCL                                     |  |  |

|          | • •                 |                                                                                                                                                                                                                                                      | GND                                    | *                                                                      | * | SS_1/HA2_1                                  |  |  |

|          |                     |                                                                                                                                                                                                                                                      | MISO/SDA                               | *                                                                      | * | MOSI/HA0                                    |  |  |

|          |                     |                                                                                                                                                                                                                                                      | 3.3V                                   | *                                                                      | * | MISO/SDA                                    |  |  |

| OnCE     | P2                  | Use the P2 OnCE header to connect an external OnCE/JTAG debugger tool to the OnCE/JTAG port of the DSP on the daughterboard. When using an external OnCE/JTAG debugger tool, a jumper must be installed in the OnCE position of the JP9 JTAG jumper. | TDI (Pin 1 TDO TCK N/C RESET 3.3 V N/C | P2 – OnCE in 1) * * GND O * * GND K * GND C * KEY ET * * TMS V * * N/C |   | * GND * GND * GND  * GND  * KEY * TMS * N/C |  |  |

Freescale Semiconductor 2-7

#### Configuring the DSPAUDIOEVM Motherboard

Table 2-4. Signal Headers and Connectors (continued)