# 1400 Bit Serial Electrically Alterable Read Only Memory

#### **FEATURES**

- 100 word x 14 bit organization

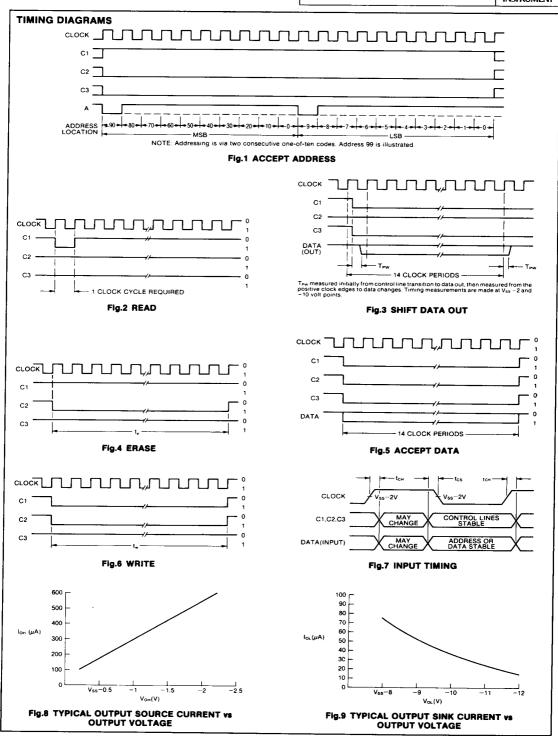

- Addressing by two consecutive one-of-ten codes

- Single -35 Volt supply

- Word alterable

- 10 year data storage

- MOS compatible signal levels

- Write/erase time: 10ms

#### DESCRIPTION

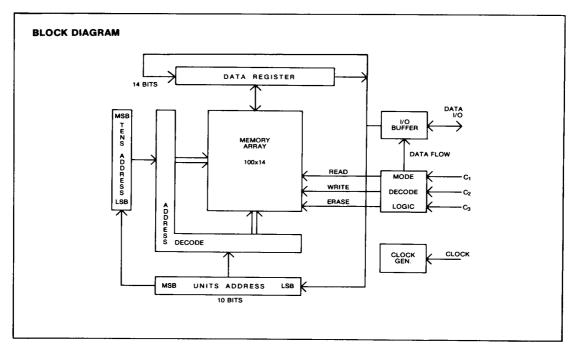

The ER1400 is a serial input/output 1400 bit electrically erasable and reprogrammable ROM, organized as 100 words of 14 bits each. Data and address are communicated in serial form via a one-pin bidirectional bus.

Mode selection is by a 3 bit code applied to C1, C2 and C3.

Before writing, a selected location must be preconditioned by an Erase operation. Data is then stored by internal negative writing pulses that selectively tunnel charge into the oxide-nitride interface of the gate insulator of the 1400 MNOS memory transistors. When the writing voltage is removed the charge trapped at the interface is manifested as a negative shift in the threshold voltage of the selected memory transistors.

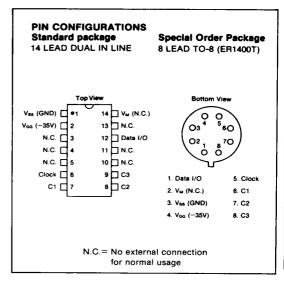

### PIN FUNCTIONS

| Name           | Function                                                                                                 |                                                                                |           |                                                                                                                                                             |  |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Data           | In the Accept Address and Accept Data modes, this pin is an input pin for address and data respectively. |                                                                                |           |                                                                                                                                                             |  |  |  |  |  |

|                | Wh                                                                                                       | en out                                                                         | putting   | data it has MOS drive capability, while in all other modes it is left floating.                                                                             |  |  |  |  |  |

| V <sub>M</sub> | Use                                                                                                      | Used for testing purposes only. Must be left unconnected for normal operation. |           |                                                                                                                                                             |  |  |  |  |  |

| Vss            | Chip substrate. Normally connected to ground.                                                            |                                                                                |           |                                                                                                                                                             |  |  |  |  |  |

| $V_{GG}$       | DC supply. Normally connected to V <sub>SS</sub> =35 Volt supply.                                        |                                                                                |           |                                                                                                                                                             |  |  |  |  |  |

| Clock          | Timing reference. Required for all operations. May be left at logic zero when device is in standby.      |                                                                                |           |                                                                                                                                                             |  |  |  |  |  |

| C1,C2,C3       | Mode control pins. Their operation is as follows:                                                        |                                                                                |           |                                                                                                                                                             |  |  |  |  |  |

|                | Ç1                                                                                                       | <u>C2</u>                                                                      | <u>C3</u> | <u>Function</u>                                                                                                                                             |  |  |  |  |  |

|                | ٥                                                                                                        | 0                                                                              | 0         | Standby—the output buffer is left floating. If the clock is maintained, the contents of the Address and Data Registers will remain unchanged.               |  |  |  |  |  |

|                | ٥                                                                                                        | 1                                                                              | 1         | Accept Address—Data presented at the I/O pin is shifted into the Address Register with each clock pulse. Addressing is by two consecutive one-of-ten codes. |  |  |  |  |  |

|                | 1                                                                                                        | 0                                                                              | 0         | Read—The address word is read from memory into the data register.                                                                                           |  |  |  |  |  |

|                | 1                                                                                                        | 0                                                                              | 1         | Shift Data Out—The output driver is enabled and the contents of the Data Register are shifted out one bit with each clock pulse.                            |  |  |  |  |  |

|                | 0                                                                                                        | 1                                                                              | 0         | Erase—The word stored at the addressed location is erased to all ones.                                                                                      |  |  |  |  |  |

|                | 1                                                                                                        | 1                                                                              | 1         | Accept Data—The data register accepts serial data presented at the I/O pin. The Address Register remains unchanged.                                         |  |  |  |  |  |

|                | 1                                                                                                        | 1                                                                              | 0         | Write—The word contained in the Data Register is written into the location designated by the Address Register.                                              |  |  |  |  |  |

|                | ١٥                                                                                                       | 0                                                                              | 1         | Not Used                                                                                                                                                    |  |  |  |  |  |

## **ELECTRICAL CHARACTERISTICS**

## Maximum Ratings\*

| All inputs and outputs (except V <sub>GG</sub> ) with respect to V <sub>S</sub> | $_{ss} \dots -$ 20V to $+$ 0.3V |

|---------------------------------------------------------------------------------|---------------------------------|

| V <sub>GG</sub> with respect to V <sub>SS</sub>                                 |                                 |

| Storage temperature (No Data Retention)                                         | 65°C to +150°C                  |

| Storage temperature (with Data Retention)                                       |                                 |

| Operating                                                                       | 25°C to +75°C                   |

| Unnoward                                                                        | -65°C +0 ±90°C                  |

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

#### Standard Conditions (unless otherwise noted):

$V_{SS} = GND$  $V_{GG} = -35V \pm 8\%$

Operating Temperature TA = 0°C to +70°C

| Characteristics                        | Symbol          | Min                  | Тур** | Max                  | Units | Conditions                  |

|----------------------------------------|-----------------|----------------------|-------|----------------------|-------|-----------------------------|

| DC CHARACTERISTICS                     |                 |                      |       |                      |       |                             |

| Input logic "1"                        | V <sub>IL</sub> | Vss-15.0             | _     | V <sub>ss</sub> -8.0 | Volts |                             |

| Input logic "0"                        | VIH             | V <sub>ss</sub> -1.0 | _     | Vss+0.3              | Volts |                             |

| Input leakage                          | I IL            |                      | _     | 10                   | μA    | $V_{1N} = -15V$             |

| Output logic "1"                       | Vol             | _                    |       | Vss12.0              | Volts | Load = 1.5 Meg, 100pF       |

| Output logic "0"                       | V <sub>OH</sub> | V <sub>ss</sub> -1.0 | _     | Vss+0.3              | Volts | I <sub>SOURCE</sub> = 200µA |

| Power consumption                      | PGG             | _                    | _     | 300                  | mW    |                             |

| Power supply current                   | Igg             | -                    | _     | 8.0                  | mA    |                             |

| AC CHARACTERISTICS                     |                 |                      |       |                      |       |                             |

| Clock Frequency                        | fφ              | 10.0                 | 14.0  | 17.0                 | kHz   |                             |

| Clock duty cycle                       | Dφ              | 35                   | 50    | 65                   | %     |                             |

| Write time                             | tw              | 10.0                 | 15.0  | 24.0                 | ms    |                             |

| Erase time                             | te              | 10.0                 | 15.0  | 24.0                 | ms    |                             |

| Rise, fall time                        | tr, tf          | _                    | _     | 1.0                  | μs    |                             |

| Control, Data set up time              | tcs             | 1                    | _     | _                    | μs    |                             |

| Control, Data hold time                | tсн             | 0                    | _     | _                    | μs    | !                           |

| Propagation delay                      | tpw             | _                    | _     | 20.0                 | μs    | Load - 1 Meg. 100pF         |

| Non-volatile data storage              | Ts              | 10                   | _     | _                    | Years | See Note 1.                 |

| Number of erase/write cycles           | Nw              | _                    | _     | 10 <sup>4</sup>      |       | Per word. See Note 2.       |

| Number of read accesses between writes | NRA             | 10°                  | _     | _                    | -     | Per word                    |

<sup>\* \*</sup> Typical values are at +25°C and nominal voltages.

NOTE 1: Ts is for powered or unpowered storage.

NOTE 2: N<sub>W</sub> (=10<sup>4</sup>) is a maximum for data retention times greater than 10 years. Beyond 10<sup>4</sup> reprogramming cycles, there is a gradual, logarithmic reduction in retention time with 1 year being a typical value after 10<sup>5</sup> cycles.

ER1400