# Fixed-Output Synchronous TinyBoost® Regulator

## Description

The FAN48615 is a low-power PWM only boost regulator designed to provide a minimum voltage-regulated rail from a standard single-cell Li-Ion battery and advanced battery chemistries. Even below the minimum system battery voltage, the device maintains the output voltage regulation for an output load current of 1000 mA. The combination of built-in power transistors, synchronous rectification, and low supply current suit the FAN48615 for battery-powered applications.

The FAN48615 is available in a 9-bump, 0.4 mm pitch, (1.215 x 1.215 mm) Wafer-Level Chip-Scale Package (WLCSP).

#### **Features**

- Input Voltage Range: 2.7 V to 5.5 V

- Output Voltage: 5.25 V and 5.4 V

- 1000 mA Max. Load Capability

- PWM Only

- Up to 97% Efficient

- Forced Pass-Through Operation via EN Pin

- Internal Synchronous Rectification

- True Load Disconnect

- Short-Circuit Protection

- Three External Components: 2016 (Metric) 0.47 μH Inductor, 0402 Input and 0603 Output Capacitors

- This is a Pb-Free Device

#### **Applications**

- Class-D Audio Amplifier

- Boost for Low-Voltage Li-Ion Batteries

- Smart Phones, Tablets, Portable Devices

- RF Applications

- NFC Applications

## ON Semiconductor®

www.onsemi.com

#### MARKING DIAGRAM

KY / KZ = Specific Device Code

F = Fab Indicator

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

Pb-Free Package

(Note: Microdot may be in either location)

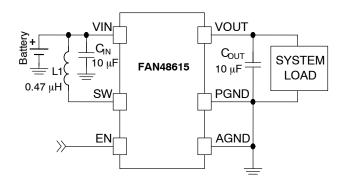

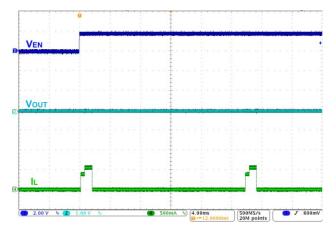

Figure 1. Typical Application

#### **ORDERING INFORMATION**

| Part Number   | V <sub>OUT</sub> | Operating Temperature | Package               | Packing            | Device Marking |

|---------------|------------------|-----------------------|-----------------------|--------------------|----------------|

| FAN48615UC08X | 5.25 V           | -40°C to 85°C         | 9-Bump, 0.4 mm Pitch, | 3000 / Tape & Reel | KY             |

| FAN48615UC11X | 5.40 V           |                       | WLCSP Package         |                    | KZ             |

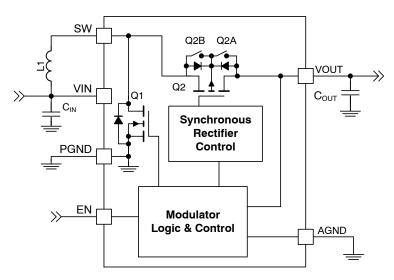

# **Block Diagram**

Figure 2. IC Block Diagram

**Table 1. RECOMMENDED COMPONENTS**

| Component        | Description                     | Vendor                     | Parameter      | Typical Value | Unit |

|------------------|---------------------------------|----------------------------|----------------|---------------|------|

| L1               | 20%, 5.3 A, 2016, 1.0 mm Height | DFE201610E-R47M<br>TOKO    | Inductance     | 470           | nH   |

|                  |                                 | TOKO                       | DCR (Series R) | 26            | mΩ   |

| C <sub>IN</sub>  | 20%, 6.3 V, X5R, 0402 (1005)    | C1005X5R0J106M050BC<br>TDK | Capacitance    | 10            | μF   |

| C <sub>OUT</sub> | 20%, 10 V, X5R, 0603 (1608)     | C1608X5R1A106K080AC<br>TDK | Capacitance    | 10            | μF   |

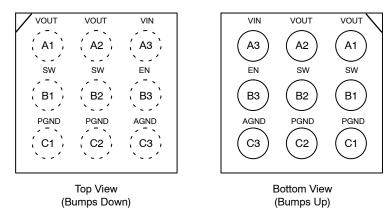

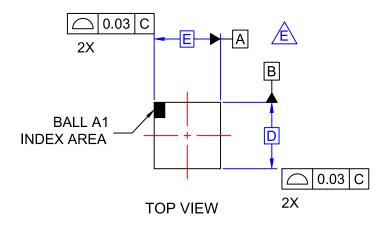

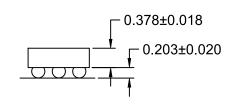

# **Pin Configuration**

Figure 3. Pin Assignment

## **Pin Definitions**

## **Table 2. PIN DEFINITIONS**

| Pin # | Name | Description                                                                                                                                                    |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1    | VOUT | Output Voltage. This pin is the output voltage terminal; connect directly to C <sub>OUT</sub> .                                                                |

| A2    |      |                                                                                                                                                                |

| A3    | VIN  | Input Voltage. Connect to Li-lon battery input power source and C <sub>IN</sub> .                                                                              |

| B1    | SW   | Switching Node. Connect to inductor.                                                                                                                           |

| B2    |      |                                                                                                                                                                |

| ВЗ    | EN   | <b>Enable</b> . When this pin is HIGH, the circuit is enabled. After part is engaged, pin forces part into Forced-Pass-Through Mode when EN pin is pulled LOW. |

| C1    | PGND | Power Ground. This is the power return for the IC. C <sub>OUT</sub> capacitor should be returned                                                               |

| C2    |      | with the shortest path possible to these pins.                                                                                                                 |

| С3    | AGND | Analog Ground. This is the signal ground reference for the IC. All voltage levels are measured with respect to this pin – connect to PGND at a single point.   |

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                |                                                   | Min  | Max                | Unit |

|------------------|------------------------------------------|---------------------------------------------------|------|--------------------|------|

| V <sub>IN</sub>  | Voltage on VIN Pin                       |                                                   | -0.3 | 6.0                | V    |

| V <sub>OUT</sub> | Voltage on VOUT Pin                      | Voltage on VOUT Pin                               |      | 6.0                | V    |

| V <sub>SW</sub>  | SW Node                                  | SW Node DC                                        |      | 6.0                | V    |

|                  | Transient: 10 ns, 3 MHz                  |                                                   | -1.0 | 8.0                |      |

| V <sub>CC</sub>  | Voltage on Other Pins                    |                                                   | -0.3 | 6.0 <sup>(1)</sup> | V    |

| ESD              | Electrostatic Discharge Protection Level | Human Body Model, ANSI/ESDA/<br>JEDEC JS-001-2012 | 2.0  |                    | kV   |

|                  |                                          | Charged Device Model, JESD22-C101                 | 1    | .0                 |      |

| TJ               | Junction Temperature                     |                                                   | -40  | 150                | °C   |

| T <sub>STG</sub> | Storage Temperature                      |                                                   | -65  | 150                | °C   |

| TL               | Lead Soldering Temperature, 10 Seconds   |                                                   |      | 260                | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **Table 4. RECOMMENDED OPERATING CONDITIONS**

| Symbol           | Parameter                                                  | Min  | Max | Unit |

|------------------|------------------------------------------------------------|------|-----|------|

| V <sub>IN</sub>  | Supply Voltage for Boost & Auto Pass Through Operation (2) | 2.7  | 5.5 | V    |

| I <sub>OUT</sub> | Maximum Output Current                                     | 1000 |     | mA   |

| T <sub>A</sub>   | Ambient Temperature                                        | -40  | 85  | °C   |

| T <sub>J</sub>   | Junction Temperature                                       | -40  | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **Table 5. THERMAL PROPERTIES**

|   | Symbol            | Parameter                              | Typical | Unit |

|---|-------------------|----------------------------------------|---------|------|

| ĺ | $\theta_{\sf JA}$ | Junction-to-Ambient Thermal Resistance | 50      | °C/W |

NOTE: Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards with vias in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature,  $T_{J(max)}$ , at a given ambient temperature,  $T_A$ .

<sup>1.</sup> Lesser of 6.0 V or  $V_{IN}$  + 0.3 V.

<sup>2.</sup> When VIN nears VOUT the part will automatically go into pass through mode, depending on load current.

#### **Table 6. ELECTRICAL CHARACTERISTICS**

Recommended operating conditions, unless otherwise noted, circuit per Figure 1,  $V_{OUT} = 5.40 \text{ V}$ . Typical, minimum and maximum values are given at  $V_{IN}$  = 3.6 V,  $T_A$  = 25°C, -40°C and +85°C.

| Symbol                | Parameter                                     | Conditions                                                       | Min  | Тур  | Max | Unit |

|-----------------------|-----------------------------------------------|------------------------------------------------------------------|------|------|-----|------|

| Power Supply          | ,                                             |                                                                  |      |      |     |      |

| IQ                    | V <sub>IN</sub> Quiescent Current             | I <sub>OUT</sub> = 0 mA, EN = 1.8 V, No Switching                |      | 95   |     | μΑ   |

|                       |                                               | Forced Pass-Through EN = 0 V, V <sub>OUT</sub> = V <sub>IN</sub> |      | 3.5  |     |      |

| V <sub>UVLO</sub>     | Under-Voltage Lockout                         | V <sub>IN</sub> Rising                                           |      | 2.20 |     | V    |

| V <sub>UVLO_HYS</sub> | Under-Voltage Lockout Hysteresis              |                                                                  |      | 150  |     | mV   |

| Inputs                |                                               |                                                                  |      |      |     |      |

| V <sub>IH</sub>       | Enable HIGH Voltage                           |                                                                  | 1.05 |      |     | V    |

| $V_{IL}$              | Enable LOW Voltage                            |                                                                  |      |      | 0.4 | V    |

| Outputs               |                                               |                                                                  |      |      |     |      |

| V <sub>REG</sub>      | Output Voltage Accuracy DC (3)                | 2.7 V ≤ V <sub>IN</sub> ≤ 4.5 V                                  | -2   |      | +2  | %    |

| Timing                | •                                             |                                                                  | •    | •    | •   | •    |

| f <sub>SW</sub>       | Switching Frequency                           | I <sub>OUT</sub> = 300 mA                                        | 1.8  | 2.3  | 2.8 | MHz  |

| t <sub>SS</sub> (4)   | EN HIGH to 95% of Regulation                  | I <sub>OUT</sub> = 150 mA                                        |      | 440  |     | μs   |

| t <sub>RST</sub> (4)  | FAULT Restart Timer                           |                                                                  |      | 20   |     | ms   |

| Power Stage           |                                               |                                                                  |      |      |     |      |

| R <sub>DS(ON)N</sub>  | N-Channel Boost Switch R <sub>DS(ON)</sub>    |                                                                  |      | 63   |     | mΩ   |

| R <sub>DS(ON)P</sub>  | P-Channel Sync. Rectifier R <sub>DS(ON)</sub> |                                                                  |      | 52   |     | mΩ   |

<sup>3.</sup> DC  $I_{LOAD}$  from 0 to 1 A.  $V_{OUT}$  measured from mid–point of output voltage ripple. Effective capacitance of  $C_{OUT} \ge 2.2 \ \mu F$ . 4. Guaranteed by design and characterization; not tested in production.

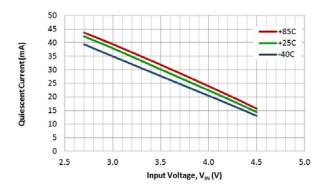

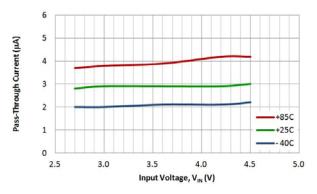

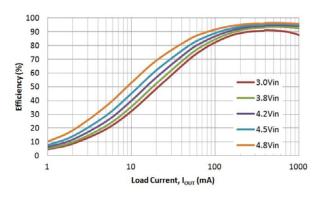

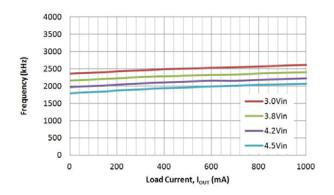

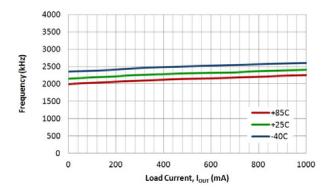

#### **Typical Performance Characteristics**

Unless otherwise specified;  $V_{IN}$  = 3.8 V,  $V_{OUT}$  = 5.40 V,  $T_A$  = 25°C, and circuit according to Figure 1.

Components:  $C_{IN} = 10 \mu F$  (0402, X5R, 6.3 V, C1005X5R0J106M050BC),  $C_{OUT} = 10 \mu F$  (0603, X5R,

10 V, C1608X5R1A106K080AC), L1 = 470 nH (2016, 26 mΩ, DFE201610E–R47M ).

Figure 4. Quiescent Current (Switching) vs. Input Voltage and Temperature

Figure 5. Pass-Through Current vs. Input Voltage and Temperature

Figure 6. Efficiency vs. Load Current and Input Voltage

Figure 7. Efficiency vs. Load Current and Temperature

Figure 8. Switching Frequency vs. Load Current and Input Voltage

Figure 9. Switching Frequency vs. Load Current and Temperature

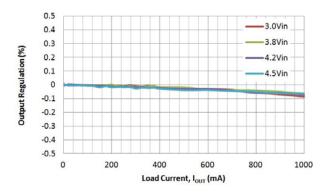

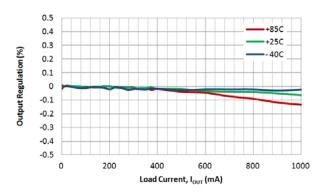

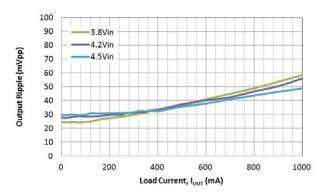

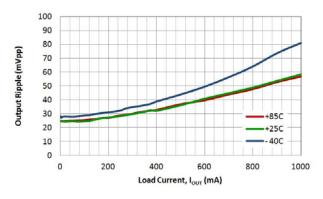

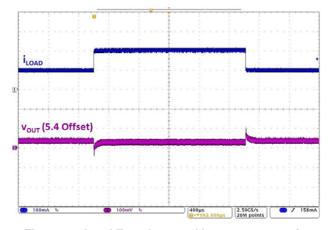

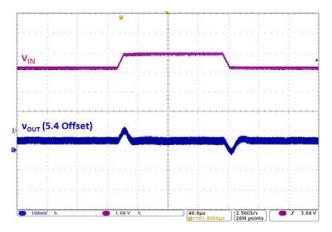

#### **Typical Performance Characteristics**

Unless otherwise specified;  $V_{IN} = 3.8 \text{ V}$ ,  $V_{OUT} = 5.40 \text{ V}$ ,  $T_A = 25$ °C, and circuit according to Figure 1.

Components:  $C_{IN} = 10 \mu F$  (0402, X5R, 6.3 V, C1005X5R0J106M050BC),  $C_{OUT} = 10 \mu F$  (0603, X5R,

10 V, C1608X5R1A106K080AC), L1 = 470 nH (2016, 26 mΩ, DFE201610E–R47M ).

Figure 10. Output Regulation vs. Load Current and Input Voltage

Figure 11. Output Regulation vs. Load Current and Temperature

Figure 12. Output Ripple vs. Load Current and Input Voltage

Figure 13. Output Ripple vs. Load Current and Temperature

Figure 14. Load Transient, 3.6  $V_{IN},\,100 \leftrightarrow 200$  mA, 1  $\mu s$  Edge

Figure 15. Line Transient, 50 mA, 3.2 V  $\leftrightarrow$  3.9 V, 10  $\mu s$  Edge

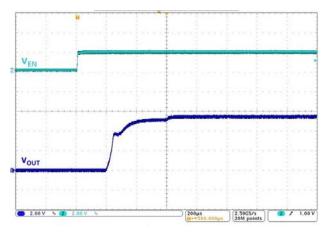

## **Typical Performance Characteristics**

Unless otherwise specified;  $V_{IN}$  = 3.8 V,  $V_{OUT}$  = 5.40 V,  $T_A$  = 25°C, and circuit according to Figure 1.

Components:  $C_{IN}$  = 10  $\mu F$  (0402, X5R, 6.3 V, C1005X5R0J106M050BC),  $C_{OUT}$  = 10  $\mu F$  (0603, X5R,

10 V, C1608X5R1A106K080AC), L1 = 470 nH (2016, 26 m $\Omega$ , DFE201610E–R47M ).

Figure 16. Startup, 150 mA Load

Figure 17. Fault Restart

#### CIRCUIT DESCRIPTION

FAN48615 is a synchronous PWM Only boost regulator. The regulator's Pass-Through Mode automatically activates when VIN is above the boost regulator's set point.

**Table 7. OPERATING MODES**

| Mode | Description          | Invoked When:                                                                                   |

|------|----------------------|-------------------------------------------------------------------------------------------------|

| LIN  | Linear Startup       | V <sub>IN</sub> > V <sub>OUT</sub>                                                              |

| SS   | Boost Soft-Start     | V <sub>IN</sub> < V <sub>OUT</sub> < V <sub>OUT</sub> (TARGET)                                  |

| BST  | Boost Operating Mode | V <sub>OUT</sub> = V <sub>OUT(TARGET)</sub>                                                     |

| PT   | Pass-Through Mode    | V <sub>IN</sub> > V <sub>OUT(TARGET)</sub> or<br>when EN is pulled LOW<br>after initial startup |

### **Boost Mode Regulation**

The FAN48615 uses a current-mode modulator to achieve excellent transient response.

**Table 8. BOOST STARTUP SEQUENCE**

| Start<br>Mode | Entry                         | Exit                                           | End<br>Mode | Timeout<br>(μs) |

|---------------|-------------------------------|------------------------------------------------|-------------|-----------------|

| LIN1          | V <sub>IN</sub> >             | $V_{OUT} > V_{IN} - 300 \text{ mV}$            | SS          |                 |

|               | V <sub>UVLO</sub> ,<br>EN = 1 | Timeout                                        | LIN2        | 512             |

| LIN2          | LIN1 Exit                     | V <sub>OUT</sub> > V <sub>IN</sub> - 300 mV    | SS          |                 |

|               |                               | Timeout                                        | FAULT       | 1024            |

| SS            | LIN1 or<br>LIN2 Exit          | V <sub>OUT</sub> =<br>V <sub>OUT(TARGET)</sub> | BST         |                 |

|               |                               | Overload Timeout                               | FAULT       | 64              |

#### **LIN Mode**

When EN is HIGH and  $V_{IN} > V_{UVLO}$ , the regulator first attempts to bring  $V_{OUT}$  within 300 mV of  $V_{IN}$  by using the internal fixed-current source from VIN (Q2). The current is limited to the LIN1 set point.

If  $V_{OUT}$  reaches  $V_{IN}\text{--}300$  mV during LIN1 Mode, the SS Mode is initiated. Otherwise, LIN1 times out after 512  $\mu s$  and LIN2 Mode is entered.

In LIN2 Mode, the current source is incremented. If  $V_{OUT}$  fails to reach  $V_{IN}$ -300 mV after 1024  $\mu s$ , a fault condition is declared and the device waits 20 ms to attempt an automatic restart.

## Soft-Start (SS) Mode

Upon the successful completion of LIN Mode ( $V_{OUT} \ge V_{IN}$ – 300 mV), the regulator begins switching with boost pulses current limited to 50% of nominal level.

During SS Mode, if  $V_{OUT}$  fails to reach regulation during the SS ramp sequence for more than 64  $\mu$ s, a fault is declared. If large  $C_{OUT}$  is used, the reference is automatically stepped slower to avoid excessive input current draw.

#### **Boost (BST) Mode**

This is a normal operating mode of the regulator.

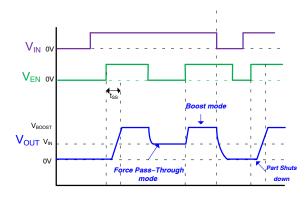

#### Pass-Through Mode

The device allows the user to force the device in Forced Pass–Through Mode through the EN pin. If the EN pin is pulled HIGH, the device starts operating in Boost Mode. Once the EN pin is pulled LOW, the device is forced into Pass–Through Mode. To disable the device, the input supply voltage must be removed. The device cannot startup in Forced Pass–Through Mode (see Figure 18). During startup, keep the EN pulled HIGH for at least 350 µs before pulling it LOW in order to make sure that the device enters Pass–Through Mode reliably.

In normal operation, the device automatically transitions from Boost Mode to Pass–Through Mode if VIN goes above the target  $V_{OUT}$ . In Pass–Through Mode, the device fully enhances Q2 to provide a very low impedance path from VIN to VOUT. Entry to the Pass–Through Mode is triggered by condition where  $V_{IN} > V_{OUT}$  and no switching has occurred during the past 5  $\mu$ s. To soften the entry into Pass–Through Mode, Q2 is driven as a linear current source for the first 5  $\mu$ s. Pass–Through Mode exit is triggered when  $V_{OUT}$  reaches the target  $V_{OUT}$  voltage. During Automatic Pass–Through Mode, the device is short–circuit protected by a voltage comparator tracking the voltage drop from  $V_{IN}$  to  $V_{OUT}$ ; if the drop exceeds 300 mV, a fault is declared.

Figure 18. Pass-Through Profile

#### **Current Limit Protection**

The FAN48615 has valley current limit protection in case of overload situations. The valley current limit will prevent high current from causing damage to the IC and the inductor. The current limit is halved during soft–start.

When starting into a fault condition, the input current will be limited by LIN1 and LIN2 current threshold.

#### **Fault State**

The regulator enters Fault State under any of the following conditions:

- V<sub>OUT</sub> fails to achieve the voltage required to advance from LIN Mode to SS Mode.

- V<sub>OUT</sub> fails to achieve the voltage required to advance from SS Mode to BST Mode.

- Boost current limit triggers for 2 ms during BST Mode.

- V<sub>IN</sub> V<sub>OUT</sub> > 300 mV; this fault can occur only after successful completion of the soft–start sequence.

- $V_{IN} < V_{UVLO}$

Once a fault is triggered, the regulator stops switching and presents a high-impedance path between VIN and VOUT. After waiting 20 ms, an automatic restart is attempted.

#### Over-Temperature

The regulator shuts down if the die temperature exceeds 150°C and restarts when the IC cools by ~20°C.

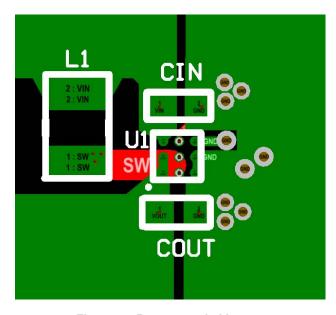

## **Layout Recommendation**

The layout recommendations below highlight various top-copper pours by using different colors.

To minimize spikes at VOUT, COUT must be placed as close as possible to PGND and VOUT, as shown in Figure 19.

For best thermal performance, maximize the pour area for all planes other than SW. The ground pour, especially, should fill all available PCB surface area and be tied to internal layers with a cluster of thermal vias.

Figure 19. Recommended Layout

## Table 9. PRODUCT-SPECIFIC PACKAGE DIMENSIONS

The following information applies to the WLCSP package dimensions on the next page.

| Product       | D (mm)            | E (mm)            | X (mm) | Y (mm) |

|---------------|-------------------|-------------------|--------|--------|

| FAN48615UC08X | $1.215 \pm 0.030$ | $1.215 \pm 0.030$ | 0.2075 | 0.2075 |

All other brand names and product names appearing in this document are registered trademarks or trademarks of their respective holders.

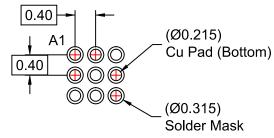

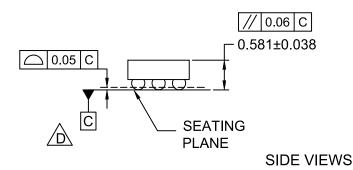

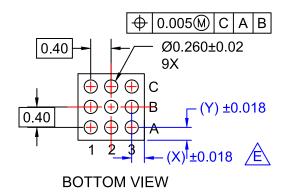

#### WLCSP9 1.215x1.215x0.581 CASE 567QW ISSUE O

**DATE 31 OCT 2016**

RECOMMENDED LAND PATTERN (NSMD PAD TYPE)

#### **NOTES**

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCE PER A ASME Y14.5M, 2009.

D DATUM C IS DEFINED BY THE

SPHERICAL CROWNS OF THE BALLS.

E. FOR DIMENSIONS D,E,X, AND Y SEE PRODUCT DATASHEET.

| DOCUMENT NUMBER: | 98AON13355G               | Electronic versions are uncontraccessed directly from the Document   | •           |

|------------------|---------------------------|----------------------------------------------------------------------|-------------|

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document versions are uncontrolled except |             |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                            |             |

| DESCRIPTION:     | WLCSP9 1.215x1.215x0.581  |                                                                      | PAGE 1 OF 2 |

**DOCUMENT NUMBER:** 98AON13355G

PAGE 2 OF 2

| ISSUE | REVISION                                                                                | DATE        |

|-------|-----------------------------------------------------------------------------------------|-------------|

| 0     | RELEASED FOR PRODUCTION FROM FAIRCHILD UC009AK TO ON SEMICONDUCTOR. REQ. BY F. ESTRADA. | 31 OCT 2016 |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

|       |                                                                                         |             |

ON Semiconductor and una are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. anising out of the application of use of any product of circuit, and specifically disclaims any and an inability, including without infiniation special, consequential of inclental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates. and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

© Semiconductor Components Industries, LLC, 2016 Case Outline Number: October, 2016 - Rev. O 567QW

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative