# FAN6208 Secondary-Side Synchronous Rectifier Controller for LLC Topology

#### Features

FAIRCHILD SEMICONDUCTOR

- Specialized SR Controller for LLC or LC Resonant Converters

- Secondary-Side Timing Detection with Timing Estimator

- Gate-Shrink Function to Prevent Shoot-Through During Load and Line Transient

- Green-Mode Function for Higher Efficiency at Light-Load Condition

- Programmable Dead Time between Primary-Side Gate Drive Signal and SR Drive Signal

- Advanced Output-Short / Overload Protection Based on the Feedback Information

- Internal Over-Temperature Protection (OTP)

- V<sub>DD</sub> Pin Over-Voltage Protection (OVP)

# Description

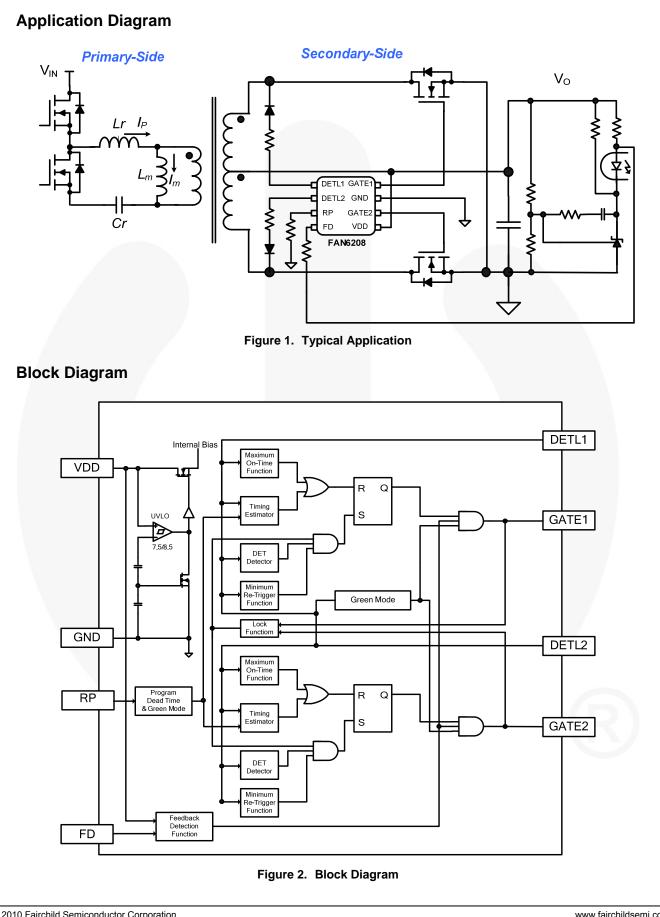

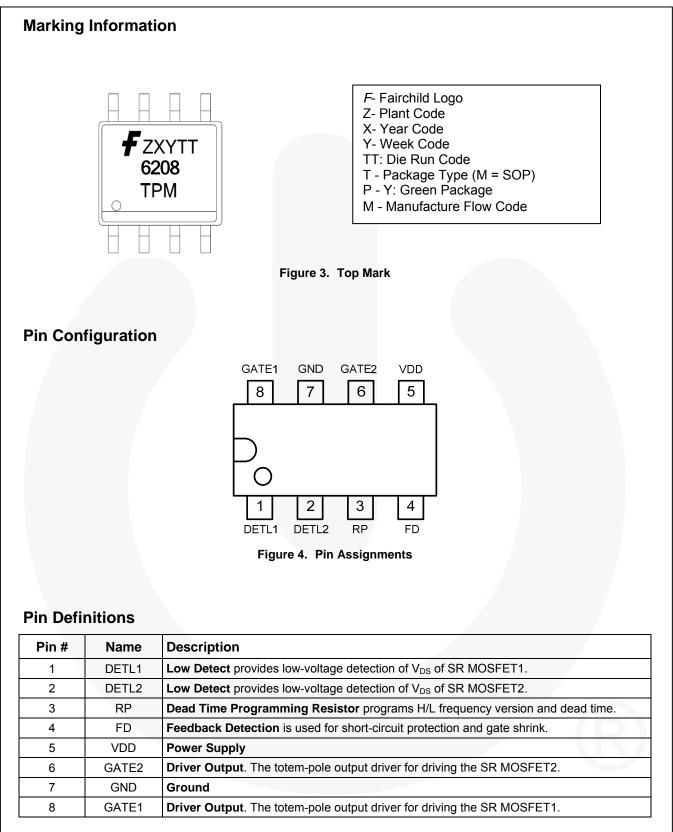

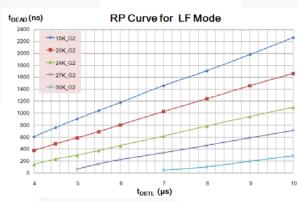

FAN6208 is a synchronous rectification (SR) controller for isolated LLC or LC resonant converters that can drive two individual SR MOSFETs emulating the behavior of rectifier diodes. FAN6208 measures the SR conduction time of each switching cycle by monitoring the drain-to-source voltage of each SR and determines the optimal timing of the SR gate drive. FAN6208 uses the change of opto-coupler diode current to adaptively shrink the duration of SR gate drive signals during load transients to prevent shoot-through. To improve lightload efficiency, Green-Mode operation is employed, which disables the SR drive signals, minimizing gate drive power consumption at light-load condition.

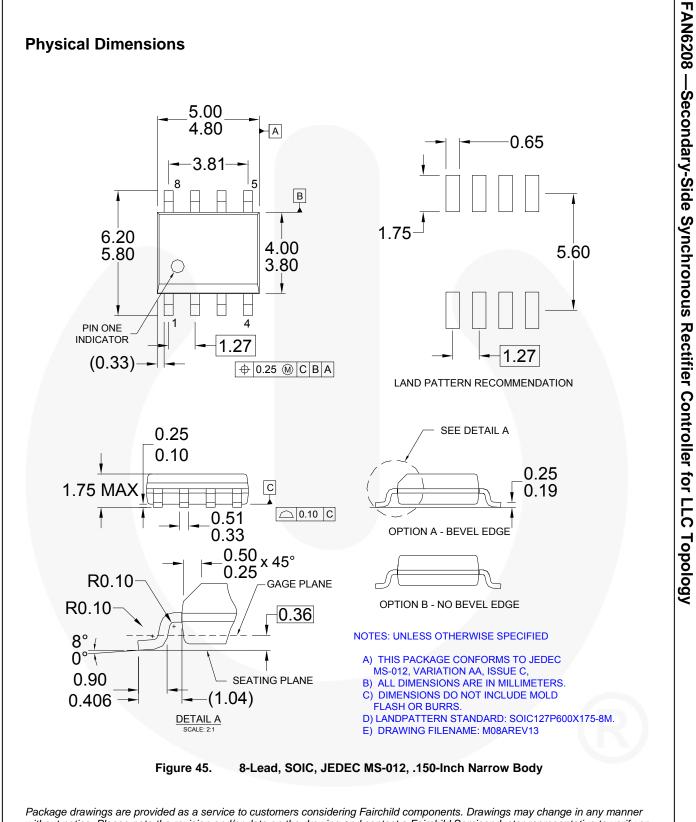

Optimal timing circuits and protection functions are integrated in an 8-pin SOP package, which allows highefficiency power supply design with fewer components.

#### **Related Resources**

<u>Evaluation Board: FEBFAN6208\_CP433v1</u>

# Applications

- LCD TV

- PC Power

- Open-Frame SMPS

## **Ordering Information**

| Part Number Operating Temperature Range |                 | Package                           | Packing Method |  |

|-----------------------------------------|-----------------|-----------------------------------|----------------|--|

| FAN6208MY                               | -40°C to +105°C | 8-Pin Small Outline Package (SOP) | Tape & Reel    |  |

**Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                           | Min.                             | Max.                              | Unit |

|------------------|-----------------------------------------------------|----------------------------------|-----------------------------------|------|

| V <sub>DD</sub>  | Supply Voltage                                      |                                  | 30                                | V    |

| V <sub>FD</sub>  | Voltage on FD Pin                                   |                                  | 30                                | V    |

| V <sub>LV</sub>  | Voltage on DETL1, DETL2, RP Pins                    | -0.3                             | 7.0                               | V    |

| PD               | Power Dissipation                                   | 350Mw<br>at T <sub>A</sub> =90°C | 1000mW<br>at T <sub>A</sub> =25°C |      |

| Θ <sub>JA</sub>  | Junction-to-Ambient Thermal Resistance              |                                  | 130                               | °C/W |

| $\Psi_{JT}$      | Junction-to-Top Thermal Characteristics             |                                  | 45                                | °C/W |

| TJ               | Operating Junction Temperature                      | -40                              | +125                              | °C   |

| T <sub>STG</sub> | Storage Temperature Range                           | -55                              | +150                              | °C   |

| TL               | Lead Temperature (Wave Soldering or IR, 10 Seconds) |                                  | +260                              | °C   |

| TL               | Human Body Model, JESD22-A114                       |                                  | 6                                 | kV   |

| ESD              | Charged Device Model, JESD22-C101                   |                                  | 2                                 | κV   |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| ; | Symbol         | Parameter                     | Min. | Max. | Unit |

|---|----------------|-------------------------------|------|------|------|

|   | T <sub>A</sub> | Operating Ambient Temperature | -40  | +105 | °C   |

# **Electrical Characteristics**

V<sub>DD</sub>=20V, T<sub>A</sub>=25°C, unless otherwise specified. All voltages are with respect to GND unless otherwise noted.

| Symbol                                                     | Parameter                                                                   | Conditions                                                                       | Min.                | Тур. | Max. | Units |

|------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------|------|------|-------|

| VDD Section                                                |                                                                             |                                                                                  |                     |      |      |       |

| V <sub>DD</sub>                                            | DC Supply Voltage                                                           |                                                                                  | $V_{\text{TH-OFF}}$ |      | 28   | V     |

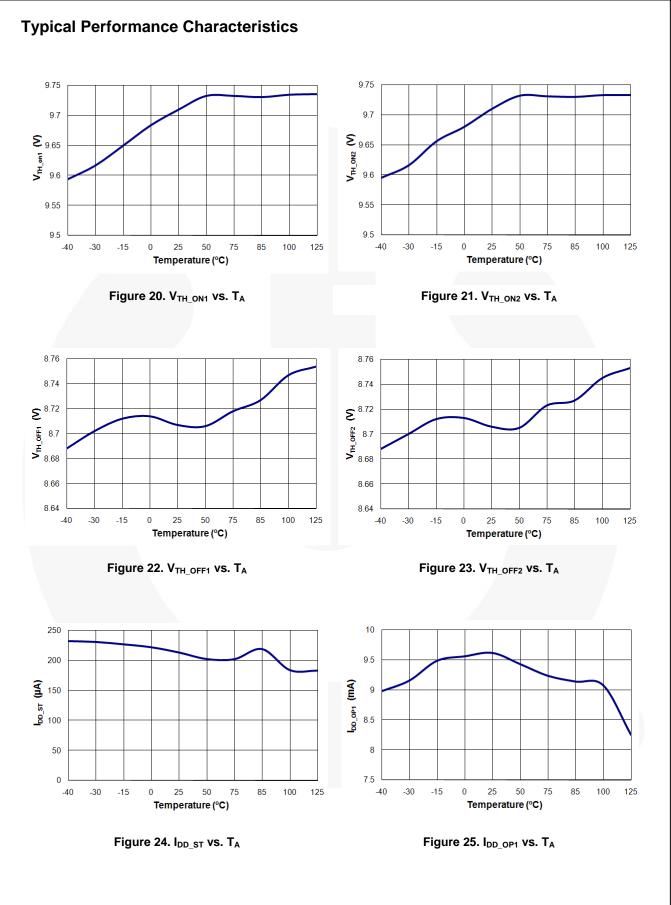

| I <sub>DD-OP1</sub>                                        | Operating Current                                                           | $V_{DD}$ =12V, DETL=50KHz,<br>C <sub>L</sub> =6nF, R <sub>RP</sub> =24K ·        | 7.0                 | 8.5  | 10.0 | mA    |

| I <sub>DD-OP2</sub>                                        | Operating Current                                                           | V <sub>DD</sub> =12V, DETL=100KHz                                                | 2.4                 | 3.2  | 4.0  | mA    |

| I <sub>DD-ST</sub>                                         | Startup Current                                                             | V <sub>DD</sub> =8V                                                              | 180                 | 300  | 500  | μA    |

| V <sub>TH-ON1</sub> V <sub>TH-ON2</sub>                    | On Threshold Voltage                                                        |                                                                                  | 9.3                 | 9.7  | 10.1 | V     |

| V <sub>TH-OFF1</sub><br>V <sub>TH-OFF2</sub>               | Off Threshold Voltage                                                       |                                                                                  | 8.3                 | 8.8  | 9.3  | V     |

| V <sub>DD-OVP1</sub><br>V <sub>DD-OVP2</sub>               | V <sub>CC</sub> Over-Voltage<br>Protection                                  |                                                                                  | 26                  | 27   | 28   | V     |

| V <sub>DD-OVP-HYS1</sub><br>V <sub>DD-OVP-HYS2</sub>       | V <sub>CC</sub> Over-Voltage<br>Protection Hysteresis                       |                                                                                  | 1.3                 | 1.8  | 2.3  | V     |

| tovp1,tovp2                                                | V <sub>CC</sub> Over-Voltage-<br>Protection Debounce                        |                                                                                  | 30                  | 60   | 100  | μs    |

| DETL Section                                               |                                                                             |                                                                                  |                     |      |      |       |

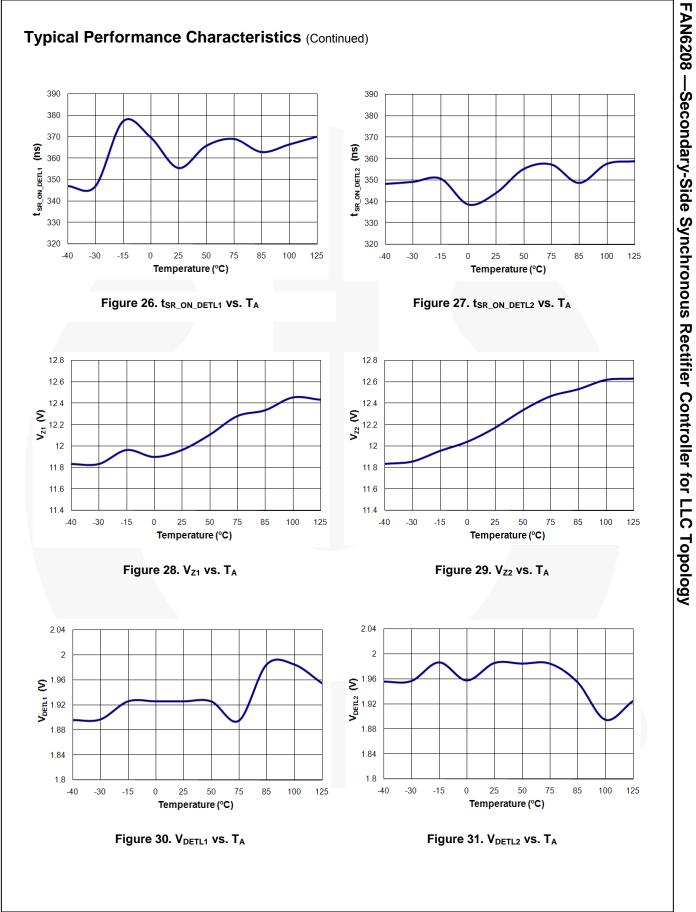

| V <sub>detl1</sub><br>V <sub>detl2</sub>                   | Threshold Voltage for LOW<br>Detection of DETL                              | $V_{DD}$ =12V, DETL=50KHz,<br>C <sub>L</sub> =6nF, R <sub>RP</sub> =24K $\Omega$ | 1.7                 | 2.0  | 2.3  | V     |

| tsr-on-detl1<br>tsr-on-detl2                               | Delay from DETL LOW to SR Gate Turn-On                                      | t <sub>DB</sub> + t <sub>PD</sub> + t <sub>R</sub>                               | 300                 | 350  | 400  | ns    |

| V <sub>DETL-FLOATING1</sub><br>V <sub>DETL-FLOATING2</sub> | DETL Floating Voltage                                                       | V <sub>DD</sub> =12V, DETL Pin<br>Floating                                       | 4.5                 |      |      | V     |

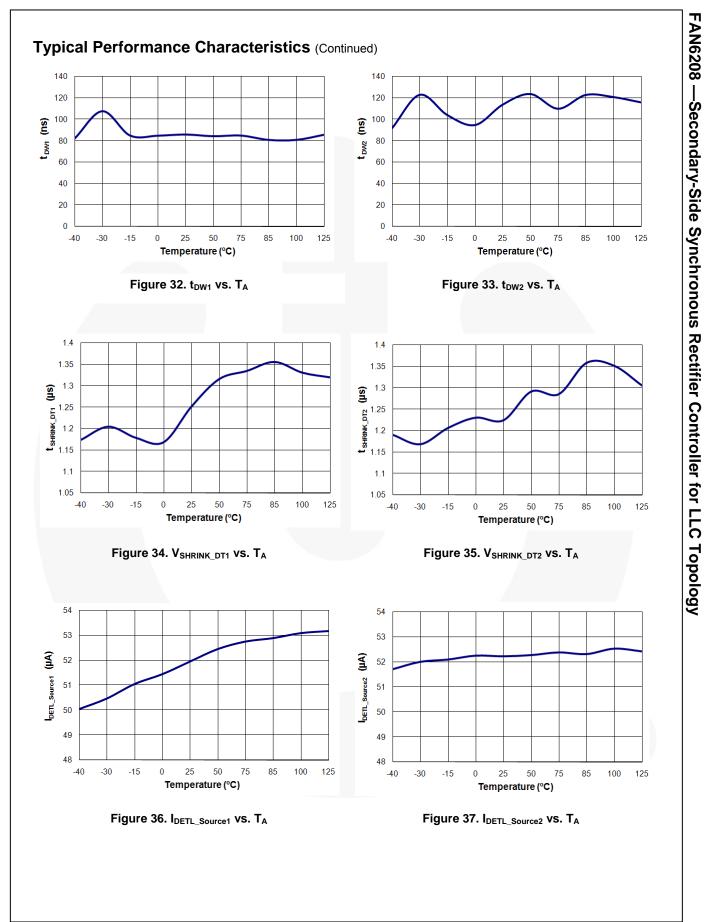

| I <sub>DETL-SOURCE1</sub>                                  | DETL Source Current                                                         | V <sub>DETL1</sub> =0V                                                           | 40                  | 50   | 60   | μA    |

| tDETL_Green_LF1<br>tDETL_Green_LF2                         | DETL LOW Time<br>Threshold for Green Mode<br>at Low-Frequency<br>Operation  | V <sub>RP</sub> < 1.5V                                                           | 3.50                | 3.75 | 4.00 | μs    |

| tDET(L)_Green_HF1<br>tDET(L)_Green_HF2                     | DETL LOW Time<br>Threshold for Green Mode<br>at High-Frequency<br>Operation | V <sub>RP</sub> > 1.5V                                                           | 1.75                | 1.90 | 2.05 | μs    |

| Thermal Shutd                                              | own                                                                         |                                                                                  |                     |      |      |       |

| T <sub>SHUTDOWN</sub>                                      | Shutdown Temperature                                                        | Temperature Rising, $V_{DD}$ =15V                                                |                     | 140  |      |       |

|                                                            | Hysteresis                                                                  |                                                                                  |                     | 20   |      | °C    |

| TSTARTUP                                                   | Startup Temperature                                                         | Before Startup                                                                   |                     | 120  |      |       |

Continued on the following page...

$V_{DD}$ =20V,  $T_A$ =25°C, unless otherwise specified. All voltages are with respect to GND unless otherwise noted.

| Symbol                                               | Parameter                                                                              | Conditions                                                        | Min. | Тур. | Max. | Units |

|------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|------|------|-------|

| Gate Section                                         |                                                                                        | I                                                                 | 1    | 1    |      | 1     |

| $V_{Z1}V_{Z2}$                                       | Gate Output Voltage<br>Maximum (Clamping)                                              | V <sub>DD</sub> =20V                                              | 10   | 12   | 14   | V     |

| $V_{OL1}V_{OL2}$                                     | Gate Output Voltage LOW                                                                | V <sub>DD</sub> =12V; I <sub>O</sub> =100mA                       |      |      | 0.5  | V     |

| $V_{OH1}V_{OH2}$                                     | Gate Output Voltage HIGH                                                               | V <sub>DD</sub> =12V; I <sub>O</sub> =100mA                       | 9    |      |      | V     |

| t <sub>R1</sub> t <sub>R2</sub>                      | Rising Time                                                                            | $V_{DD}$ =12V; C <sub>L</sub> =6nF;<br>$V_{GATE}$ =2V to 9V       | 30   | 70   | 120  | ns    |

| $t_{F1} t_{F2}$                                      | Falling Time                                                                           | $V_{DD}$ =12V; C <sub>L</sub> =6nF;<br>$V_{GATE}$ =9V to 2V       | 30   | 50   | 70   | ns    |

| tpd_high_detl1<br>tpd_high_detl2                     | Propagation Delay to Gate<br>Output HIGH (DETL<br>Trigger)                             | t <sub>R</sub> : 0V~2V, V <sub>DD</sub> =12V<br>(DET Floating)    |      | 120  |      | ns    |

| tpd_low_detl1<br>tpd_low_detl2                       | Propagation Delay to Gate<br>Output LOW (DETL<br>Trigger)                              | t <sub>F</sub> : 100%∼90%, V <sub>DD</sub> =12V<br>(DET Floating) |      | 120  |      | ns    |

| t <sub>on_max1</sub><br>t <sub>on_max2</sub>         | Maximum On-Time                                                                        | Trim Maximum On-Time                                              | 9.0  | 10.5 | 12.0 | μs    |

| t <sub>INHIBIT_LF1</sub><br>t <sub>INHIBIT_LF2</sub> | Gate Inhibit Time (from Turn-Off to Next Turn-On)                                      | V <sub>RP</sub> < 1.5V                                            | 1.8  | 2.1  | 2.5  | μs    |

| t <sub>INHIBIT_HF1</sub><br>t <sub>INHIBIT_HF2</sub> | Gate Inhibit Time (from Turn-Off to Next Turn-On)                                      | V <sub>RP</sub> > 1.5V                                            | 1.25 | 1.45 | 1.70 | μs    |

| t <sub>blanking1</sub><br>t <sub>blanking2</sub>     | Blanking Time for SR Turn-<br>Off Triggered by DETL<br>High (Minimum On-Time)          |                                                                   |      | 300  |      | ns    |

| K <sub>R</sub>                                       | Gate ON-Time Increase<br>Rate Between Two<br>Consecutive Cycles                        | t <sub>on</sub> (n) / t <sub>on</sub> (n-1) %                     |      | 140  |      | %     |

| Timing Estimat                                       | tor Section                                                                            |                                                                   | •    |      | •    |       |

| tow                                                  | Detection Window for<br>Insufficient Dead Time<br>(from Gate Turn-Off to<br>DETL HIGH) |                                                                   | 80   | 125  | 150  | ns    |

| t <sub>shrink-dt</sub>                               | Gate Shrink Time by<br>Insufficienct Dead Time                                         | R <sub>RP</sub> =20KΩ, t <sub>DETL</sub> =5µs                     | 1.00 | 1.25 | 1.50 | μs    |

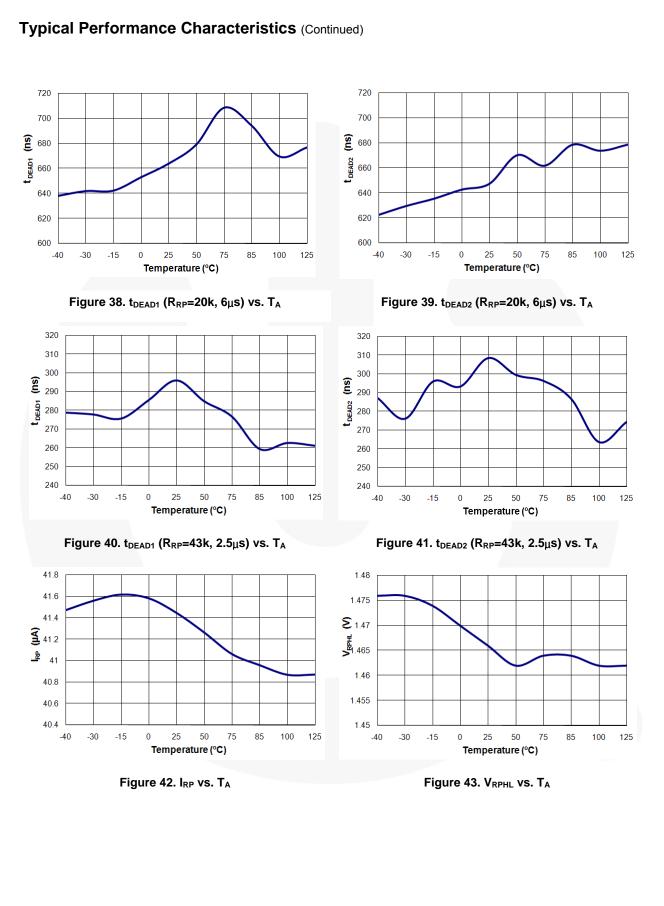

|                                                      | Dead Time by Timing<br>Estimator (70kHz ~<br>140kHz, V <sub>RP</sub> < 1.5V)           | t <sub>DETL</sub> =4μs, R <sub>RP</sub> =20KΩ                     | 210  | 300  | 390  |       |

|                                                      |                                                                                        | t <sub>DETL</sub> =6μs, R <sub>RP</sub> =20KΩ                     | 570  | 720  | 870  |       |

| t <sub>DEAD</sub>                                    | Dead Time by Timing                                                                    | t <sub>DETL</sub> =2.5μs, R <sub>RP</sub> =43KΩ                   | 220  | 320  | 420  | ns    |

|                                                      | Estimator (160kHz ~<br>240kHz, V <sub>RP</sub> > 1.5V)                                 | t <sub>DETL</sub> =3.8μs, R <sub>RP</sub> =43KΩ                   | 560  | 670  | 780  | K     |

| t <sub>DB</sub>                                      | DETL HIGH-to-LOW<br>Debounce Time for Gate<br>Turn-on Trigger                          |                                                                   |      | 150  |      | ns    |

| t <sub>shrink-rng</sub>                              | Gate Shrink by DETL<br>Ringing around Zero                                             |                                                                   |      | 1.2  |      | μs    |

| $t_{Green_{DH}}$                                     | DETL Pull-HIGH Time<br>Threshold for Green Mode                                        |                                                                   | 18   | 24   | 30   | μs    |

Continued on the following page...

www.fairchildsemi.com

FAN6208 —Secondary-Side Synchronous Rectifier Controller for LLC Topology

# **Electrical Characteristics**

$V_{DD}$ =20V,  $T_A$ =25°C, unless otherwise specified. All voltages are with respect to GND unless otherwise noted.

| Symbol                               | Parameter                                                            | Conditions                                  | Min. | Тур. | Max. | Units |

|--------------------------------------|----------------------------------------------------------------------|---------------------------------------------|------|------|------|-------|

| Feedback Dete                        | ection (FD) Section                                                  |                                             |      |      |      |       |

| ΔV1% ΔV2%                            | Feedback Increase<br>Threshold for Gate Shrink                       | $[(V_{DD}-V_{FD})_{n+1}/(V_{DD}-V_{FD})_n]$ |      | 120  |      | %     |

| t <sub>shrink-fd</sub>               | Gate Shrink by Feedback Detection                                    |                                             |      | 1.4  |      | μs    |

| t <sub>D-SHRINK-FD</sub>             | Gate-Shrink Duration by<br>Feedback Detection                        |                                             | 60   | 90   | 120  | μs    |

| V <sub>DD</sub> -V <sub>FD.SCP</sub> | Short-Circuit Protection<br>(SCP) Threshold by<br>Feedback Detection |                                             | 200  | 270  | 340  | mV    |

| t <sub>DB-SCP</sub>                  | Debounce Time for Short-<br>Circuit Protection (SCP)                 |                                             | 12   | 16   | 20   | μs    |

| RP Section                           |                                                                      |                                             |      |      |      |       |

| I <sub>RP</sub>                      | RP Source Current                                                    |                                             | 38.5 | 41.5 | 44.5 | μA    |

| V <sub>RPO</sub>                     | RP Open Protect                                                      |                                             | 3.40 | 3.65 | 3.90 | V     |

| V <sub>RPS</sub>                     | RP Short Protect                                                     |                                             | 0.25 | 0.30 | 0.35 | V     |

| t <sub>RPOS</sub>                    | RP Open/Short Debounce                                               |                                             | 1.6  | 2.0  | 2.4  | μs    |

| V <sub>RPHL</sub>                    | H/L Frequency Threshold                                              |                                             | 1.40 | 1.46 | 1.52 | V     |

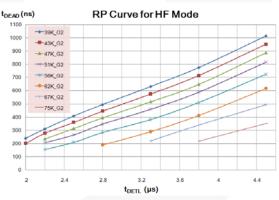

Figure 5. tDEAD vs. tDETL RP Curve for LF Mode

# **Function Description**

#### **Operation Principle**

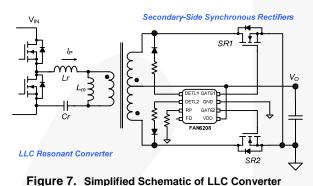

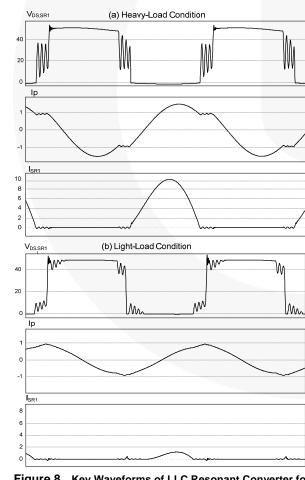

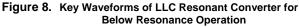

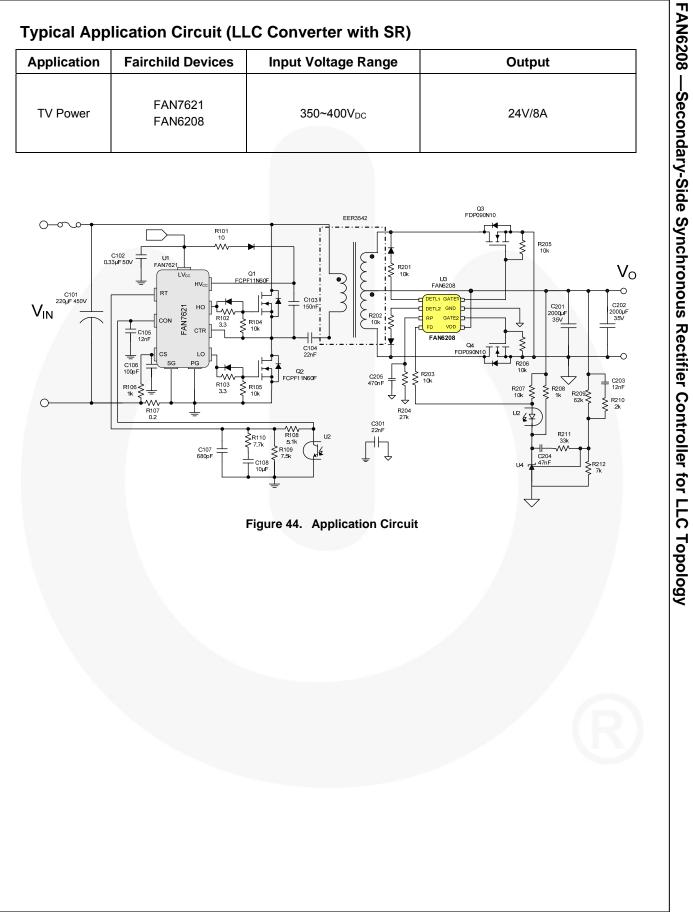

FAN6208 is a secondary-side synchronous rectifier controller for LLC or LC resonant converters that drive two synchronous rectifier MOSFETs. Figure 7 is the simplified circuit diagram of an LLC converter. The FAN6208 determines SR MOSFET turn-on/off timing by detecting the drain-to-source voltage of each SR MOSFET. The key waveforms for LLC resonant converter for below resonance and above resonance are shown in Figure 8 and Figure 9, respectively.

Figure 9. Key Waveforms of LLC Resonant Converter for Above Resonance Operation

## **Timing Estimator**

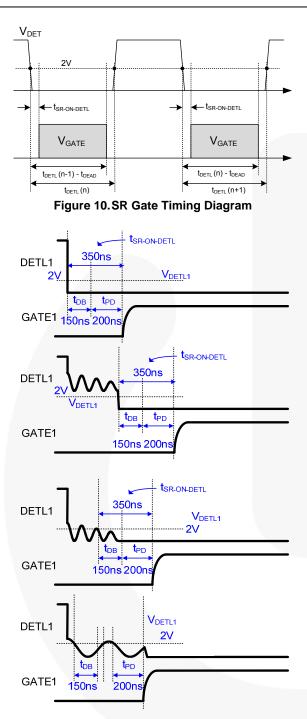

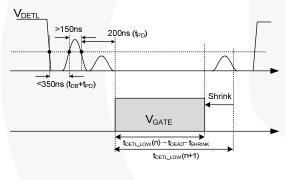

Figure 10 shows the timing diagram for FAN6208. Once the body diode of SR begins conducting, the drain-to-source voltage drops to zero, which causes DETL pin voltage to drop to zero. FAN6208 turns on the MOSFET after  $t_{ON-ON-DETL}$  (about 350ns), when voltage on DETL drops below 2V. As depicted in Figure 11, the turn-on delay (after  $t_{SR-ON-DETL}$ ) is the sum of debounce time (150ns) and propagation delay (200ns).

FAN6208 measures the SR conduction duration ( $t_{DETL}$ ), during which DETL stays lower than 2V, and uses this information to determine the turn-off instant of SR gates of the next switching cycle. The turn-off timing is obtained by subtracting a dead time ( $t_{DEAD}$ ) from the measured SR conduction duration of the previous switching cycle. The dead time can be programmed using a resistor on the RP pin and the relationship between the dead time and SR conduction duration ( $t_{DETL}$ ) for different resistor values on RP pin is given in Figure 5.

Figure 11.DETL Debounce (Blanking) Time

#### **Gate-Shrink Functions**

In normal operation, the turn-off instant is determined by subtracting a dead time ( $t_{DEAD}$ ) from the measured SR conduction duration of the previous switching cycle, as shown in Figure 10. This allows proper driving timing for SR MOSFETS when the converter is in steady state and the switching frequency does not change much. However, this control method may cause shoot-through of SR MOSFETs when the switching frequency increases fast and switching transition of the primary-

side MOSFETs takes place before the turn-off command of SR is given. To prevent the shoot-through, FAN6208 has gate-shrink functions. Gate shrink occurs under three conditions:

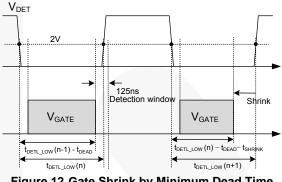

(a) When insufficient dead time is detected in the previous switching cycle. When the DETL goes HIGH within 125ns of detection window after SR gate is turned off, the SR gate drive signal in the next switching cycle is reduced by t<sub>SHRINK-DT</sub> (about 1.25μs) to increase the dead time, as shown in Figure 12.

Figure 12. Gate Shrink by Minimum Dead Time Detection Window

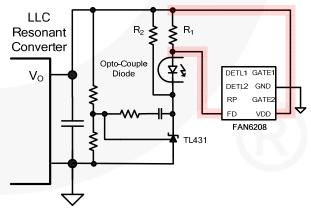

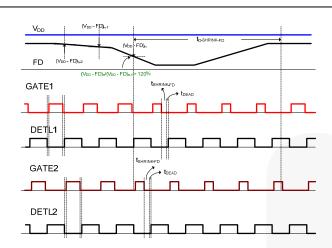

(b) When the feedback information changes fast. FAN6208 monitors the current through the optocoupler diode by measuring the voltage across the resistor in series with the opto-coupler diode, as depicted in Figure 13. If the feedback current through the opto-coupler diode increases by more than 20% of the feedback current of the previous switching cycle, the SR gate signal is shrunk by t<sub>SHRINK-FD</sub> (about 1.4µs) for t<sub>D-SHRINK-FD</sub> (about 90µs), as shown in Figure 14.

Figure 13. Typical Application Circuit

Figure 14. Gate Shrink by Feedback Detection

(c) When the DETL voltage has ringing around zero. As depicted in Figure 8, the drain voltage of SR has ringing around zero at light-load condition after the switching transition of the primary-side switches. When DETL voltage rises above 2V within 350ns after DETL voltage drops to zero and stays above 2V longer than 150ns, the gate is shrunk by 1.2µs (t<sub>SHRINK-RNG</sub>), as shown in Figure 15.

Figure 15. Gate Shrink by DETL Voltage Ringing Around Zero

#### **RP Pin Function**

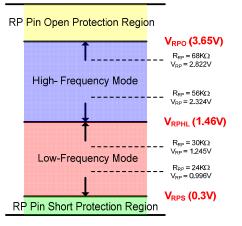

The RP pin programs the level of green mode and  $t_{DEAD}$ . Figure 16 shows how the mode is selected by the voltage on the RP pin (open protection, short protection, and HF/LF mode). When  $R_{RP}$  is less than 36K $\Omega$ , FAN6208 operates in low-frequency mode. Green mode is enabled when  $t_{DETL}$  is smaller than 3.75µs. When  $R_{RP}$  is larger than 36K $\Omega$ , high-frequency mode is selected and green mode is enabled for  $t_{DETL} < 1.90$ µs.  $t_{DEAD}$  can be also adjusted by a resistor on the RP pin. Figure 5 shows the relationship between  $t_{DEAD}$  and  $t_{DETL}$  for different RP resistors.

Figure 16. RP Pin Operation

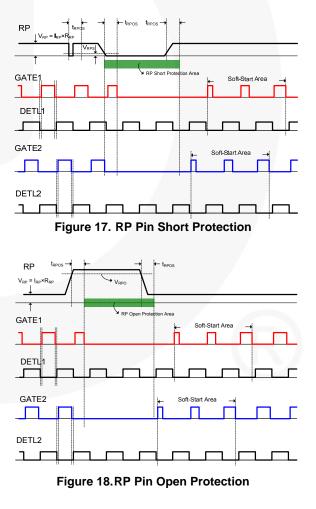

To handle abnormal conditions for IC pins, the RP pin also provides open/short protection. When V<sub>RP</sub> is less than V<sub>RPS</sub> (0.3V) or V<sub>RP</sub> is higher than V<sub>RPO</sub> (3.65V), the protection is triggered. Figure 17 shows the RP pin short protection timing sequence. If V<sub>RP</sub> < V<sub>RPS</sub> (0.3V) for longer than t<sub>RPOS</sub> (2µs), FAN6208 is disabled. Figure 18 shows the RP pin open protection timing sequence. If V<sub>RP</sub> > V<sub>RPO</sub> (3.65V) for longer than t<sub>RPOS</sub> (2µs), FAN6208 is disabled.

### **Green Mode**

Switching frequency increases in LLC topology at lightload condition, which increases the power consumption for the SR gate drive. Green mode reduces power loss at light load. FAN6208 has two ways to enable green mode. Green mode is triggered when DETL voltage is pulled LOW for less than 3.75µs (LF mode) or 1.90µs (HF mode) for seven switching cycles. FAN6208 resumes normal SR gate driving when DETL voltage is pulled LOW for longer than 3.75µs (LF mode) or 1.90µs (HF mode) for seven switching cycles.

When DETL voltage is pulled HIGH for longer than 24µs. This occurs when the LLC resonant converter operates in burst mode (skipping mode).

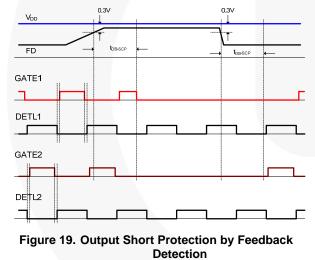

### **Short-Circuit Protection**

As depicted in Figure 13, FAN6208 monitors the current through the opto-coupler diode by measuring the voltage across the resistor in series with the opto-coupler diode. When the output of the power supply is short circuited, the output voltage drops and the cathode of the shunt regulator (KA431) is saturated to HIGH. No current flows through the opto coupler diode. The output short protection is triggered when the voltage between V<sub>DD</sub> and FD is smaller than 0.3V, as shown in Figure 19.

# **V**<sub>DD</sub> Pin Over-Voltage Protection

Over-voltage conditions are usually caused by an open feedback loop.  $V_{DD}$  over-voltage protection prevents damage of SR MOSFET. When the voltage on the  $V_{DD}$  pin exceeds 27V, FAN6208 disables gate output.

#### **Internal Over-Temperature Protection**

Internal over-temperature protection prevents the SR gate from fault triggering in high temperatures. If the temperature is over 140°C, the SR gate is disabled until the temperature drops below 120°C.

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

Т