### PRELIMINARY

# National Semiconductor

# GAL20RA10-15, -20, -25 Generic Array Logic

### **General Description**

The NSC E<sup>2</sup>CMOS<sup>TM</sup> GAL<sup>®</sup> device combines a high performance CMOS process with electrically erasable floating gate technology. This programmable memory technology applied to array logic provides designers with reconfigurable logic and bipolar performance at significantly reduced power levels.

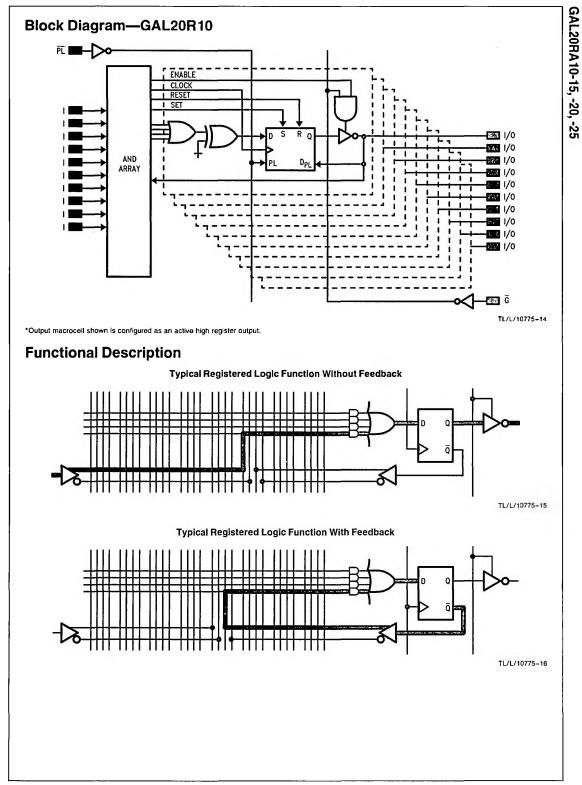

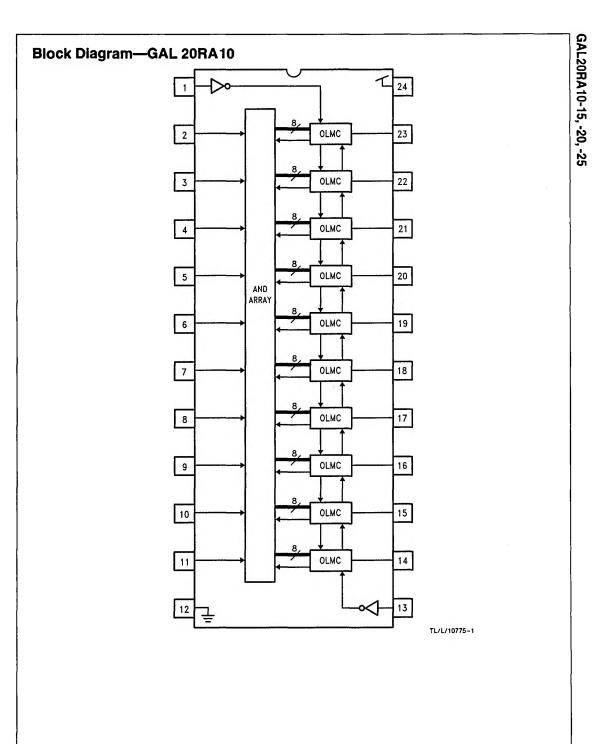

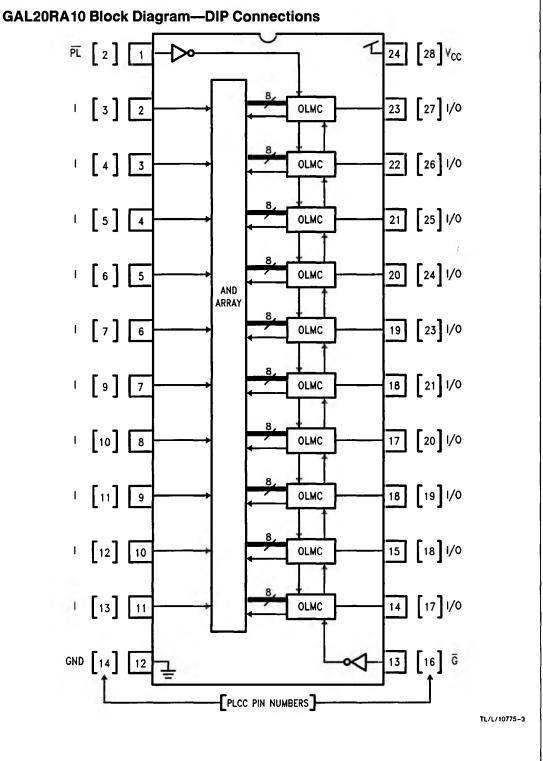

The GAL20RA10 is made up of ten Output Logic Macro Cells (OLMC). Four programmable AND array outputs feed into the fixed OR-gate for each OLMC to generate the device's output functions. Four other AND array outputs are used for control functions in the OLMC. With a robust mixture of logic derived controlled functions and selectable output data paths, the GAL20RA10 provides an ideal solution for registered random logic applications.

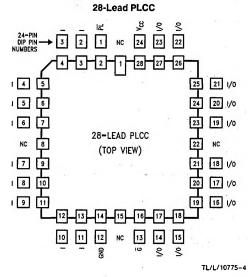

This device is housed in a 24-pin 300 mil DIP. A 28-pin PCC package is also available. It can be programmed by most PAL programmers.

Programming is accomplished using industry standard available hardware and software tools. NSC guarantees a minimum 100 erase/write cycles.

Unique test circuitry and reprogrammable cells allow complete AC, DC, cell and functionality testing during manufacture. Therefore, NSC guarantees 100% field programmability of the GAL devices. In addition, electronic signature is available to provide positive device ID. A security circuit is built-in, providing proprietary designs with copy protection.

### Features

- High performance E<sup>2</sup>CMOS technology

- 15 ns maximum propagation delay

- $-f_{CLK} = 40 \text{ MHz}$

- 15 ns maximum from clock input to data output

- TTL compatible 16 mA outputs

- UltraMOS® III advanced CMOS technology

- Electrically erasable cell technology

- Reconfigurable logic

- Reprogrammable cells

- 100% tested/guaranteed 100% yields

- High speed electrical erasure (<50 ms)

- 20 year data retention

- 10 output logic macrocells

- Maximum flexibility for complex logic designs

- Programmable output polarity

- Programmable asynchronous set and reset

- Individually programmable clocks

- Programmable and dedicated pin control of output TRI-STATE®

- Programmable Register bypass

- TTL level Register preload

- Power-up reset for registered outputs

- JEDEC-compatible programming equipment and development software available

- Preload and power-up reset of all registers — 100% functional testability

- Full supported development software

- Electronic signature for identification

- Security fuse prevents direct copying of logic patterns

- JEDEC map identicle to Bipolar PAL versions

### Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> ) | -0.5V to +7.0V                  |

|-----------------------------------|---------------------------------|

| Input Voltage (Note 2)            | -2.5V to V <sub>CC</sub> + 1.0V |

| Off-State Output Voltage (Note 2) | -2.5V to V <sub>CC</sub> + 1.0V |

| Output Current                    | ± 100 mA                        |

| Storage Temperature               | -65°C to +150°C                 |

| Ambient Temperature with                |                 |

|-----------------------------------------|-----------------|

| Power Applied                           | 65°C to +125°C  |

| Junction Temperature                    | -65°C to +150°C |

| Lead Temperature (Soldering, 10 seconds | s) 260°C        |

| ESD Tolerance                           | TBD             |

| C <sub>ZAP</sub> = 100 pF               |                 |

| $R_{ZAP} = 1500\Omega$                  |                 |

| Test Method: Human Body Model           |                 |

| Test Specification: NSC SOP-5-028       |                 |

# **Recommended Operating Conditions**

### SUPPLY VOLTAGE AND TEMPERATURE

| Symbol          | DI Parameter Commercial        |      | lai | Industrial |     |     | Military |     |     | Units |       |  |

|-----------------|--------------------------------|------|-----|------------|-----|-----|----------|-----|-----|-------|-------|--|

| Symbol          | Farameter                      | Min  | Тур | Max        | Min | Тур | Max      | Min | Тур | Max   | Units |  |

| V <sub>CC</sub> | Supply Voltage                 | 4.75 | 5   | 5.25       | 4.5 | 5   | 5.5      | 4.5 | 5   | 5.5   | v     |  |

| TA              | Operating Free-Air Temperature | 0    | 25  | 75         | -40 | 25  | 85       | -55 | 25  |       | °C    |  |

| T <sub>C</sub>  | Operating Case Temperature     |      |     |            |     |     |          |     |     | 125   | °C    |  |

#### AC TIMING REQUIREMENTS

|                    |                                                |                            | GAL20 | RA10-15 | GAL20RA10-20 |         | GAL20RA 10-25 |     |     |

|--------------------|------------------------------------------------|----------------------------|-------|---------|--------------|---------|---------------|-----|-----|

| Symbol             | Para                                           | Parameter                  |       | COM     |              | COM/IND |               | MIL |     |

|                    |                                                |                            | Min   | Max     | Min          | Max     | Min           | Max |     |

| tsu                | Set-Up Time<br>(Input or Feedback before Clock |                            | 10    |         | 10           |         | 15            |     | ns  |

| t <sub>H</sub>     | Hold Time (Input after Clock)                  |                            | 0     |         | 0            |         | 0             |     | ns  |

| tw                 | Clock Pulse Width (High/Low)                   |                            | 10    |         | 12           |         | 15            |     | ns  |

| <sup>t</sup> CYCLE | Clock Cycle Period (with Feedback)<br>(Note 3) |                            | 25    |         | 30           |         | 40            |     | ns  |

| fCLK               | Clock Frequency                                | With Feedback              | 40    |         | 33           |         | 25.0          |     | MHz |

|                    | (Note 4)                                       | Without Feedback           | 50.0  |         | 41.7         |         | 33.3          |     | MHz |

| fl                 | Input Frequency (Note 5)                       |                            | 66.7  |         | 50.0         |         | 40.0          |     | MHz |

| t <sub>PR</sub>    | Clock Valid after Pe                           | Clock Valid after Power-Up |       |         | 100          |         | 100           |     | ns  |

Preliminary

Note 1: Absolute maximum ratings are those values beyond which the device may be permanently damaged. Proper operation is not guaranteed outside specified recommended operating conditions.

Note 2: Some device pins may be raised above these limits during programming and preload operations according to the applicable specification.

Note 3:  $t_{CYCLE} = t_{SU} + t_{CLK}$

Note 4:  $t_{CLK}$  (with feedback) = ( $t_{CYCLE}$ ) 1

$t_{CLK}$  (without feedback) = (2  $t_W$ ) 1

Note 5:  $t_{I} = (t_{PD}) 1$

| Symbol           | Parameter                              | Conditions                        |                           | Conditions Temperature Range |       | Тур | Max                 | Units |

|------------------|----------------------------------------|-----------------------------------|---------------------------|------------------------------|-------|-----|---------------------|-------|

| VIH              | High Level Input Voltage               |                                   |                           |                              | 2.0   |     | V <sub>CC</sub> + 1 | v     |

| VIL              | Low Level Input Voltage                |                                   |                           |                              | - 1.0 |     | 0.8                 | v     |

| V <sub>OH</sub>  | High Level Output Voltage              | V <sub>CC</sub> = Min             | I <sub>OH</sub> = -3.2 mA | COM/IND                      | 2.4   |     |                     | V     |

|                  |                                        |                                   | I <sub>OH</sub> = -2.0 mA | MIL                          | 2.4   |     |                     | V     |

| V <sub>OL</sub>  | Low Level Output Voltage               | $V_{CC} = Min$                    | I <sub>OL</sub> = 16 mA   | COM/IND                      |       |     | 0.5                 | v     |

|                  |                                        |                                   | l <sub>OL</sub> = 16 mA   | MIL                          |       |     | 0.5                 | v     |

| lozh             | High Level Off State<br>Output Current | $V_{CC} = Max, V_O = V_{CC} Max$  |                           |                              |       |     | 10                  | μА    |

| lozl             | Low Level Off State<br>Output Current  | $V_{CC} = Max, V_O = GND$         |                           |                              |       |     | - 10                | μA    |

| 1                | Maximum Input Current                  | $V_{CC} = Max,$                   | $V_{I} = V_{CC} Max$      |                              |       |     | 10                  | μA    |

| Чн               | High Level Input Current               | V <sub>CC</sub> = Max,            | $V_{I} = V_{CC} Max$      |                              |       | -   | 10                  | μА    |

| liL .            | Low Level Input Current                | V <sub>CC</sub> = Max,            | $V_{I} = GND$             |                              |       |     | -10                 | μA    |

| los'             | Output Short Circuit Current           | $V_{\rm CC} = 5.0 V_{\rm c}$      | V <sub>O</sub> = GND      |                              | -30   |     | - 160               | mА    |

| lcc              | Supply Current                         | f = 15 MHz, V <sub>CC</sub> = Max |                           | СОМ                          |       |     | 150                 | mA    |

|                  |                                        |                                   |                           | MIL/IND                      |       |     | 180                 | mA    |

| CI               | Input Capacitance                      | $V_{\rm CC} = 5.0V,$              | V <sub>I</sub> = 2.0V     |                              | _     |     | 8                   | pF    |

| C <sub>1/O</sub> | I/O Capacitance                        | $V_{\rm CC} = 5.0V_{\rm r}$       | $V_{I/O} = 2.0V$          |                              |       |     | 10                  | pF    |

\*One output at a time for a maximum duration of one second

# Switching Characteristics Over Recommended Operating Conditions

|                   |                                                       | <b>_</b> .                                                                                   |     | GAL20RA10-15 |         | RA10-20 | GAL20 | Units |    |

|-------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|--------------|---------|---------|-------|-------|----|

| Symbol            | Parameter                                             | Test<br>Conditions                                                                           | COM |              | COM/IND |         | MIL   |       |    |

|                   |                                                       | Conditionio                                                                                  | Min | Max          | Min     | Max     | Min   | Max   |    |

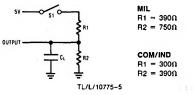

| t <sub>PD</sub>   | Input or Feedback to<br>Combinatorial Output          | C <sub>L</sub> = 50 pF,<br>S1 Closed                                                         |     | 15           |         | 20      |       | 25    | ns |

| <sup>t</sup> CLK  | Clock Input to Registered<br>Output or Feedback       | C <sub>L</sub> = 50 pF,<br>S1 Closed                                                         |     | 15           |         | 20      |       | 25    | ns |

| ts                | Asynchronous Set Input to<br>Registered Output Low    |                                                                                              |     | 15           |         | 20      |       | 25    | ns |

| t <sub>R</sub>    | Asynchronous Reset Input to<br>Registered Output High |                                                                                              |     | 15           |         | 20      |       | 30    | ns |

| <sup>t</sup> PZXG | G Pin Output Enabled                                  | C <sub>L</sub> = 50 pF,<br>Active High: S1 Open,<br>Active Low: S1 Closed                    |     | 12           |         | 15      |       | 20    | ns |

| <sup>t</sup> pxzg | G Pin Output Disabled                                 | $C_L = 5 \text{ pF},$<br>From V <sub>OH</sub> : S1 Open,<br>From V <sub>OL</sub> : S1 Closed |     | 12           |         | 15      |       | 20    | ns |

| <sup>t</sup> PZXI | Input to Output<br>Enabled via Product Term           | C <sub>L</sub> = 50 pF,<br>Active High: S1 Open,<br>Active Low: S1 Closed                    |     | 15           |         | 20      |       | 25    | ns |

| t <sub>PXZI</sub> | Input to Output<br>Disabled via Product Term          | $C_L = 5 \text{ pF},$<br>From V <sub>OH</sub> : S1 Open,<br>From V <sub>OL</sub> : S1 Closed |     | 15           |         | 20      |       | 25    | ns |

### **Ordering Information**

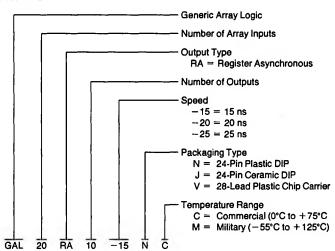

GAL20RA10-15, -20, -25

# **Functional Description**

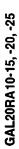

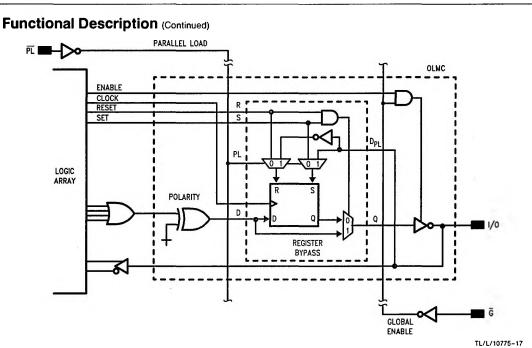

The GAL20RA10 logic array consists of 20 complementary input lines and 80 product-term lines with an EE programmable cell at each intersection (3200 cell). The product terms are organized into ten groups of eight each. Four of the eight product terms in each group connect into an ORgate to produce the sum-of-products logic function. The remaining four product terms in each group are used for control functions in the "Output Logic Macro Cell" (OLMC).

As shown in the GAL20RA10 Block Diagram a total of ten output logic functions are available. Under control of an OLMC each output may be designated either as a registered output configuration or combinatorial.

The logic function output passes through a D-type Flip-Flop triggered by the rising edge of the clock which is defined by one product-term line.

Two product-terms are designated to set or reset the output register and to define the output configuration (register or combinatorial).

| Set | Reset | Output Mode        |

|-----|-------|--------------------|

| 0   | 0     | Register Mode      |

| 0   | 1     | Reset              |

| 1   | 0     | Set                |

| 1   | 1     | Combinatorial Mode |

All architecture cells are normally configured automatically by the development software.

### **Connection Diagram**

### PROGRAMMABLE SET AND RESET

In each OLMC cell, two product lines are dedicated to asynchronous set and reset. If the set product line is high, the register output becomes a logic "1", the output pin becomes a "0". If the reset product line is high, the register output becomes a logic "0", the output pin becomes a "1". The operation of the programmable set and reset overrides the clock.

### INDIVIDUALLY PROGRAMMABLE REGISTER BYPASS

If both the set and reset product lines are high, the sum-ofproducts bypasses the register and appears immediately at the output, thus making the output combinatorial. This allows each output to be configured in the registered or combinatorial mode.

#### **PROGRAMMABLE CLOCK**

One of the product lines in each group is connected to the clock. This provides the user with the additional flexibility of a programmable clock, so each output can be clocked independently of all the others.

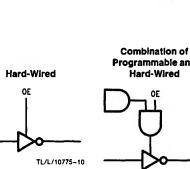

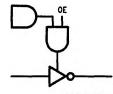

#### PROGRAMMABLE AND HARD-WIRED TRI-STATE OUT-PUTS

The GAL20RA10 provides a product term dedicated to output control. There is also an output control pin (Pin 13). The output is enabled if both the output control pin is low and the output control product term is HIGH. If the output control pin is high all outputs will be disabled or if an output control product term is low, then that output will be disabled.

### PROGRAMMABLE OUTPUT POLARITY

The outputs can be programmed either active-low or activehigh. This is represented by the exclusive-OR gates shown in the GAL20RA10 Logic Diagram. When the output polarity is unprogrammed the lower input to the exclusive-OR gate is high, so the output is active-high. Similarily, when the output polarity cell is 0, or a low impedance connection to GND, the output is active-low. The programmable output polarity features allows the user a high degree of flexibility when writing equations.

### REGISTER PRELOAD

GAL20RA10 offers register preload for device testability. The registers can be preloaded from the outputs by using TTL-level signals, in order to simplify functional testing. The preload signal overrides the set and reset signal.

### POWER-UP RESET

The GAL20RA10 device resets all registers to a low state upon power-up (active-low outputs assume high logic levels if enabled). This may simplify sequential circuit design and test. During power-up, the clock input should assume a valid, stable logic state as early as possible to avoid interfering with the reset operation. The clock input should remain stable until after the power-up reset operation is completed to allow the registers to capture the proper next state on the first high-going transition.

### AC Test Load

### Clock/Input Frequency Specifications

The clock frequency (f<sub>CLK</sub>) parameter listed in the Recommended Operating Conditions table specifies the maximum speed at which the GAL registers are guaranteed to operate. Clock frequency is defined differently for the two cases in which register feedback is used versus when it is not. In a data-path type application, when the logic functions feed into the registers are not dependent on register feedback from the previous cycle (i.e., based only on external inputs), the minimum required cycle period (f<sub>CLK</sub>-1 without feedback) is defined as the greater of the minimum "data window" period (tw high + tw low) and the minimum "data window" period ( $t_{SU} + t_{H}$ ). This assumes optimal alignment between data inputs and the clock input. In sequential logic applications such as state machines, the minimum required cycle period ( $t_{CYCLE} = f_{CLK}^{-1}$  with feedback) is defined as t<sub>CLK</sub> + t<sub>SU</sub>. This provides sufficient time for outputs from the registers to feed back through the logic array and set up on the inputs to the registers before the end of each cycle. The input frequency (f) parameter specifies the maximum rate at which each GAL input can be toggled and still produce valid logic transitions on each combinatorial output. The fl specification is derived as the inverse of the combina-

### **Design Development Support**

torial propagation delay (tpp).

A variety of software tools and programming equipment is available to support the development of designs using GAL products. Typical software packages accept Boolean logic equations to define desired functions. Most are available to run on personal computers and generate a JEDEC-compatible "cell-map" (analogous to a PAL "fuse-map"). The industry-standard JEDEC format ensures that the resulting cell-map file can be down-loaded into a variety of programming equipment. Many software packages and programming units support a large variety of programmable logic products as well. The PLANTM software package from National Semiconductor supports all programmable logic products available from National and is fully JEDEC-compatible. PLAN software also provides automatic device selection based on the designer's Boolean logic equations.

National strongly recommends using only approved programming hardware and software for developing GAL designs. Programming using unapproved equipment generally voids all guarantees. Approved programmers incorporate specialized programming algorithms that program the array and automatically configure the architecture cells. To ensure data retention and reliability, the programming algorithm also tracks the number of programming cycles to which each GAL device has been subjected since shipment, and stores this information automatically in the device.

The special GAL programming algorithm can also program a GAL device using a standard fuse-map developed for any of the emulated PAL products. PAL fuse-maps can be created by any JEDEC-compatible PAL development software or by loading the fuse pattern from an existing programmed PAL device into the programming unit (provided the PAL device has not been secured). However, to utilize the full flexibility of the GAL architecture, true GAL development software (such as PLAN software) is recommended.

Detailed logic diagrams showing all JEDEC cell-map addresses in the GAL logic array and OLMC are provided for direct map editing and diagnostic purposes (see "Programming Details"). For a list of current software and programming support tools available for these devices, please contact your local National sales representative or distributor. If detailed specifications of the GAL programming algorithm are needed, please contact the National Semiconductor Programmable Device Support department.

## **Security Cell**

A security cell is provided on all GAL20V8A devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, the circuitry enabling array access is disabled, preventing further programming or verification of the array. The security cell can be erased only in conjunction with the array during a bulk erase cycle, so the original configuration can never be examined once this cell is programmed.

### **Electronic Signature**

Each GAL device contains an electronic signature word consisting of 64 bits of reprogrammable memory. The electronic signature word can be programmed to contain any identification information desired by the user. Some uses include pattern identification labels, revision numbers, dates, inventory control information, etc. The data stored in the electronic signature word has no effect on the functionality of the device. The information is read out of the device using the normal program verification procedure provided by the programming equipment. The information may be accessed at anytime independent of the state of the security cell. National's PLAN development software allows electronic signature data to be entered by the user and downloaded to the programming equipment.

### **Bulk Erase**

The programming equipment automatically performs a bulk erase operation prior to each programming operation. No special erase operation need be performed by the user. Bulk erase clears the logic array, architecture cells, security cell, and electronic signature information. The GAL device is thereby reverted back to its virgin state.

# Latch-Up Protection

GAL devices are designed with an on-chip charge pump to negatively bias the substrate. The negative bias is of sufficient magnitude to prevent input undershoots from causing the circuitry to latch. Additionally, outputs are designed with n-channel pullups instead of the traditional p-channel pullups to eliminate any possibility of SCR induced latching.

To insure that no undesired bias conditions occur with P+ diffusions, a Latch-Lock<sup>TM</sup> power-up circuitry has been developed. The drain of all P channel devices normally connected to the device supply are now connected to an alternate supply that powers up after the device N-wells have been biased and the substrate has reached its negative clamp value. This prevents any hazardous bias conditions from developing in the power-up sequence. After power-up is complete, the Latch-Lock circuitry becomes dormant until a full power-down has occurred; this eliminates the chance of an unwanted P channel power-down during device operation.

### **Manufacturer Testing**

Because of E<sup>2</sup>CMOS technology, GAL devices can be reprogrammed in milliseconds. This allows each device to be completely tested by the manufacturer using numerous logic array and architecture patterns prior to shipping. Every programmable cell and every logic path through every device is fully tested for programmability, functionality and performance to all AC and DC parameters. The customer can therefore expect 100% programming and functional yield and 100% compliance of all GAL products to data sheet specifications.

The testing procedure performed on all GAL devices by the manufacturer tests all aspects of device operation. Extensive testing of all programmable cells in the device include margin testing, internal verify, and program retention during high-temperature bake. All DC and AC parameters are tested at hot and cold temperatures using a variety of worstcase logic and signal patterns. Functional test include reprogramming each OLMC to all valid architectural configurations.

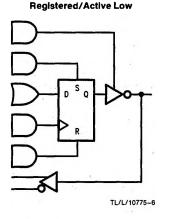

**Output Always Enabled**

TL/L/10775-8

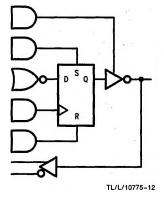

## **OLMC Configurations**

Low TL/L/10775-7

Combinatorial/Active

Combinatorial/Active High

**Registered/Active High**

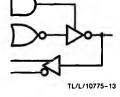

Programmable and Hard-Wired

Programmable

TL/L/10775-11

TL/L/10775-9