# **Data Sheet**

# gmZ1

DAT-0001-D

August 1998

**Genesis Microchip**

200 Town Centre Blvd. • Suite 400 • Markham • ON • Canada • L3R 8G5 • Tel: (905) 470-2742 • Fax: (905) 470-9022 1871 Landings Drive • Mountain View • CA • USA • 94043 • Tel: (650) 428-4277 • Fax: (650) 428-4288 www.genesis-microchip.com / info@genesis-microchip.on.ca

# gmZ1 Data Sheet

# DAT-0001-D

(supersedes gmZ1 Data Sheet DAT-0001-C)

| Document               | Revision Details                                                                                                                               | Date        |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Preliminary 1.0        |                                                                                                                                                | May 1997    |

| DAT-0002-A<br>(CD-ROM) |                                                                                                                                                | Aug 1997    |

| DAT-0001-B             | Figs. 2, 10, 17, 18, 21, 26, 27, Tables 6, 30, Soft Reset description, No Zoom Mode, Z_HORZ_SV, Z_VERT_SV                                      | Oct 1997    |

| DAT-0001-C             | Ref. timing diagrams (p91, 92, 96), Ordering Info (p101), 1.5V switching level threshold (p90), fig. 32, fig. 41, fig. 42, DH_BKGND_END (p81). | April 1998  |

| DAT-0001-D             | Changed reference to "multiscan" on page 3. Added Table 3 - D_BYPASS Mode signals. Added note to Section 5.7                                   | August 1998 |

# TABLE OF CONTENTS

| 1. | OVER      | VIEW                                     | 1  |

|----|-----------|------------------------------------------|----|

| 2. | FEATU     | JRES & APPLICATIONS                      | 2  |

| 3. | GENEI     | RAL OPERATION                            | 4  |

|    |           |                                          |    |

| 4. | PINOU     | Т                                        | 6  |

| 5. | FUNCT     | FIONAL DESCRIPTION                       | 13 |

|    | 5.1. Pow  | ER-ON RESET                              | 13 |

|    | 5.2. Syst | em Clocks                                | 14 |

|    | 5.2.1.    | Input Port Clock                         | 14 |

|    | 5.2.2.    | Display Port Clock                       | 14 |

|    | 5.2.3.    | Overlay Port Clock                       | 15 |

|    | 5.2.4.    | Host Interface Port Clock                | 15 |

|    | 5.3. INPU | T PORT                                   | 16 |

|    | 5.3.1.    | VGB Input Port                           | 16 |

|    | 5.3.2.    | VGA Input Port                           | 22 |

|    | 5.3.3.    | Operating Modes                          | 27 |

|    | 5.3.4.    | Input Active Window Control              |    |

|    | 5.4. RGB  | OUTPUT PORT                              |    |

|    | 5.4.1.    | Data Transfer Modes                      |    |

|    | 5.4.2.    | Programmable Input Lock Event            |    |

|    | 5.4.3.    | D BYPASS Mode                            |    |

|    | 5.4.4.    | Display Timing Generation                |    |

|    | 5.4.5.    | Output Display Timing Exception Handling |    |

|    | 5.4.6.    | Display Active Window Control            |    |

|    | 5.5. Over | rlay Port                                |    |

|    | 5.5.1.    | Input Signals                            |    |

|    | 5.5.2.    | Output Control Signals                   |    |

|    |           | ΓINTERFACE PORT                          |    |

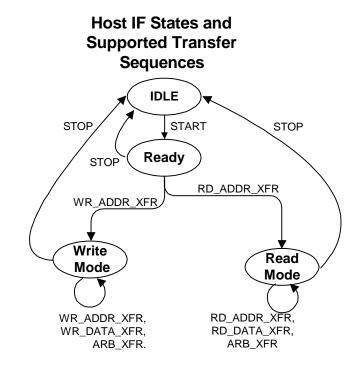

|    | 5.6.1.    | Host Interface Protocol                  |    |

|    | 5.6.2.    | Host Interface State Description         |    |

|    | 5.6.3.    | Typical Usage Scenarios                  |    |

|    | 5.6.4.    | Interrupts                               |    |

|    | 5.6.5.    | Updating Register Contents               |    |

|    | 5.6.6.    | Host I/F Address Map/Control Bit Map.    |    |

|    |           | ΓINTERFACE REGISTERS                     |    |

|    | 5.7.1.    | Host Interface and Main Control Register |    |

|    | 5.7.2.    | Input Control Register                   |    |

|    | 5.7.3.    | Display Control Register                 |    |

|    | 5.7.4.    | Display Output Port Control Register     |    |

|    |           | r                                        |    |

|    | 5.7.5.  | Display Clock Control Register      | 71  |

|----|---------|-------------------------------------|-----|

|    | 5.7.6.  | Status Register                     | 72  |

|    | 5.7.7.  | Interrupt Control Register 1        |     |

|    | 5.7.8.  | Interrupt Control Register 2        | 74  |

|    | 5.7.9.  | Input Video Register                | 75  |

|    | 5.7.10. | Display Register                    | 77  |

|    |         | Zoom Register                       |     |

|    |         | Filter Horizontal Control Register  |     |

|    |         | Display Horizontal Control Register |     |

|    |         | Overlay Register                    |     |

| 6. | ELECT   | TRICAL SPECIFICATIONS               | 86  |

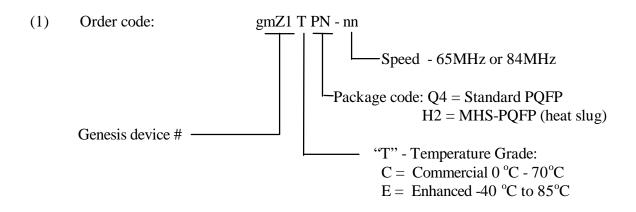

| 7. | ORDE    | RING INFORMATION                    | 104 |

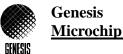

| 8. | MECH    | IANICAL SPECIFICATIONS              | 105 |

# TABLE OF FIGURES

| FIGURE 1: FUNCTIONAL BLOCK DIAGRAM                              | 1  |

|-----------------------------------------------------------------|----|

| FIGURE 2: GMZ1 SYSTEM BLOCK DIAGRAM                             | 5  |

| FIGURE 3: GMZ1 PINOUT                                           |    |

| FIGURE 4: VIDEO COLOR DECODER CONNECTION TO GMZ1                | 17 |

| FIGURE 5: VCLREQ, VCBLNK - START OF FRAME                       | 19 |

| FIGURE 6: VCLREQ OPERATION                                      | 19 |

| FIGURE 7: VCLREQ OPERATION DURING END OF FRAME/FIELD            | 20 |

| FIGURE 8: SINGLE PIXEL MODE - VGB PORT INTERFACING              | 21 |

| FIGURE 9: CCIR 601 SIGNAL RANGE                                 | 21 |

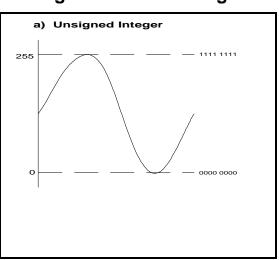

| FIGURE 10: DATA RANGE                                           | 23 |

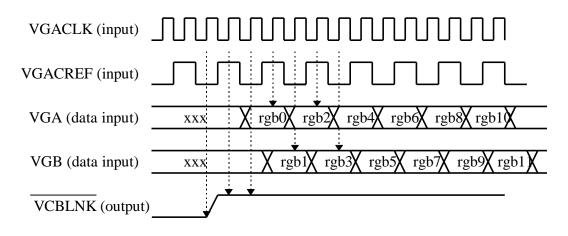

| FIGURE 11: PIXEL WIDTH MODE                                     | 24 |

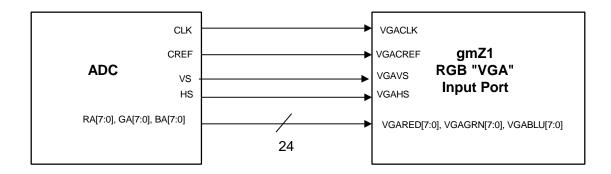

| FIGURE 12: SINGLE PIXEL - RGB "VGA" PORT INTERFACING            | 24 |

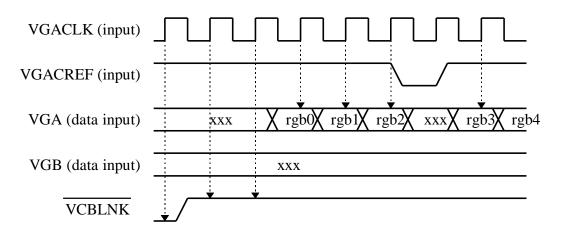

| FIGURE 13: RGB SINGLE PIXEL TIMING                              | 25 |

| FIGURE 14: DOUBLE PIXEL - VGA AND VGB PORTS INTERFACING         | 25 |

| FIGURE 15: RGB DOUBLE PIXEL TIMING                              | 26 |

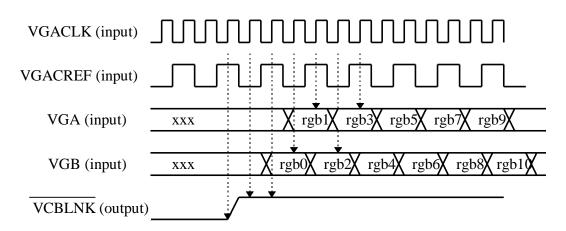

| FIGURE 16: RGB DOUBLE PIXEL OFFSET TIMING #1                    | 27 |

| FIGURE 17: RGB PORT DOUBLE PIXEL OFFSET TIMING #2               | 27 |

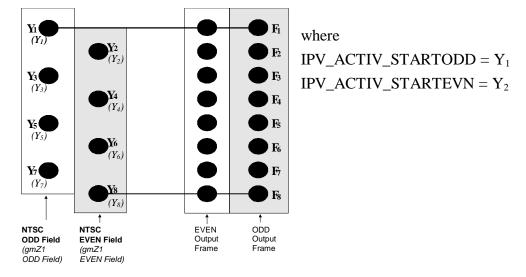

| FIGURE 18: NTSC DE-INTERLACING ZOOM                             | 29 |

| FIGURE 19: PAL DE-INTERLACING ZOOM                              | 29 |

| FIGURE 20: YUV DATA START OF ACTIVE WINDOW                      | 30 |

| FIGURE 21: YUV DATA END OF ACTIVE WINDOW                        | 31 |

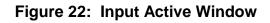

| FIGURE 22: INPUT ACTIVE WINDOW                                  | 32 |

| FIGURE 23: DISPLAY DATA TIMING SINGLE PIXEL MODE                | 33 |

| FIGURE 24: DISPLAY DATA TIMING DOUBLE PIXEL MODE                | 34 |

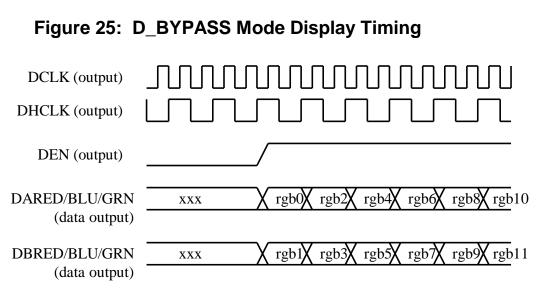

| FIGURE 25: D_BYPASS MODE DISPLAY TIMING                         | 36 |

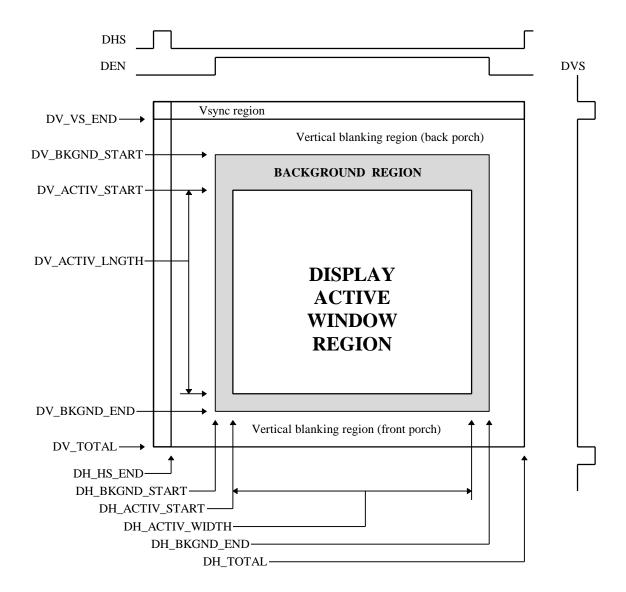

| FIGURE 26: DISPLAY TIMING DIAGRAM                               | 44 |

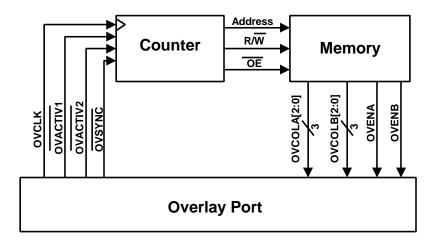

| FIGURE 27: EXAMPLE OF OVERLAY IMPLEMENTATION                    | 45 |

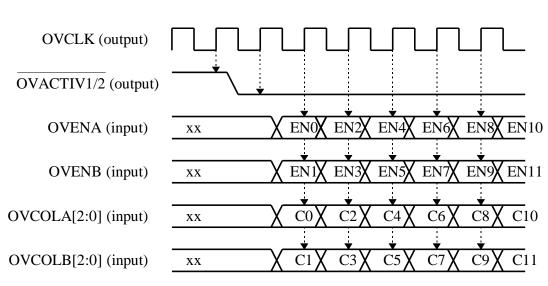

| FIGURE 28: OVERLAY PORT - START OF ACTIVE OVERLAY LINE          | 47 |

| FIGURE 29: OVERLAY PORT - END OF ACTIVE OVERLAY LINE            | 47 |

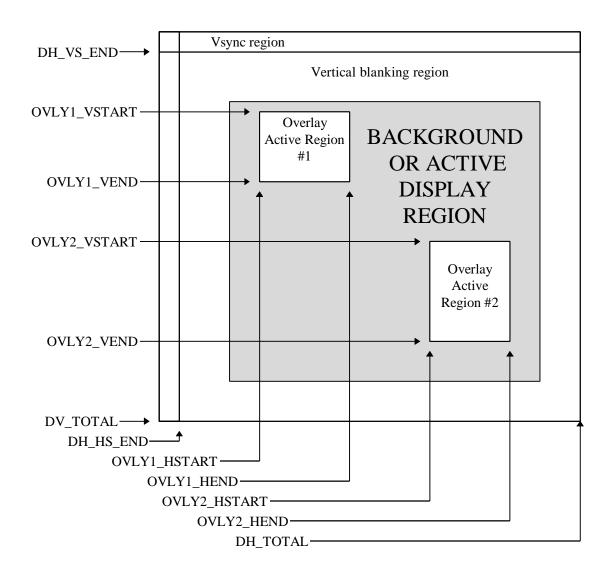

| FIGURE 30: OVERLAY ACTIVE REGION PROGRAMMING                    | 48 |

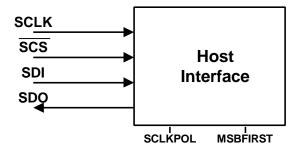

| FIGURE 31: HOST INTERFACE PORT                                  | 50 |

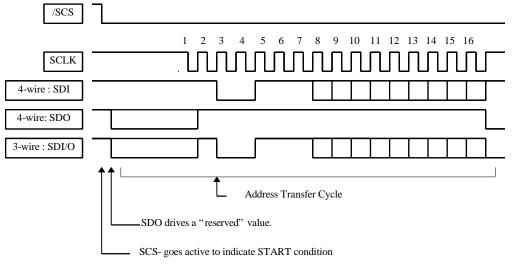

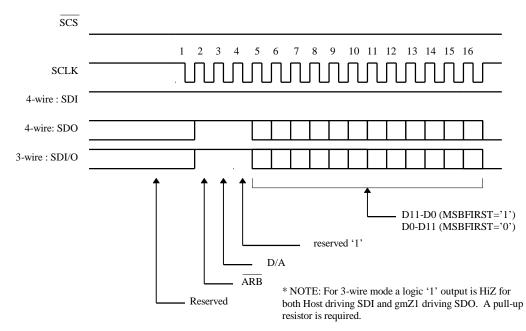

| FIGURE 32: HOST I/F START CONDITION (FOLLOWED BY ADDRESS CYCLE) | 54 |

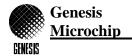

| FIGURE 33: HOST I/F ADDRESS TRANSFER                            | 54 |

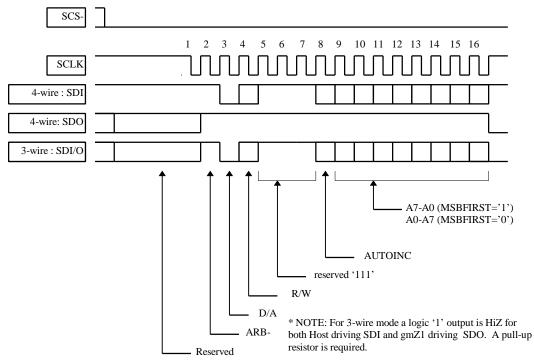

| FIGURE 34: HOST I/F ADDRESS READ BACK (ARB) TRANSFER            | 55 |

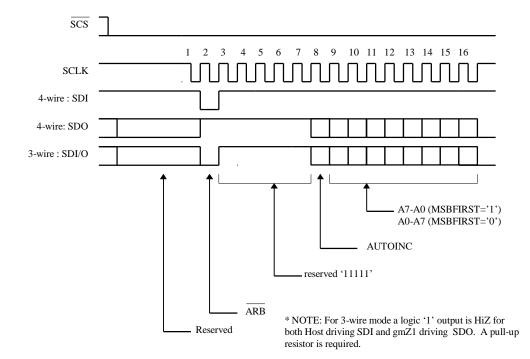

| FIGURE 35: HOST I/F WRITE DATA TRANSFER                         | 56 |

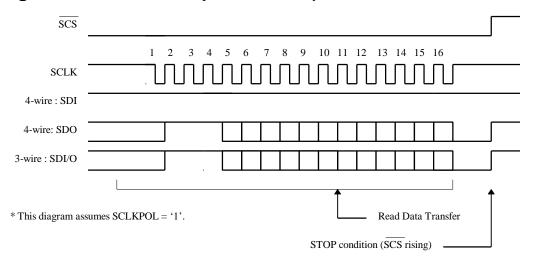

| FIGURE 36: HOST I/F READ DATA TRANSFER                          | 56 |

| FIGURE 37: HOST I/F STOP CONDITION (AFTER A READ DATA TRANSFER) | 57 |

| FIGURE 38: HOST INTERFACE OPERATING STATES AND TRANSFERS        | 57 |

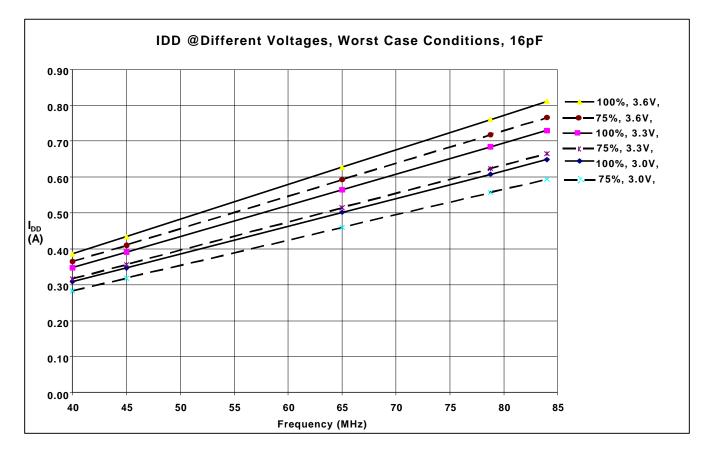

| FIGURE 39: I <sub>DD</sub> @ 16PF OUTPUT LOAD                   | 88 |

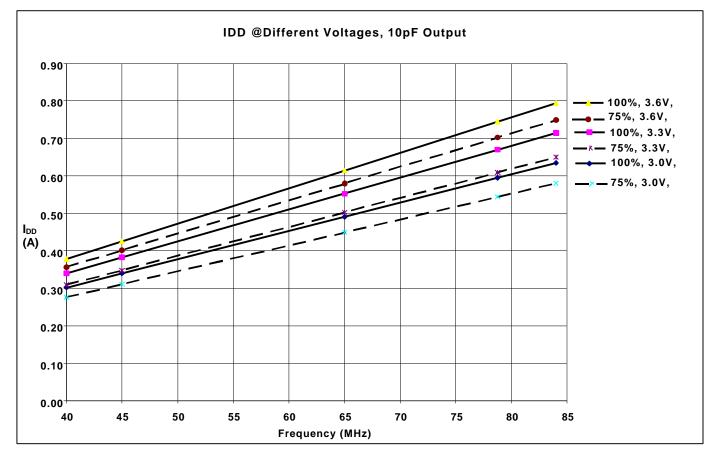

| FIGURE 40: I <sub>DD</sub> @ 10pF Output Load                   | 90 |

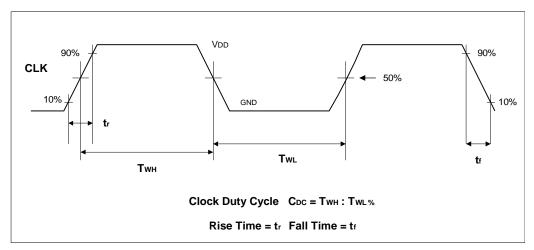

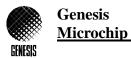

| FIGURE 41: CLOCK REFERENCE LEVELS                               | 94 |

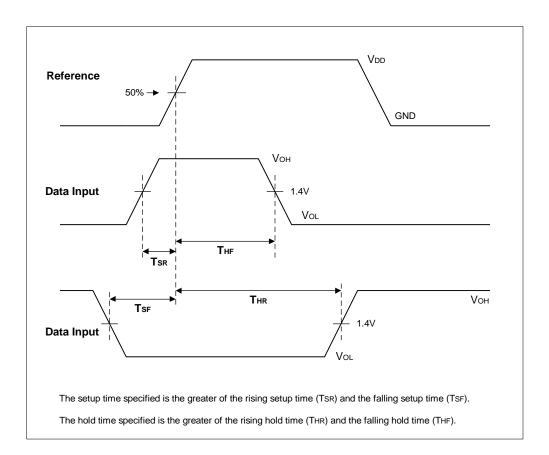

| FIGURE 42: SETUP AND HOLD REFERENCE LEVELS                      | 94 |

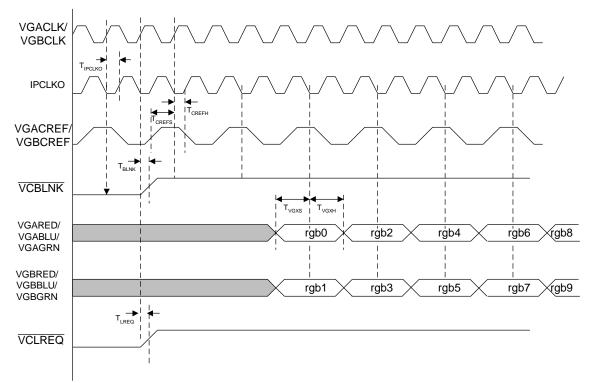

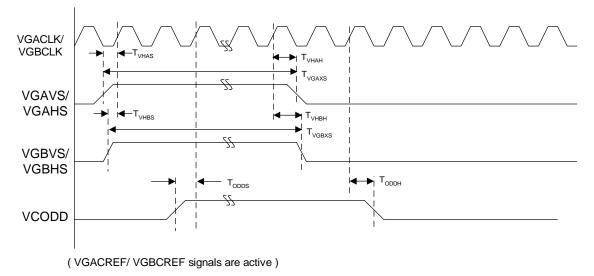

| FIGURE 43: VGA & VGB PORT TIMING                                | 95 |

| FIGURE 44: | VGA & VGB Port Timing                    | 95   |

|------------|------------------------------------------|------|

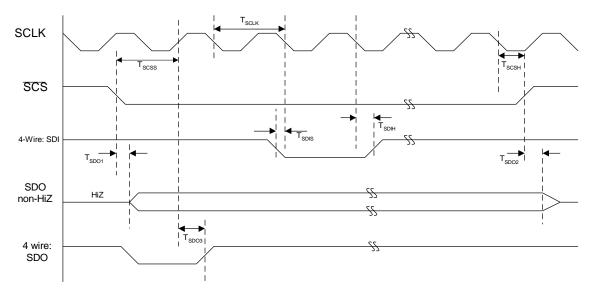

| FIGURE 45: | 4-WIRE MODE HOST I/F TIMING              | 97   |

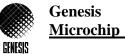

| FIGURE 46: | OVERLAY PORT TIMING                      | 98   |

| FIGURE 47: | PROPAGATION DELAY REFERENCE LEVELS       | 99   |

| FIGURE 48: | SINGLE PIXEL DISPLAY PORT TIMING         | .100 |

| FIGURE 49: | DISPLAY PORT TIMING                      | .100 |

| FIGURE 50: | DISPLAY PORT TIMING - DCLK_PHASE[1:0]    | 101  |

| FIGURE 51: | DOUBLE PIXEL - DISPLAY PORT TIMING       | .102 |

| FIGURE 52: | BY-PASS MODE - DISPLAY PORT TIMING       | .103 |

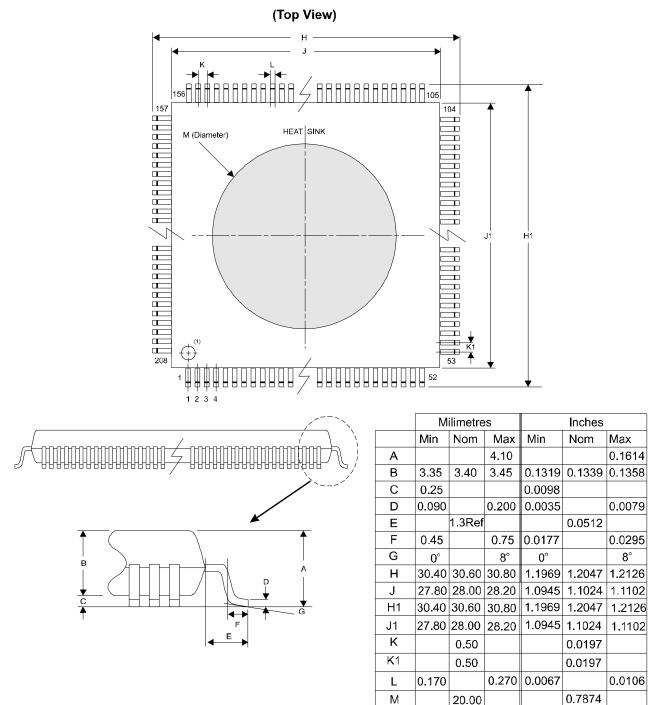

| FIGURE 53: | Q4 PACKAGE (208-PIN PQFP)                | .105 |

| FIGURE 54: | H2 PACKAGE (208-PIN PQFP WITH HEAT SLUG) | 106  |

|            |                                          |      |

# LIST OF TABLES

| TABLE 1: GMZ1 PINOUT                                         |    |

|--------------------------------------------------------------|----|

| TABLE 2: SUMMARY - I/O INTERFACING TO GMZ1                   | 16 |

| TABLE 3: CORRESPONDING INPUT/OUTPUT SIGNALS IN D_BYPASS      | 35 |

| TABLE 4: DISPLAY TIMING GENERATION: SYNCHRONIZATION MODES    | 36 |

| TABLE 5: OVERLAY COLOR CONTROLS                              | 46 |

| TABLE 6: HOST I/F SDO MODE                                   | 51 |

| TABLE 7: SUMMARY OF THE 3-WIRE HOST I/F TRANSFER MODES       | 52 |

| TABLE 8: SUMMARY OF THE 4-WIRE HOST I/F TRANSFER MODES       | 53 |

| TABLE 9: MON_SEL[2:0]                                        | 63 |

| TABLE 10: HOSTCTRL                                           | 64 |

| TABLE 11: IPCTRL                                             | 66 |

| TABLE 12: DCONTROL                                           | 68 |

| TABLE 13: DOUTCNTRL                                          | 70 |

| TABLE 14: DCLK_CTRL                                          | 71 |

| TABLE 15: STATUS                                             | 72 |

| TABLE 16: IRQ1CNTRL                                          | 73 |

| TABLE 17: IRQ2CNTRL                                          | 74 |

| TABLE 18: INPUT VIDEO                                        | 75 |

| TABLE 19: DISPLAY LINE RATE                                  | 77 |

| Тавle 20: ZOOM                                               | 78 |

| TABLE 21: FHC - FILTER HORIZONTAL CONTROL                    | 80 |

| TABLE 22: DISPLAY HORIZONTAL                                 | 80 |

| TABLE 23: OVERLAY                                            | 84 |

| TABLE 24 RECOMMENDED OPERATING CONDITIONS                    | 86 |

| TABLE 25: ABSOLUTE MAXIMUM RATINGS                           | 86 |

| TABLE 26 DC CHARACTERISTICS                                  | 87 |

| TABLE 27 : IDD FOR DIFFERENT CONDITIONS, 16PF OUTPUT LOADING | 88 |

| TABLE 28 : POWER DISSIPATION = 2.92W @ 3.6V, 84MHz, 100% DATA SWITCHING |     |

|-------------------------------------------------------------------------|-----|

| TABLE 29 : POWER DISSIPATION = 2.26W @ 3.6V, 65MHz, 100% DATA SWITCHING |     |

| TABLE 30 : POWER DISSIPATION = 2.21W @ 3.3V, 84MHz, 75% DATA SWITCHING  |     |

| TABLE 31 : POWER DISSIPATION = 1.68W @ 3.3V, 65MHz, 75% DATA SWITCHING  | 90  |

| TABLE 32 : IDD FOR DIFFERENT CONDITIONS WITH 10PF OUTPUT LOADING        | 91  |

| TABLE 33 : POWER DISSIPATION = 2.84W @ 3.6V, 84MHz, 100% DATA SWITCHING | 91  |

| TABLE 34 : POWER DISSIPATION = 2.20W @ 3.6V, 65MHz, 100% DATA SWITCHING | 91  |

| TABLE 35 : POWER DISSIPATION = 2.14W @ 3.3V, 84MHz, 75% DATA SWITCHING  | 92  |

| TABLE 36 : POWER DISSIPATION = 1.65W @ 3.3V, 65MHz, 75% DATA SWITCHING  | 92  |

| TABLE 37: VGA & VGB PORT TIMING                                         | 93  |

| TABLE 38: HOST I/F PORT TIMING                                          | 96  |

| TABLE 39: OVERLAY PORT TIMING                                           | 97  |

| TABLE 40:         MISCELLANEOUS INPUTS TIMING                           |     |

| TABLE 41: SINGLE PIXEL MODE DISPLAY PORT TIMING                         |     |

| TABLE 42: DISPLAY PORT TIMING - DCLK_PHASE[1:0]                         | 101 |

| TABLE 43: DOUBLE PIXEL MODE DISPLAY PORT TIMING                         |     |

| TABLE 44: DISPLAY PORT TIMING - D_BYPASS MODE                           |     |

# 1. Overview

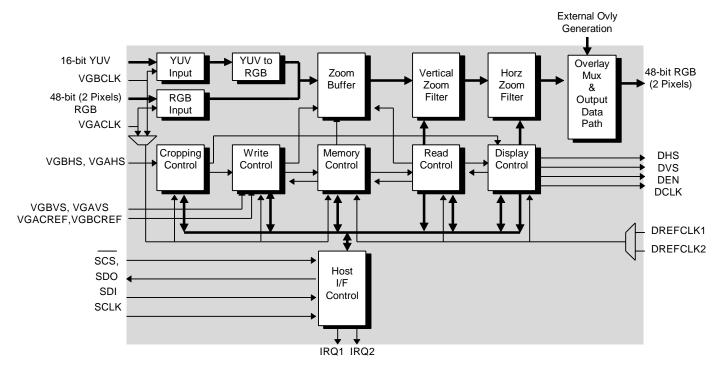

The gmZ1 is a highly-integrated IC producing real-time, high-quality, scaled digital video or computer graphics images. Three separate data channels have been integrated into the gmZ1, allowing complete images to be resized using a single device. The gmZ1 performs image magnification (zoom) on 24-bit RGB or 16-bit YUV input data streams. The RGB video ports support single width (24-bit) or double width (48-bit) pixel transfers.

The gmZ1 performs advanced interpolation and finite impulse response (FIR) filtering independently in both the vertical and horizontal directions. The output image's spatial frequency response is automatically adjusted to preserve image bandwidth and to minimize imaging artifacts, resulting in the highest image quality.

Both graphics and status overlay information can be displayed on top of the scaled video data by means of an overlay port. A "transparent" capability exists for viewing zoomed video within and around any alpha-numeric or graphics overlay.

# Figure 1: Functional Block Diagram

# 2. Features & Applications

# High quality advanced zoom-only engine:

- Fully programmable zoom ratios

- Independent Horizontal/Vertical zoom

- An advanced zoom algorithm provides pristine image quality

### Spatial de-interlacing of video inputs

• Corrected spatial positioning of odd and even input lines

### **Built-in display timing generator**

- Can be used to drive AMLCD panels

- Special support for DMD engines

- Fully programmable timing parameters

### **YUV inputs:**

- 16-bit YUV input video

- Clock rates up to 45MHz

- NTSC/PAL square pixels/CCIR601

- Glue-less connection to many color decoders, ex. Philips SAA7110/7111

- Built-in YUV to RGB color space converter

### **RGB** inputs:

- Single 24-bit RGB pixels @ 84MHz

- 48-bit RGB pixel @ 42MHz

- Programmable input port

### **Output Pixel Modes supported:**

- 1 and 2 pixel/clock panel support

- Single 24 bit RGB pixel/clock @ 84MHz

- Dual 48 bit RGB pixels/clock @ 42 MHz

- Dithering logic to enhance pixel color depth for 18-bit panels

- Compliant with proposed VESA FPDI-2 standard via direct connect to NSC, C&T, SII LVDS transceivers

### **Operating Modes**

- Bypass mode with no filtering

- 1:1 scaling

- Non-interlaced zoom

- De-interlacing zoom

### **Display Synchronization Modes**

- Frame Sync input & output frame periods are forced to synchronize

- Line Sync display line rate synthesized from the input line rate

- Free Run input and output rates are not synchronized - ideal for frame-rate conversions

# Simplicity of design speeds time to market

- Single-chip zoom-only solution

- No external memory required

- Programmable horizontal and vertical front and back porches on input data

- Input active window region decoded

- Active window framing signal requests pixels 2 clocks before sampling time

- Using line request and pixel request signals, pipelined video data I/F can be easily designed

- Overlay menus supported via dedicated port, control, and data lines

- 4-wire or 3-wire serial host interface for easy connection to Intel/Motorola MCUs

### Applications

- Projection Systems based on AMLCDs, DMDs

- Fixed-resolution Pixelated Display devices

- Multiscan LCD Panels for CRT

replacement

- Standards conversion

- Scan doublers/quadruplers/converters

- Home theater

- Video Walls

# 3. General Operation

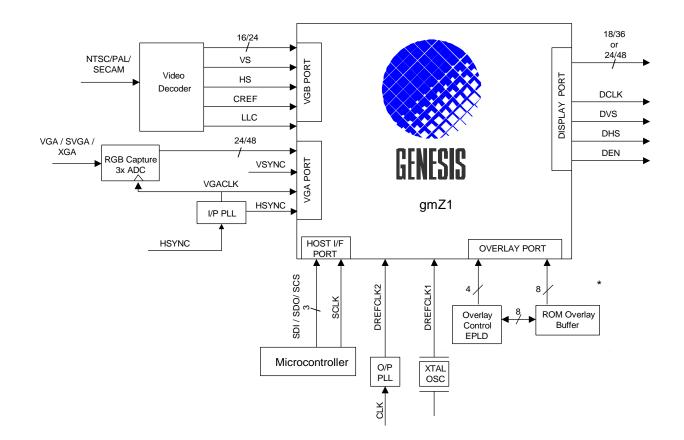

The gmZ1 has been designed to simplify connection to both digital video and graphics data streams. Once the gmZ1 is programmed, high quality zoom processing is performed using independently adjustable ADVANCED ZOOM filtering in the vertical and horizontal directions. All filter coefficients are generated internally without additional programming.

The gmZ1 scales the selected input video by a 1X or larger zoom ratio to create an output image of equal or greater size. The gmZ1 requires no external frame buffer when the input and output formats have equal frame rates and the vertical active periods are synchronized. Magnification plus frame-rate conversion may be performed using the Genesis gmFC1 Frame Rate Converter chip along with the gmZ1 (see Application Note MSD-0016).

The video input data is transferred to the gmZ1 at the selected video input pixel clock rate and stored in an internal zoom buffer. Data is read from the zoom buffer for processing by the onchip scaler and subsequent display at the display pixel clock rate. The selected input and output display clocks can run at different frequencies.

An overlay port outputs programmable overlay timing information to external overlay circuitry that generates 8-bit overlay color select data (See Application Note MSD-0008). Two independent overlay display regions may be displayed on top of the scaled output. Pixel-by-pixel enabling control provides "transparent" capability for viewing zoomed video within and around any alpha numeric or graphics overlay.

The gmZ1 can be initialized by an external micro-controller to program the control, status, filter parameter, and timing parameter registers via a serial interface port. All registers can be accessed using read, write, burst-read, and burst-write I/O cycles. The gmZ1 provides status and video timing information to the system through a status register and programmable interrupts.

A gmZ1 Programming Cable and software is available from Genesis Microchip to help speed up gmZ1 designs. This Cable Module allows a PC to access and program gmZ1 registers directly (See Application Note MSD-0004). What'sOn Software is also available to help in calculating gmZ1 register parameters (See The What'sOn User Guide SED-0015).

# Figure 2: gmZ1 System Block Diagram

\* Overlay control may be simplified using a single chip OSD device such as the Motorola 141544DW. See Genesis Application Note MSD-0008.

# 4. Pinout

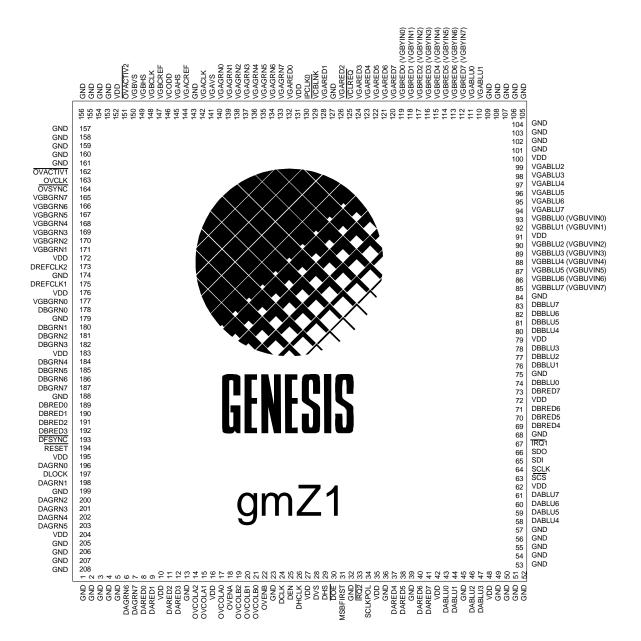

# Figure 3: gmZ1 Pinout

# Table 1: gmZ1 Pinout

## "VGB" Input Port (YUV or RGB Data) - Input Signals

| PIN # | Symbol           | I/O | Description                                                   |

|-------|------------------|-----|---------------------------------------------------------------|

| 148   | VGBCLK           | Ι   | Video input system clock                                      |

| 147   | VGBCREF          | Ι   | Input pixel clock qualifier - programmable active high or low |

| 150   | VGBVS            | Ι   | Vertical sync - programmable active high or low               |

| 149   | VGBHS            | Ι   | Horizontal sync - programmable active high or low             |

| 119   | VGBRED0/VGBYIN0  | Ι   | Red input data /Input data for Y - LSBit                      |

| 118   | VGBRED1/VGBYIN1  | Ι   | Red input data /Input data for Y                              |

| 117   | VGBRED2/VGBYIN2  | Ι   | Red input data /Input data for Y                              |

| 116   | VGBRED3/VGBYIN3  | Ι   | Red input data /Input data for Y                              |

| 115   | VGBRED4/VGBYIN4  | Ι   | Red input data /Input data for Y                              |

| 114   | VGBRED5/VGBYIN5  | Ι   | Red input data /Input data for Y                              |

| 113   | VGBRED6/VGBYIN6  | Ι   | Red input data /Input data for Y                              |

| 112   | VGBRED7/VGBYIN7  | Ι   | Red input data /Input data for Y - MSBit                      |

| 177   | VGBGRN0          | Ι   | Green input data - LSBit                                      |

| 171   | VGBGRN1          | Ι   | Green input data                                              |

| 170   | VGBGRN2          | Ι   | Green input data                                              |

| 169   | VGBGRN3          | Ι   | Green input data                                              |

| 168   | VGBGRN4          | Ι   | Green input data                                              |

| 167   | VGBGRN5          | Ι   | Green input data                                              |

| 166   | VGBGRN6          | Ι   | Green input data                                              |

| 165   | VGBGRN7          | Ι   | Green input data - MSBit                                      |

| 93    | VGBBLU0/VGBUVIN0 | Ι   | Blue input data /Input data for UV - LSBit                    |

| 92    | VGBBLU1/VGBUVIN1 | Ι   | Blue input data /Input data for UV                            |

| 90    | VGBBLU2/VGBUVIN2 | Ι   | Blue input data /Input data for UV                            |

| 89    | VGBBLU3/VGBUVIN3 | Ι   | Blue input data /Input data for UV                            |

| 88    | VGBBLU4/VGBUVIN4 | Ι   | Blue input data /Input data for UV                            |

| 87    | VGBBLU5/VGBUVIN5 | Ι   | Blue input data /Input data for UV                            |

| 86    | VGBBLU6/VGBUVIN6 | Ι   | Blue input data /Input data for UV                            |

| 85    | VGBBLU7/VGBUVIN7 | Ι   | Blue input data /Input data for UV - MSBit                    |

Note: VGB port input data represents the Right pixel of a pixel pair in double wide mode

| PIN # | Symbol  | I/O | Description                                                         |

|-------|---------|-----|---------------------------------------------------------------------|

| 142   | VGACLK  | Ι   | Video graphics input system clock                                   |

| 144   | VGACREF | Ι   | Video graphics input system clock enable - programmable active high |

|       |         |     | or low                                                              |

| 141   | VGAVS   | Ι   | Vertical sync - programmable active high or low                     |

| 145   | VGAHS   | Ι   | Horizontal sync - programmable active high or low                   |

| 132   | VGARED0 | Ι   | Red input data - LSBit                                              |

| 128   | VGARED1 | Ι   | Red input data                                                      |

| 126   | VGARED2 | Ι   | Red input data                                                      |

| 124   | VGARED3 | Ι   | Red input data                                                      |

| 123   | VGARED4 | Ι   | Red input data                                                      |

| 122   | VGARED5 | Ι   | Red input data                                                      |

| 121   | VGARED6 | Ι   | Red input data                                                      |

| 120   | VGARED7 | Ι   | Red input data - MSBit                                              |

| 140   | VGAGRN0 | Ι   | Green input data - LSBit                                            |

| 139   | VGAGRN1 | Ι   | Green input data                                                    |

| 138   | VGAGRN2 | Ι   | Green input data                                                    |

| 137   | VGAGRN3 | Ι   | Green input data                                                    |

| 136   | VGAGRN4 | Ι   | Green input data                                                    |

| 135   | VGAGRN5 | Ι   | Green input data                                                    |

| 134   | VGAGRN6 | Ι   | Green input data                                                    |

| 133   | VGAGRN7 | Ι   | Green input data - MSBit                                            |

| 111   | VGABLU0 | Ι   | Blue input data - LSBit                                             |

| 110   | VGABLU1 | Ι   | Blue input data                                                     |

| 99    | VGABLU2 | Ι   | Blue input data                                                     |

| 98    | VGABLU3 | Ι   | Blue input data                                                     |

| 97    | VGABLU4 | Ι   | Blue input data                                                     |

| 96    | VGABLU5 | Ι   | Blue input data                                                     |

| 95    | VGABLU6 | Ι   | Blue input data                                                     |

| 94    | VGABLU7 | Ι   | Blue input data - MSBit                                             |

### "VGA" Input Port (RGB Data) - Input Signals

Note: VGA port input data represents the Left pixel of a pixel pair in double wide mode

### Input Port Control Signals - Common Control signals for "VGB" and "VGA" ports.

| PIN # | Symbol | I/O | Description                                                                                                 |

|-------|--------|-----|-------------------------------------------------------------------------------------------------------------|

| 146   | VCODD  | Ι   | Interlace Mode Field status, programmable active high or low.<br>Default 1=odd field, 0=even field          |

| 125   | VCLREQ | 0   | Line request signal indicates the gmZ1 is ready to accept input lines                                       |

| 129   | VCBLNK | 0   | When de-asserted, blanking output indicates active capture window for the selected (VGA or VGB) video input |

## **Overlay Port**

| PIN # | Symbol   | I/O | Description                                                            |

|-------|----------|-----|------------------------------------------------------------------------|

| 163   | OVCLK    | 0   | Clock for external overlay circuit (operates at half the display pixel |

|       |          |     | rate).                                                                 |

| 164   | OVSYNC   | 0   | Overlay vertical synchronization pulse indicates start of new frame of |

|       |          |     | display overlay data.                                                  |

| 162   | OVACTIV1 | 0   | Overlay status indicates active overlay window region #1               |

|       |          |     |                                                                        |

| 151   | OVACTIV2 | 0   | Overlay status indicates active overlay window region #2               |

| 18    | OVENA    | Ι   | Enables overlay "A" color.                                             |

| 17    | OVCOLA0  | Ι   | Overlay "A" color select - Blue                                        |

| 15    | OVCOLA1  | Ι   | Overlay "A" color select - Green                                       |

| 14    | OVCOLA2  | Ι   | Overlay "A" color select - Red                                         |

| 22    | OVENB    | Ι   | Enables overlay "B" color.                                             |

| 21    | OVCOLB0  | Ι   | Overlay "B" color select - Blue                                        |

| 20    | OVCOLB1  | Ι   | Overlay "B" color select - Green                                       |

| 19    | OVCOLB2  | Ι   | Overlay "B" color select - Red                                         |

### Display Port

| PIN # | Symbol   | I/O | Description                                                           |

|-------|----------|-----|-----------------------------------------------------------------------|

| 30    | DOE      | Ι   | Display Port Output Enable. A logic "1" tri-states all Display Output |

|       |          |     | Port clock, control and data output signals.                          |

| 175   | DREFCLK1 | Ι   | Display timing reference clock #1                                     |

| 173   | DREFCLK2 | Ι   | Display timing reference clock #2                                     |

| 24    | DCLK     | 0   | Display output clock. Programmable phase.                             |

| 26    | DHCLK    | 0   | Half rate display output clock. Programmable phase.                   |

| 28    | DVS      | 0   | Display vertical sync. Programmable active high or low.               |

| 29    | DHS      | 0   | Display horizontal sync. Programmable active high or low.             |

Genesis <u>Microchip</u>

| PIN # | Symbol | I/O | Description                                        |  |

|-------|--------|-----|----------------------------------------------------|--|

| 25    | DEN    | 0   | Display enable (specifies active area of display). |  |

|       |        |     | Programmable active high or low.                   |  |

| 8     | DARED0 | 0   | Red output data - LSBit                            |  |

| 9     | DARED1 | 0   | Red output data                                    |  |

| 11    | DARED2 | 0   | Red output data                                    |  |

| 12    | DARED3 | 0   | Red output data                                    |  |

| 37    | DARED4 | 0   | Red output data                                    |  |

| 38    | DARED5 | 0   | Red output data                                    |  |

| 40    | DARED6 | 0   | Red output data                                    |  |

| 41    | DARED7 | 0   | Red output data - MSBit                            |  |

| 196   | DAGRN0 | 0   | Green output data - LSBit                          |  |

| 198   | DAGRN1 | 0   | Green output data                                  |  |

| 200   | DAGRN2 | 0   | Green output data                                  |  |

| 201   | DAGRN3 | 0   | Green output data                                  |  |

| 202   | DAGRN4 | 0   | Green output data                                  |  |

| 203   | DAGRN5 | 0   | Green output data                                  |  |

| 6     | DAGRN6 | 0   | Green output data                                  |  |

| 7     | DAGRN7 | 0   | Green output data - MSBit                          |  |

| 43    | DABLU0 | 0   | Blue output data - LSBit                           |  |

| 44    | DABLU1 | 0   | Blue output data                                   |  |

| 46    | DABLU2 | 0   | Blue output data                                   |  |

| 47    | DABLU3 | 0   | Blue output data                                   |  |

| 58    | DABLU4 | 0   | Blue output data                                   |  |

| 59    | DABLU5 | 0   | Blue output data                                   |  |

| 60    | DABLU6 | 0   | Blue output data                                   |  |

| 61    | DABLU7 | 0   | Blue output data - MSBit                           |  |

| 189   | DBRED0 | 0   | Red output data - LSBit                            |  |

| 190   | DBRED1 | 0   | Red output data                                    |  |

| 191   | DBRED2 | 0   | Red output data                                    |  |

| 192   | DBRED3 | 0   | Red output data                                    |  |

| 69    | DBRED4 | 0   | Red output data                                    |  |

| 70    | DBRED5 | 0   | Red output data                                    |  |

| 71    | DBRED6 | 0   | Red output data                                    |  |

| 73    | DBRED7 | 0   | Red output data - MSBit                            |  |

| 178   | DBGRN0 | 0   | Green output data - LSBit                          |  |

| 180   | DBGRN1 | 0   | Green output data                                  |  |

| 181   | DBGRN2 | 0   | Green output data                                  |  |

| 182   | DBGRN3 | 0   | Green output data                                  |  |

| 184   | DBGRN4 | 0   | Green output data                                  |  |

| 185   | DBGRN5 | 0   | Green output data                                  |  |

| 186   | DBGRN6 | 0   | Green output data                                  |  |

| PIN # | Symbol | I/O | Description               |

|-------|--------|-----|---------------------------|

| 187   | DBGRN7 | Ο   | Green output data - MSBit |

| 74    | DBBLU0 | Ο   | Blue output data - LSBit  |

| 76    | DBBLU1 | Ο   | Blue output data          |

| 77    | DBBLU2 | Ο   | Blue output data          |

| 78    | DBBLU3 | 0   | Blue output data          |

| 80    | DBBLU4 | Ο   | Blue output data          |

| 81    | DBBLU5 | 0   | Blue output data          |

| 82    | DBBLU6 | 0   | Blue output data          |

| 83    | DBBLU7 | 0   | Blue output data - MSBit  |

### Note: DA output data represents the Left pixel of a pixel pair in double wide mode.

DB output data represents the Right pixel of a pixel pair in double wide mode.

### Host Interface Control Signals

| PIN # | Symbol   | I/O | Description                                              |  |  |

|-------|----------|-----|----------------------------------------------------------|--|--|

| 194   | RESET    | Ι   | Reset input for initializing the device                  |  |  |

| 31    | MSBFIRST | Ι   | Selects data bit order MSB or LSB first operation,       |  |  |

|       |          |     | 0=LSBit First; 1=MSBit First.                            |  |  |

| 34    | SCLKPOL  | Ι   | 0=SDI sampled on SCLK rising edge, SDO clock out on SCLK |  |  |

|       |          |     | falling edge.                                            |  |  |

| 63    | SCS      | Ι   | Serial Control I/F Chip select                           |  |  |

| 64    | SCLK     | Ι   | Serial Control I/F Clock                                 |  |  |

| 65    | SDI      | Ι   | Serial Control I/F Input Data                            |  |  |

| 66    | SDO      | 0   | Serial Control I/F Output Data                           |  |  |

### Miscellaneous Interface Signals

| PIN # | Symbol | I/O | Description                                                                                                                                                                 |  |

|-------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 67    | IRQ1   | 0   | Interrupt or status output to host controller. Programmable to indicate IPVsync, OPVsync, Zoom buffer Error (over/under flow).                                              |  |

| 33    | IRQ2   | 0   | Interrupt or status output to host controller. Programmable to indicate IPVsync, OPVsync, Zoom buffer Error (over/under flow).                                              |  |

| 197   | DLOCK  | Ι   | Display REFCLK lock status                                                                                                                                                  |  |

| 193   | DFSYNC | Ι   | Display Timing Forced Synchronization - forces the Display Timing<br>Generation to a programmable location within the blanking interval<br>when a falling edge is detected. |  |

| 130   | IPCLKO | 0   | Selected input pixel port clock (VGBCLK or VGACLK). For use as reference to external display clock synthesis PLL which generates DREFCLK1 or DREFCLK2.                      |  |

Power and Ground

| Power Supply, +3.3V | 10, 16, 27, 35, 42, 48, 62, 72, 79, 91, 100, |

|---------------------|----------------------------------------------|

| [18 pins]           | 131,152, 172, 176, 183, 195, 204             |

**Ground** [51 pins]

1, 2, 3, 4, 5, 13, 23, 32, 36, 39, 45, 49, 50, 51, 52, 53,54, 55, 56, 57, 68, 75, 84, 101, 102, 103, 104 105, 106, 107, 108, 109, 127, 143, 153, 154, 155 156, 157, 158, 159, 160, 161, 174, 179, 188, 199 205, 206, 207, 208

# 5. FUNCTIONAL DESCRIPTION

# 5.1. Power-on Reset

A Power-on Reset cycle is required to place the gmZ1 into a defined state, and should be initiated after any power supply excursion outside of the range specified in Table 26. If a Power-on Reset cycle is not performed, the operation of the gmZ1 cannot be guaranteed and the output image data may be corrupted.

A Power-on Reset cycle is performed by asserting  $\overrightarrow{\text{RESET}}$  for at least 100 nsec. This forces all internal programmable registers to be set to zero. SCLK must be asserted (logic high) for a minimum of 50 nsec during the  $\overrightarrow{\text{RESET}}$  pulse.

After the  $\overrightarrow{\text{RESET}}$  pulse, the selected input and display clocks (VGBCLK and DREFCLK1 by default) must receive a minimum of 8 rising clock edges before normal operation will commence.

# 5.2. System Clocks

There are master clocks for each of the gmZ1's four ports: the Input Port, the Display Port, the Overlay Port, and the Host Interface Port.

### 5.2.1. Input Port Clock

The Input Port is divided into the VGA Port and the VGB Port.

### 5.2.1.1. VGACLK & VGACREF - VGA Input Port (RGB Data)

The VGACLK signal provides the master clock for the VGA Input Port. This clock supports operating speeds up to 84 MHz. VGACLK synchronizes data on the input buses and the writing of data to the gmZ1. The active edge of VGACLK is programmable through the host interface.

The VGACREF (VGA Port Clock Reference) signal provides a clock by clock enable (or stall) capability when transferring data and control information into the VGA Input Port. VGACREF must be asserted during the selected edge of VGACLK for control and data information to be sampled.

### 5.2.1.2. VGBCLK & VGBCREF - VGB Input Port (YUV or RGB Data)

VGBCLK is the master clock for the VGB Input Port, which accepts YUV or RGB data. This clock is connected to a 1X or 2X pixel clock in the external system with operating frequencies up to a maximum of 45 MHz when in YUV mode, or 84 MHz when in RGB mode. The active edge of VGBCLK is programmable through the Host Interface.

The VGBCREF (VGB Port Clock Reference) signal provides a clock-by-clock enable (or stall) capability when transferring data and control information into the VGB Input Port. VGBCREF must be asserted during the selected edge of VGBCLK to enable the sampling of control and data information.

### 5.2.2. Display Port Clock

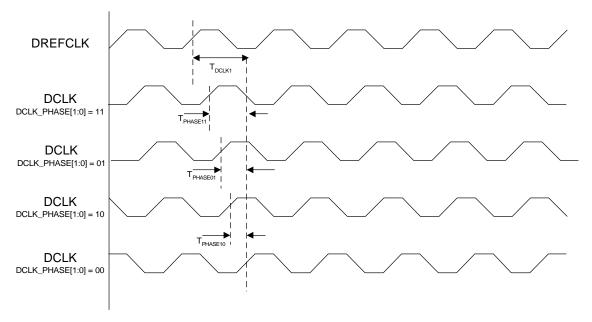

### 5.2.2.1. DREFCLK1 DREFCLK2, DCLK and DHCLK

Two separate display reference clocks (DREFCLK1 and DREFCLK2) are supported to allow systems to easily integrate both a free-running crystal oscillator and an external Phase Lock Loop (PLL) generated clock for display timing. The PLL display clock can be synchronized to the external video input to achieve frame lock through clock synchronization.

DREFCLK1: This clock input is driven by an external free running crystal oscillator source and is the default clock source during power-up-reset. *It must always be driven by a free-running clock for the gmZ1 device to reset properly.*

DREFCLK2: This clock input is driven from an external crystal oscillator source or PLL. The gmZ1 can be programmed to use DREFCLK2 as the display timing master clock by setting the HOSTCTRL: DREFCLK2\_EN control bit.

DREFCLK1 and DREFCLK2 control all display timing. A buffered version of the enabled clock is output on the DCLK pin. A separate DHCLK signal operating at half the DCLK rate is output and available to systems using Double Pixel Mode.

The Display Port data and control outputs are sampled by any external device using the DCLK and DHCLK outputs. These clocks provide controlled set-up and hold times for sampling the data outputs. The DCLK and DHCLK active edge (rising/falling) is programmable and the clock phase relative to the data and control outputs is also software controlled. By default, DCLK and DHCLK are rising-edge aligned to the data and control outputs. (DCLK leads DHCLK which in turn leads the state changes on the control and data outputs to provide finite hold times for external devices.)

### 5.2.3. Overlay Port Clock

The overlay clock output, OVCLK, operates at the same frequency as DHCLK (one half of the display pixel clock rate) and must be used as the clock for any off-chip overlay generation circuitry. This clock is used by external overlay generation circuitry to latch the gmZ1 overlay output control signals and to clock the overlay color select and enable control signals into the gmZ1.

### 5.2.4. Host Interface Port Clock

The Serial Clock (SCLK) must be provided by the external system to clock input and output serial data. The active edge is determined by the Serial Clock Polarity (SCLKPOL) pin. Address and data transfers are composed of sixteen pulses of SCLK framed by an asserted  $\overline{SCS}$  (Serial Chip Select). Each transfer cycle must consist of 16 SCLK cycles - valid control, address, or data bits must be provided with each SCLK.

# 5.3. Input Port

Table 2 summarizes the basic signal connections required for specific input data formats. The Reference Page gives the location of a detailed explanation for each item in this data sheet.

| Input Data<br>Format       | Pixel<br>Width                                          | Required Signals                                                                                                                                                                                                                                                                                                                                                                                        | Reference<br>Page |

|----------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| YUV Single<br>Pixel        | 16-bit                                                  | "VGB" Input Port: VGBCLK, VGBCREF, VGBHS, VGBVS,<br>VGBYIN[7:0] and VGBUVIN[7:0].<br>Input Port Control Signals: Use all signals.                                                                                                                                                                                                                                                                       | 16                |

| RGB "VGB"<br>Single Pixel  | 24-bit                                                  | "VGB" Input Port: Use all signals.<br>Input Port Control Signals: Use all signals                                                                                                                                                                                                                                                                                                                       | 16, 20            |

| RGB "VGA"<br>Single Pixel  | 24-bit                                                  | "VGA" Input Port: Use all signals.<br>Input Port Control Signals: Use all signals                                                                                                                                                                                                                                                                                                                       | 22, 24            |

| RGB Double<br>Pixel        | 48-bit                                                  | <ul> <li>"VGA" Input Port: Use all signals. This port supports the 24-bits (Left pixel) of each 48-bit pixel pair.</li> <li>"VGB" Input Port: Use VGBRED[7:0], VGBGRN[7:0], VGBBLU[7:0]. This port supports the 24-bits (Right pixel) of each 48-bit pixel pair. This port is clocked and controlled by the VGA clock/control signals.</li> <li>Input Port Control Signals: Use all signals.</li> </ul> | 22, 25            |

| RGB Double<br>Pixel Offset | bit nivel pair. Pivels are latched when VGACREE - $(1)$ |                                                                                                                                                                                                                                                                                                                                                                                                         | 22, 26            |

Table 2: Summary - I/O Interfacing to gmZ1

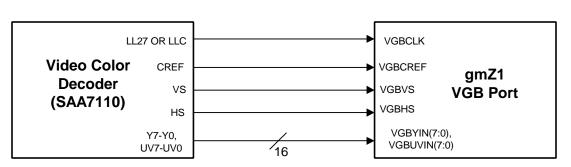

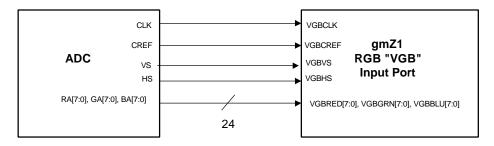

### 5.3.1. VGB Input Port

The VGB Input Port supports interlaced and non-interlaced data streams and provides an easy direct connection to most common color decoder chips. As an example, a glueless connection from the Philips SAA7110 color decoder to the gmZ1 VGB Input Port is shown in Figure 4.

The VGB Input Port supports video timing for square pixel and CCIR601 formatted NTSC/PAL/SECAM, as well as non-standard data streams. The VGB port supports YUV and RGB data formats.

Figure 4: Video Color Decoder Connection to gmZ1

The gmZ1 always uses an even number of active Y and UV samples per line. Odd numbers of active samples are not supported, however the total number of pixel clocks (blanking and active) per line can be an odd value.

### 5.3.1.1. VGB Port I/O Signals (YUV Data)

### VGBVS

The VGB Input Port samples VGBVS (VGB Port Vertical Sync) during qualified VGBCLK cycles, i.e. when VGBCREF is asserted during an active VGBCLK edge. When VGBVS assertion is detected, the gmZ1 begins processing a new input field. The VGBVS active state is programmable via the HOSTCTRL register.

### VGBHS

The VGB Input Port samples VGBHS (VGB Port Horizontal Sync) during qualified VGBCLK cycles. Upon VGBHS assertion, the VGB Input Port prepares for the next incoming line of video data. The VGBHS active state is programmable via the HOSTCTRL register.

*Note:* VGBHS can be used to stall the gmZ1 on a "line-by-line" basis.

### VCODD

The VCODD signal (Input ODD Field Indicator) determines the vertical start location of the active window. For interlaced video sources, VCODD selects one of two programmable vertical start locations. For non-interlaced video sources, this signal is ignored and all input frames are treated as "ODD" fields. VCODD is common to the VGB and VGA Input Ports.

VCODD must be valid during each field/frame's first active VGBHS pulse as defined by the IPV\_STARTODD or IPV\_STARTEVN programmable registers. Since VCODD determines the field polarity, it must assume its correct state before the lesser of the start odd or start even values. VCODD must remain valid for the entire vertical active region, i.e. during all active lines. The VCODD active state is programmable via the register set. (By default, VCODD = '1' indicates odd fields.)

# VCBLNK

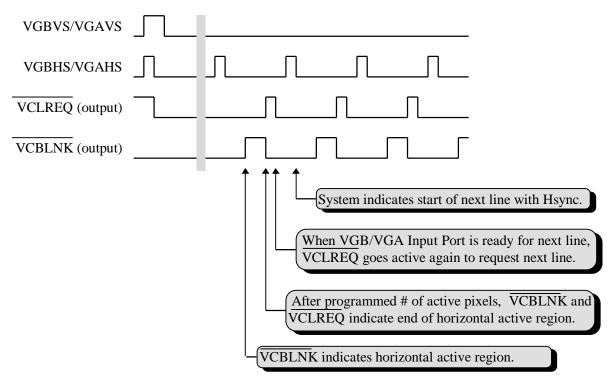

VCBLNK (Input Port Composite Blanking Indicator) indicates that the gmZ1 device is sampling pixels in the Active Display Window region. This signal frames the active region when the gmZ1 accepts pixel data for zoom processing. This signal is common to the VGB/VGA Input Ports.

When required, the external system should sample  $\overline{\text{VCBLNK}}$  during qualified clock edges (i.e. during a valid combination of VGBCLK edge and VGBCREF state).  $\overline{\text{VCBLNK}}$  is de-asserted two qualified pixel clocks before the first input data is sampled, and can be used as a pixel request signal.

For applications where the external system is providing VGB Input Port data from a memory storage buffer (i.e. frame buffer, FIFO), the predictive blanking signal allows the system one qualified clock edge to sample  $\overline{\text{VCBLNK}}$ , and the next qualified clock edge to output data to the VGB Port. This data is then sampled on the subsequent qualified clock edge by the gmZ1. For applications where the external system is providing free-running video and control signals to the Input Port, the  $\overline{\text{VCBLNK}}$  signal does not provide any controlling function, but can be used to monitor the active samples accepted by the VGB Input Port.

### VCLREQ

The Line Request,  $\overline{\text{VCLREQ}}$  output signal that indicates the gmZ1 is ready for input video lines. This signal is common to the VGA/VGB Input Port.

If the external system is providing a free-running video source to the VGB Port, the  $\overline{\text{VCLREQ}}$  signal is not typically utilized, since the flow of video data and control information cannot be stalled. However,  $\overline{\text{VCLREQ}}$  can be monitored to determine the input lines accepted by the VGB Input Port.

If the external system is providing source data and control information from a memory device without periodic video line timing, the gmZ1 de-asserts  $\overline{\text{VCLREQ}}$  at the end of each active video line until the VGB Port is ready for the next line.  $\overline{\text{VCLREQ}}$  is always de-asserted between input video lines to stall the flow of input data while the gmZ1 is flushing internal pipelines. When  $\overline{\text{VCLREQ}}$  is asserted to request the next input line, the system should always provide a VGBHS to initialize the gmZ1 for the next line. VGBHS should be followed by the programmed amount of blanking and valid data.

Once asserted to request data,  $\overline{\text{VCLREQ}}$  will remain asserted until the programmed number of pixels have been transferred into the VGB Port.  $\overline{\text{VCLREQ}}$  and  $\overline{\text{VCBLNK}}$  are intended to be utilized by system frame buffer controllers to provide high-speed pipelined image/video data interfaces with minimal external glue logic.

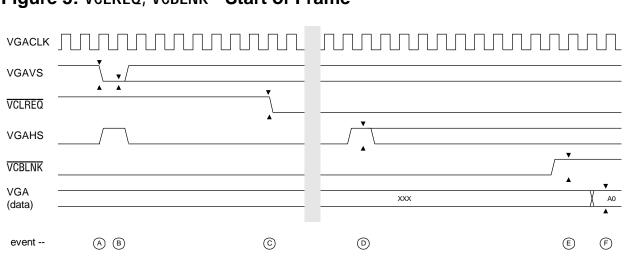

A - VSYNC occurs

B - VGA Port samples VGAVS to detect start of first line of a new field or frame. GmZ1 internal line # set to 1.

C - VCLREQ is asserted nine clocks after VGAVS assertion.

D - gmZ1 reaches vertical active region start value (IPV\_ACTIV\_STARTODD, IPV\_ACTIV\_STARTEVN)

E - VGA Port indicates pending start of active region, 2 pixels before IPH\_ACTIV\_START.

F - VGA Port samples first pixel of first line of frame. There are IPH\_ACTIV\_WIDTH active pixel samples per active line.

Note: VGAVS is programmed active low, VGAHS is programmed active high.

# Figure 6: VCLREQ Operation

| Figure 7: VCLREQ Operatior | During End of Frame/Field |

|----------------------------|---------------------------|

|----------------------------|---------------------------|

| VGBVS/VGAVS                                                                                 |

|---------------------------------------------------------------------------------------------|

| VGBHS/VGAHS                                                                                 |

| VCLREQ (output)                                                                             |

| VCBLNK (output)                                                                             |

| System indicates start of last active line with Hsync.                                      |

| After programmed # of valid pixel clocks,<br>VCBLNK indicates start of horz. active region. |

| After programmed # of active pixels,<br>VCBLNK indicates end of horz. active region.        |

| VCLREQ goes inactive - end of image.                                                        |

| VGACLK                                                                                      |

| VCLREQ                                                                                      |

| VCBLNK                                                                                      |

| After VS leading edge is detected, VCLREQ requests lines of data for next frame or field.   |

#### 5.3.1.2. VGB Port I/O Signals (RGB Data)

The VGB port supports RGB single pixel data on its own (up to 84MHz data rates), or doublepixel data streams in combination with the VGA port. The VGA port is described beginning with section 5.3.2. A connection to an RGB single-pixel source is shown below in Figure 8.

## Figure 8: Single Pixel Mode - VGB Port Interfacing

The functionality of the control signals is identical whether the VGB port is processing YUV or RGB data.

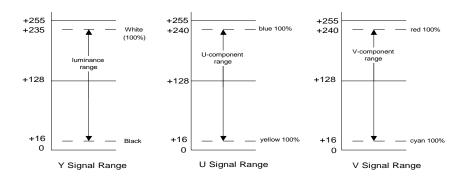

### 5.3.1.3. Data Format

YUV input data is accepted through an 8-bit Y channel, and an 8-bit multiplexed UV (or Cb, Cr) channel. UV data is sub-sampled using standard 4:2:2 sampling. Y data values can be full range 0 - 255; however, they will be clamped by internal circuitry to be in the CCIR601 range (16 to 235). UV data values can be full range 0 - 255; however, they will be clamped by internal circuitry to be in the range 16 to 240. See Figure 9. The VGB port also accepts full scale RGB data on the VGBRED, VGBGRN, and VGBLU buses. *The gmZ1 contains a color space converter that always transforms 4:2:2 YUV data to 24-bit RGB*.

R = 1/256 [298Y + 409V - 57014] G = 1/256 [298Y - 100U - 208V + 34692] B = 1/256 [298Y + 517U + 1V - 70964]Cb = U, Cr = V

### Figure 9: CCIR 601 Signal Range

### 5.3.2. VGA Input Port

The VGA Input Port accepts real-time video graphics data and control signals (HSYNC, VSYNC, Pixel clock, Clock Qualifier). The VGA Input Port supports interlaced and non-interlaced video data streams with three different input modes: Single-Pixel, Double-Pixel and Double-Pixel-Offset.

### 5.3.2.1. VGA Port I/O Signals

### VCODD

The VCODD signal (Input ODD Field Indicator) determines the vertical start location of the active window. For interlaced video sources, VCODD selects one of two programmable vertical start locations. For non-interlaced video sources, this signal is ignored and all input frames are treated as "ODD" fields. VCODD is common to the VGB and VGA Input Ports.

VCODD must be valid during each field/frame's first active VGAHS pulse as defined by the IPV\_STARTODD or IPV\_STARTEVN programmable registers. Since VCODD determines the field polarity, it must assume its correct state before the lesser of the start odd or start even values. VCODD must remain valid for the entire vertical active region i.e. during all active lines. The VCODD active state is programmable via the register set. (By default, VCODD = '1' indicates odd fields.)

### VCBLNK

VCBLNK (Input Port Composite Blanking Indicator) indicates that the gmZ1 device is sampling pixels in the Active Display Window region. This signal frames the active region when the gmZ1 accepts pixel data for zoom processing. This signal is common to the VGB/VGA Input Ports.

When required, the external system should sample VCBLNK during qualified clock edges (i.e. during a valid combination of VGBCLK edge and VGBCREF state).  $\overline{\text{VCBLNK}}$  is de-asserted two qualified pixel clocks before the first input data is sampled, and can be used as a pixel request signal.

For applications where the external system is providing VGA Input Port data from a memory storage buffer (i.e. frame buffer, FIFO), the predictive blanking signal allows the system one qualified clock edge to sample  $\overline{\text{VCBLNK}}$ , and the next qualified clock edge to output data to the VGA Port. This data is then sampled on the subsequent qualified clock edge by the gmZ1. For applications where the external system is providing free-running video and control signals to the Input Port, the  $\overline{\text{VCBLNK}}$  signal does not provide any controlling function, but can be used to monitor the active samples accepted by the VGB Input Port.

### VCLREQ

The Line Request,  $\overline{\text{VCLREQ}}$  output signal indicates the gmZ1 is ready for input video lines. This signal is common to the VGA/VGB Input Port.

For applications where the external system is providing a free-running video source to the VGA Port, the  $\overline{\text{VCLREQ}}$  signal is not typically utilized, since the flow of video data and control information cannot be stalled. However,  $\overline{\text{VCLREQ}}$  can be monitored to determine the input lines accepted by the VGA Input Port.

If the external system is providing source data and control information from a memory device without periodic video line timing, the gmZ1 de-asserts  $\overline{\text{VCLREQ}}$  at the end of each active video line until the VGA Port is ready for the next line.  $\overline{\text{VCLREQ}}$  is always de-asserted between input video lines to stall the flow of input data while the gmZ1 is flushing internal pipelines. When  $\overline{\text{VCLREQ}}$  is asserted to request the next input line, the system should always provide a VGAHS to initialize the gmZ1 for the next line. VGAHS should be followed by the desired number of blanking and valid data.

Once asserted to request data, VCLREQ will remain asserted until the programmed number of pixels have been transferred into the VGA Port.  $\overrightarrow{\text{VCLREQ}}$  and  $\overrightarrow{\text{VCBLNK}}$  are intended to be utilized by system frame buffer controllers to provide high-speed pipelined image/video data interfaces with minimal external glue logic. See Figure 6 and Figure 7.

### 5.3.2.2. Data Format

The VGB port supports single pixel width (24 bit) and double pixel width (48 bit transfers). Each pixel consists of 8 bits for each color component: R (Red), G (Green), and B (Blue). Individual Red, Green, and Blue data values are full range 0 - 255.

### Figure 10: Data Range

#### 5.3.2.3. Pixel Width Control

The three available pixel modes are selected by the IPCTRL register and IP2PIXWIDE\_EN and IP2PIXOFFSET\_EN bits.

### Figure 11: Pixel Width Mode

| Mode                  | IP2PIXWIDE_EN | IP2PIXOFFSET_EN | RGB_B_SEL | IP_RGB_EN |

|-----------------------|---------------|-----------------|-----------|-----------|

| Single Pixel VGA Port | 0             | 0               | 0         | 1         |

| Single Pixel VGB Port | 0             | 0               | 1         | 1         |

| Double Pixel          | 1             | 0               | 0         | 1         |

| Double Pixel Offset   | 0             | 1               | 0         | 1         |

| YUV Single Pixel      | 0             | 0               | 0         | 0         |

### Figure 12: Single Pixel - RGB "VGA" Port Interfacing

In this mode, the Horizontal Active Window is programmable in single pixel increments. The sync and control signals are sampled by the gmZ1 every pixel clock when the pixel clock qualifier (VGACREF) is active. 24-bit RGB data is transferred into the gmZ1 only when VGACREF is asserted during the "active" region as indicated by  $\overline{\text{VCBLNK}}$ . There is a two clock latency between  $\overline{\text{VCBLNK}}$  being de-asserted and data being accepted by the gmZ1.

- VGAVS (VGA Port Vertical Sync) is sampled during the selected edge of VGACLK when VGACREF is active.

- VGAHS is sampled during the selected edge of VGACLK when VGACREF is active.

## Figure 13: RGB Single Pixel Timing

Note: There is a two clock latency between the de-assertion of  $\overline{\text{VCBLNK}}$  and the gmZ1 accepting data. There is also a two clock latency at the end of a line between assertion of  $\overline{\text{VCBLNK}}$  and the last data sample accepted by the gmZ1.

5.3.2.3.2. Double Pixel Mode

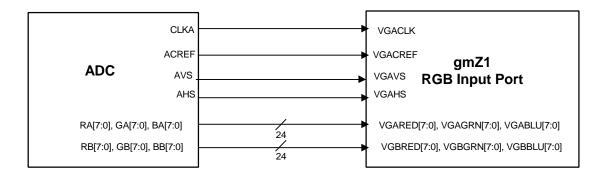

### Figure 14: Double Pixel - VGA and VGB Ports Interfacing

In this mode, the Horizontal Active Window is programmable in double pixel increments. The gmZ1 samples the sync and control signals every pixel clock when the pixel clock qualifier (VGACREF) is active. Note that only pixel clocks where VGACREF is active are counted. Both the VGA and VGB buses are sampled on every qualified pixel clock during the active region indicated by the  $\overline{\text{VCBLNK}}$  signal.

Note that the maximum transfer rate is one pixel pair every two pixel clocks. VGACREF must be inactive for at least 1 clock period every other pixel clock. Data is not sampled when the pixel

clock qualifier is in-active. Therefore in Double Pixel Mode the sync inputs always correspond to 2 pixels.

- VGAVS (VGA Port Vertical Sync) is sampled during the selected edge of VGACLK when VGACREF is active.

- VGAHS is sampled during the selected edge of VGACLK when VGACREF is active

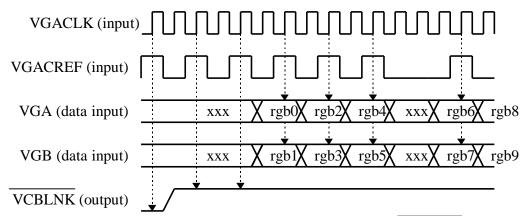

### Figure 15: RGB Double Pixel Timing

Note: There is a two clock latency between the de-assertion of  $\overline{\text{VCBLNK}}$  and the gmZ1 accepting data. There is also a two clock latency at the end of a line between the assertion of  $\overline{\text{VCBLNK}}$  and the last data sample accepted by the gmZ1.

### 5.3.2.3.3. Double Pixel Offset Mode.

In this mode, the Horizontal Active Window is programmable in single pixel increments. The sync and control signals are sampled by the gmZ1 every pixel clock, independently of the pixel clock qualifier (VGACREF) state. All pixel clocks are counted.

Pixel data on the VGA bus (24 bit RGB) is transferred into the gmZ1 on each rising edge of pixel clock while VGACREF is active. Pixel data on the VGB (24-bit RGB) is transferred into the gmZ1 on rising edge of the pixel clock while VGACREF is NOT active. The VGACREF active state is programmable to allow the interchanging of A and B Port transfers. The pixel clock qualifier acts as a pixel A/B select for systems providing double width pixel data in a "ping-pong" fashion. Note that the pixel transfer rate is one pixel pair every two pixel clocks and the pixel clock qualifier must be half the pixel clock frequency.

• VGAVS (VGA Port Vertical Sync) and VGAHS are sampled during the selected edge of VGACLK. (Not dependent on the state of VGACREF).

# Figure 16: RGB Double Pixel Offset Timing #1

### Figure 17: RGB Port Double Pixel Offset Timing #2

*Note:* In Figure 16 and Figure 17 there is a two clock latency between the de-assertion of  $\overline{VCBLNK}$  and the gmZ1 accepting data. This latency also holds true at the end of a line, between the assertion of  $\overline{VCBLNK}$  and the last data sampled.

### 5.3.3. Operating Modes

The gmZ1 operates in several modes: No Zoom, Standard Zoom and De-Interlacing Zoom. These modes will either allow the data to "pass-through" (i.e. the output data will be identical to

the input or the de-interlaced input), data will be zoomed (magnified), or the interlaced data will be de-interlaced and possibly zoomed.

### 5.3.3.1. No Zoom Mode

In No Zoom mode, the input image data passes through the gmZ1 unchanged. The number of active pixels per line and the number of active lines per frame remains unchanged. However, the data crosses clock boundaries from the input video pixel clock to the display pixel clock.

No Zoom mode is enabled when the input and output active windows are the same size, i.e. register values for the Input Video Register are equal:

IPH\_ACTIV\_WIDTH = DH\_ACTIV\_WIDTH

IPV\_ACTIV\_LNGTH = DV\_ACTIV\_LNGTH

No Zoom mode also requires the horizontal and vertical scaling values to be set to zero, i.e.  $Z_HORZ_SV = 0$  and  $Z_VERT_SV = 0$ .

### 5.3.3.2. Standard Zoom Mode

This mode is used to magnify non-interlaced data, i.e. graphics. Input image data may be magnified both vertically and horizontally - the vertical and horizontal zoom ratios are independently adjustable. The zoom ratio is set by programming the input active window parameters to the source image size, and by programming the display active window parameters to the required output image size. The Z\_HORZ\_SV and Z\_VERT\_SV registers must be programmed for zoom operation.

### DH\_ACTIV\_WIDTH > IPH\_ACTIV\_WIDTH DV\_ACTIV\_LNGTH > IPV\_ACTIV\_LNGTH

### 5.3.3.3. De-Interlacing Zoom Mode

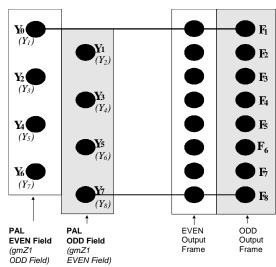

This mode is used to spatially de-interlace input data, i.e. video. Every input field is magnified to the output frame resolution, however, the even and odd fields have different fractional vertical offsets applied to properly map the two input fields into the non-interlaced output frame. This ensures the fields are correctly aligned in the output frame and eliminates interlacing artifacts.

### 5.3.3.3.1. NTSC Video

The spatial de-interlacing process assumes the ODD field is always mapped spatially higher than the EVEN field, which is true for NTSC video sources. No special operations are required by the user to handle NTSC video.

### Figure 18: NTSC De-Interlacing Zoom

5.3.3.3.2. PAL

For PAL sources, the ODD field is mapped spatially lower than the EVEN field. Since the gmZ1 always maps input fields spatially higher when VCODD is active, the PAL definition of ODD can be accommodated by inverting the VCODD "active" state through the IPCTRL register IPODD\_INV control bit.

IPODD\_INV should be programmed so that the VCODD active state corresponds with input fields mapped spatially higher in the output frame. Also the IPV\_ACTIV\_STARTODD control register should be loaded with the vertical start location of the spatially higher input field. The IPV\_ACTIV\_STARTEVN control register should be loaded with the spatially lower input field.

Figure 19: PAL De-Interlacing Zoom

#### where

$IPV\_ACTIV\_STARTODD = Y_0$  $IPV\_ACTIV\_STARTEVN = Y_1$

The EVEN field is mapped spatially higher by inverting the VCODD active state in the IPCTRL register.

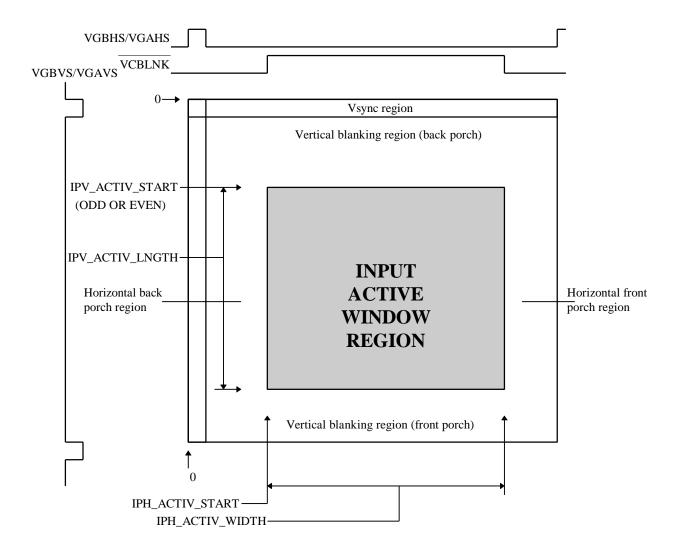

### 5.3.4. Input Active Window Control

The Input Active Window Control provides a means for programming the active window region for the selected input video on either the VGA or VGB Input Port. The horizontal sync and vertical sync controls are used from the selected port to determine the active window region. Only pixels transferred into the device during the Active Window region are used as source data for the scaling process and resulting display output. The Active Window is defined using registers IPV\_ACTIV\_STARTODD, IPV\_ACTIV\_STARTEVN, IPV\_ACTIV\_LNGTH, IPH\_ACTIV\_START, and IPH\_ACTIV\_WIDTH.

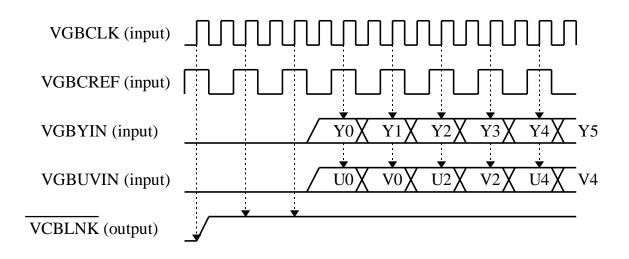

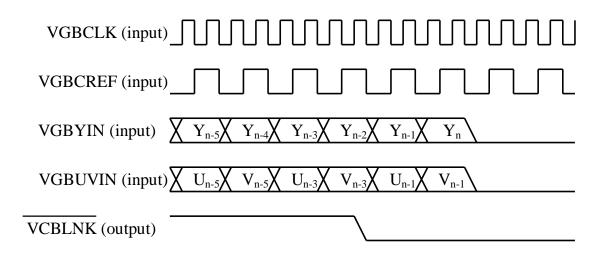

During single pixel mode, the Horizontal Active Window is programmable in single pixel increments. Note that only qualified pixel clocks (i.e. when VGACREF or VGBCREF is asserted) are counted. When processing YUV inputs, the active region is programmable in single pixel increments, however an even number of active pixels per line should always be used. Note that only pixel clocks where VGBCREF is active are counted.

For interlaced video, VCODD determines which of two possible Vertical Active Region start locations will be used.

### Figure 20: YUV Data Start of Active Window

# Figure 21: YUV Data End of Active Window

During the double pixel mode, the active region is programmable in double pixel increments. Note that only pixel clocks where VGACREF is active are counted.

During the double pixel offset mode, the active region is programmable in single pixel increments. However, all pixel clocks are counted regardless of the state of VGACREF.

# 5.4. RGB Output Port

The RGB Output Port sends zoomed video data and control signals to an external display or storage device. This port controls several functions such as data transfer (single/double pixel) and generating the output timing to synchronize the data with the display timing. The RGB Output Port will also support display devices with 6 bits per color, using dithering circuitry which can be enabled by setting the DOUTCNTRL: D\_18BIT\_EN control bit. Dithering prevents contouring or banding in the display output as a result of the reduced display color resolution. The 6-bit rounding circuitry is optimized to prevent line by line correlation (vertically) and frame by frame correlation (temporally).

# **5.4.1. Data Transfer Modes**

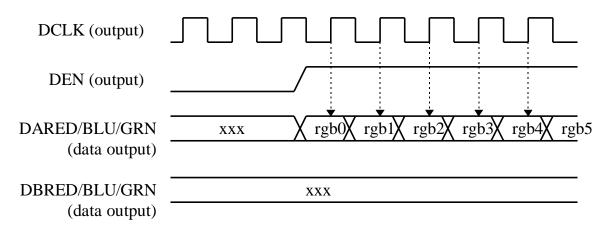

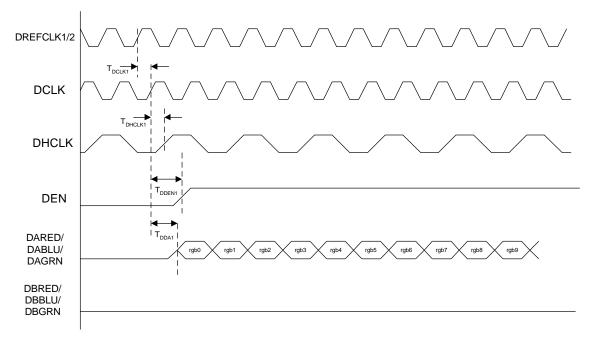

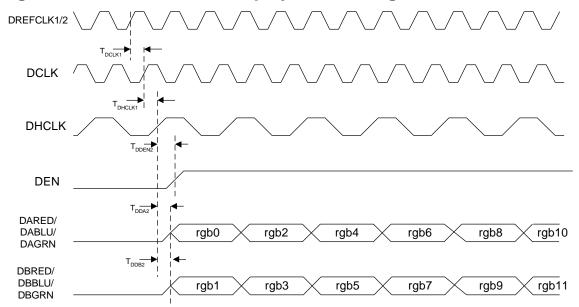

### 5.4.1.1. Single Pixel Mode

Single pixel data (24-bit RGB) is transferred to display port 'A' (DARED/BLU/GRN) on each active edge of DCLK. Note that the DHCLK signal phase may vary from line to line depending on the line length and Display Synchronization Mode. Normally DHCLK is not used by the external system in this mode. The sync and controls are transferred to display port outputs on each active edge of DCLK. This mode can be selected by programming the DOUTCNTRL register.

# Figure 23: Display Data Timing Single Pixel Mode

*Note:* DCLK and DEN polarity are independently programmable within the gmZ1.

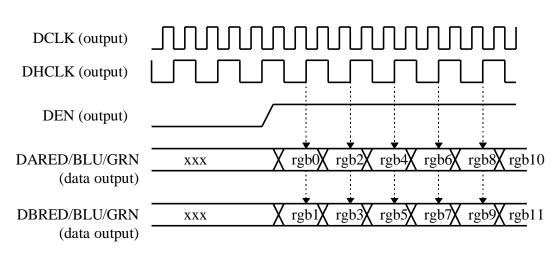

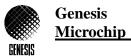

#### 5.4.1.2. Double Pixel Mode

GENESIS

Double width pixel data (48-bit RGB), sync, and control information are transferred to the display port outputs on alternate DCLKs. The transfers are synchronized with the half rate clock, DHCLK. DHCLK can be programmed to be rising or falling edge aligned with the data transfers. DHCLK can also be adjusted in <sup>1</sup>/<sub>4</sub> cycle increments relative to data/control transfers. This mode can be selected by programming the DOUTCNTRL register.

# Figure 24: Display Data Timing Double Pixel Mode

Note: DCLK, DHCLK, and DEN polarity are all independently programmable.

# 5.4.2. Programmable Input Lock Event

The Lock Event is a programmable point in time, where the Display Timing Generator synchronizes the input video source and display output frame timing with a programmable amount of phase skew between them. The phase skew between the input and output frame is programmable to optimize the usage of the on chip zoom buffer, i.e. prevent zoom buffer overflow/underflow. The lock event is set through registers IPH\_LOCK\_EVENT and IPV\_LOCK\_EVENT. It occurs once per input frame, during any specified pixel location and can be disabled by setting the IPH\_LOCK\_EVENT and IPV\_LOCK\_EVENT registers to zero. For Interlaced video sources the LOCK\_EVENT occurs during the ODD fields but not during the EVEN fields. Lock Events can also be generated externally by the system using the DFSYNC pin (this requires the DFSYNC\_EN control bit to be set).

# 5.4.3. D\_BYPASS Mode

An additional "Bypass" mode is supported within Double Pixel Mode. D\_BYPASS Mode transfers the VGA Input Port data and sync inputs directly to the display output port at the input clock rate. There is no processing of the data stream, no zoom operations supported, and the overlay is bypassed (not supported) as well.

### 5.4.3.1. Mode Selection

D\_BYPASS Mode is only supported when the VGA Port is programmed as the input port, interlaced operation is disabled, the input data format is "Double Width Pixel Mode", and No Zoom mode is selected (see Section 5.3.3.1). When all of the above are true, D\_BYPASS Mode can be selected by setting the HOSTCTRL register: D\_BYPASS\_EN control bit to '1'.

### 5.4.3.2. Output Signals

During D\_BYPASS Mode the DCLK output is driven by a buffered version of the VGA Port VGACLK input. The DHCLK output is driven by a pipelined version of the VGACREF signal that aligns with the data output delay. The DCLK and DHCLK signals can still be inverted under software control using the DOUTCNTRL register.

The DEN signal is driven with a pipelined version of the Input Port Composite Blanking Indicator ( $\overline{\text{VCBLNK}}$ ) output signal, compensated with pipeline delays to align with the display output data.

The display output data is driven with a delayed version of the VGA Port input data clocked out of the Display Port as shown in Figure 25. Note the VGARED/BLU/GRN inputs are transferred to the DARED/BLU/GRN outputs. The VGBRED/BLU/GRN inputs are transferred to the DBRED/BLU/GRN outputs.

| The input signal    | Becomes the output signal |

|---------------------|---------------------------|

| VGA port input data | DA port display data      |

| VGB port input data | DB port display data      |

| VCBLNK              | DEN                       |

| V CRE               | DHCLK                     |

| VGACLK              | DCLK                      |

Table 3: Corresponding Input/Output Signals in D\_BYPASS

*Note:* DCLK, DHCLK and DEN polarity are independently programmable.

### **5.4.4.** Display Timing Generation

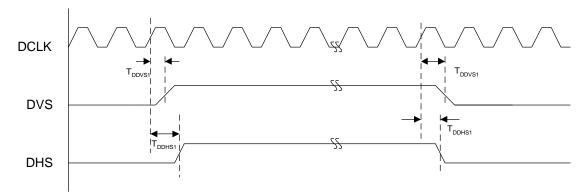

The Display Timing Generator supports four display synchronization modes. The display synchronization mode is selected through the Host Interface DCONTROL register.

| Free Run Mode:   | supports frame buffers; frame-rate conversion applications        |

|------------------|-------------------------------------------------------------------|

| Frame Sync Mode: | forced synchronization of input and output frame periods          |

| Line Sync Mode:  | display line rate synthesized from input line rate and the forced |

|                  | synchronization of input and output frame periods                 |

| Clock Sync Mode: | system-supplied display clock tracks input clock                  |

|                  | - Clock Sync Mode is not recommended since there is no            |

|                  | continuous forced synchronization of input and output frame       |

|                  | periods.                                                          |

| Register:<br>DCONTROL | Free Run<br>Mode | Frame<br>Sync Mode | Line Sync<br>Mode | Clock Sync<br>Mode |

|-----------------------|------------------|--------------------|-------------------|--------------------|

| D_LINESYNC_EN         | 1                | 0                  | 1                 | 0                  |

| D_FRAMELOCK_EN        | 1                | 1                  | 0                 | 0                  |

# Table 4: Display Timing Generation: Synchronization Modes

#### 5.4.4.1. Free-Run Mode

This mode is used in systems that can synchronize the source data with free-running display timing. Such systems typically have an external frame buffer containing source data, and can provide data to the selected input port as requested by the  $\overline{\text{VCLREQ}}$  and  $\overline{\text{VCBLNK}}$  signals.

#### 5.4.4.1.1. Synchronization & Latency

In this mode there is no display start-up synchronization performed by the gmZ1 device. The display timing begins when the DCONTROL: DTG\_RUN\_EN control bit is set. The external system must determine when to initialize to the start of a new frame. This can be accomplished by monitoring the gmZ1 Display Port DVS (Display VSYNC) or the  $\overrightarrow{OVSYNC}$  (Overlay VSYNC) outputs. The external system must provide input data to the gmZ1 as requested by  $\overrightarrow{VCLREQ}$

and VCBLNK at sufficient rates to sustain the zoomed video display output.

The DFSYNC input pin and the programmable LOCK\_EVENT are ignored, so there is no mechanism within the gmZ1 for synchronizing the DTG (Display Timing Generator) with the input source video.

Any loss of synchronization between the input pixel/line rate and the display zoomed line rate will result in variations between the input active frame period and the display active frame period. This can cause the on-chip zoom buffer to over or under flow.

### 5.4.4.2. Frame Sync Mode

This mode is used when the system can generate a display pixel clock that is synchronized to the input pixel clock, thereby allowing the display line rate to be synchronized with the input line rate.

Internally the rate that input lines are absorbed for zoom processing, closely matches the input line rate.

The display pixel clock must be generated through an external PLL and the input pixel clock must be an integer multiple of the input line rate (i.e. line-locked).

This mode can also be used with system containing an external Frame Buffer. In this case, the Frame Buffer supplies input lines are requested through the  $\overline{\text{VCLREQ}}$  and  $\overline{\text{VCBLNK}}$  signals.

The display frame rate is forced to match the input frame rate by means of LOCK\_EVENT synchronization. (For interlaced video, the output frame rate matches the input frame rate.)

#### 5.4.4.2.1. Synchronization & Latency

Display start-up synchronization occurs whenever the DCONTROL: DTG\_RUN\_EN control bit is set, i.e. transitions from a '0' to a '1'. This forces the DTG to wait until either a programmable LOCK\_EVENT is detected in the selected input video source timing or the  $\overrightarrow{DFSYNC}$  pin is asserted. Either of these events causes the DTG to immediately transition to the display timing state selected by the DH\_LOCK\_LD and DV\_LOCK\_LD register values.

The display output line rate is determined from the selected external display reference clock (normally DREFCLK2). If the input data is not provided from an external frame buffer then the display reference clock must track variations in the selected input video pixel clock. The DTG is then also be programmed so that the display output frame is equal to the input video frame period.