# **VOLTAGE REGULATOR PLUS FILTER**

PRELIMINARY DATA

- FIXED OUTPUT VOLTAGE 8.5V

- 250mA OUTPUT CURRENT

- HIGH RIPPLE REJECTION

- HIGH LOAD REGULATION

- HIGH LINE REGULATION

- SHORT CIRCUIT PROTECTION

- THERMAL SHUT DOWN WITH HYSTERESIS

- DUMP PROTECTION

This circuit combines both a filter and a voltage regulator in order to provide a high ripple rejection over a wider input voltage range.

A supervisor low-pass loop of the element prevents the output transistor from saturation at low input voltages.

The non linear behaviour of this control circuitry allows a fast settling of the filter.

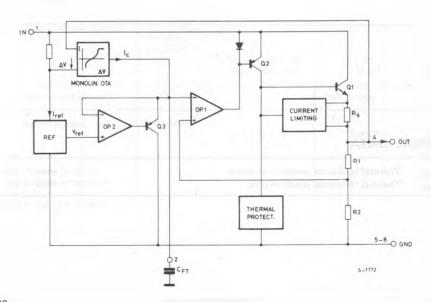

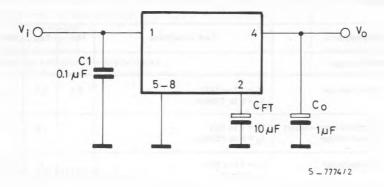

### BLOCK DIAGRAM

## ABSOLUTE MAXIMUM RATINGS

| VI                                | Peak input voltage (300 ms)      | 40                 | V  |

|-----------------------------------|----------------------------------|--------------------|----|

| V <sub>i</sub>                    | DC input voltage                 | 28                 | V  |

| I <sub>o</sub>                    | Output current                   | internally limited |    |

| P <sub>tot</sub>                  | Power dissipation                | internally limited |    |

| T <sub>stq</sub> , T <sub>i</sub> | Storage and junction temperature | -40 to 150         | °C |

|                                   |                                  |                    |    |

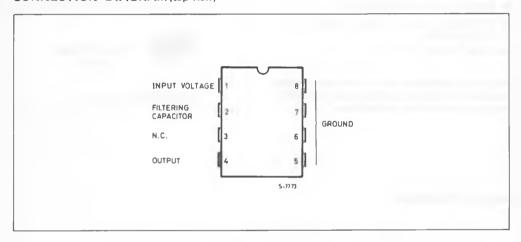

# CONNECTION DIAGRAM (top view)

#### THERMAL DATA

| Thermal resistance junction-ambient Thermal resistance junction pins | <br>80<br>20 | °C/W |

|----------------------------------------------------------------------|--------------|------|

|                                                                      |              |      |

**ELECTRICAL CHARACTERISTICS** ( $T_{amb} = 25^{\circ}C$ ,  $V_{i} = 13.5V$ , Test circuit of fig. 1, unless otherwise specified)

|                               | Parameter                               | Test Condition                                                                                               | ns                            | Min. | Тур.         | Max. | Unit     |

|-------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------|------|--------------|------|----------|

| Vi                            | Input voltage                           |                                                                                                              |                               |      |              | 20   | V        |

| Vo                            | Output voltage                          | V <sub>I</sub> = 12 to 18V<br>I <sub>O</sub> = 5 to 150mA                                                    |                               | 8.1  | 8.5          | 8.9  | V        |

| ΔV <sub>I/O</sub>             | Controlled input-output dropout voltage | V <sub>1</sub> = 5 to 10V<br>I <sub>0</sub> = 5 to 150mA                                                     |                               |      | 1.6          | 2.1  | ٧        |

| ΔV <sub>o</sub>               | Line regulation                         | V <sub>I</sub> = 12 to 18V<br>I <sub>o</sub> = 10m A                                                         |                               |      | 1            | 20   | mV       |

| ΔV <sub>o</sub>               | Load regulation                         | $l_0 = 5 \text{ to } 250\text{mA}$<br>$t_{OH} = 30\mu\text{s}$<br>$t_{Off} = \ge 1\text{ms}$                 |                               |      | 50           | 100  | mV       |

| ΔV <sub>o</sub>               | Load regulation<br>(filter mode)        | $V_1 = 8.5V$ $I_0 = 5 \text{ to } 150 \text{ m A}$ $t_{on} = 30 \mu \text{s}$ , $t_{off} = \ge 1 \text{ ms}$ |                               |      | 150          | 250  | mV       |

| Iq                            | Quiescent current                       | I <sub>0</sub> = 5m A                                                                                        |                               |      | 1            | 2    | mA       |

| ΔIq                           | Quiescent current change                | V <sub>I</sub> = 6 to 18V<br>I <sub>O</sub> = 5 to 150mA                                                     |                               |      | 0.05         |      | mA       |

| $\frac{\Delta V_o}{\Delta T}$ | Output voltage drift                    | I <sub>o</sub> = 10mA                                                                                        |                               |      | 1.2          |      | mV/°C    |

| SVR                           | Supply voltage rejection                | V <sub>lac</sub> = 1V <sub>rms</sub><br>f = 100Hz<br>I <sub>o</sub> = 150mA<br>V <sub>IDO</sub>              | ; = 12 to 18V<br>; = 6 to 11V |      | 70<br>35 (*) |      | dB<br>dB |

| Isc                           | Short circuit current                   |                                                                                                              |                               | 250  | 300          |      | mA       |

| T <sub>on</sub>               | Switch on time                          |                                                                                                              | 5 to 11V<br>11 to 18V         |      | 500 (*)      |      | ms<br>ms |

| Тј                            | Thermal shutdown junction temperature   |                                                                                                              |                               |      | 145          |      | °C       |

<sup>(\*)</sup> Depending of the CFT capacitor.

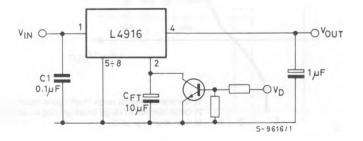

Fig. 1 - Test and Application Circuit

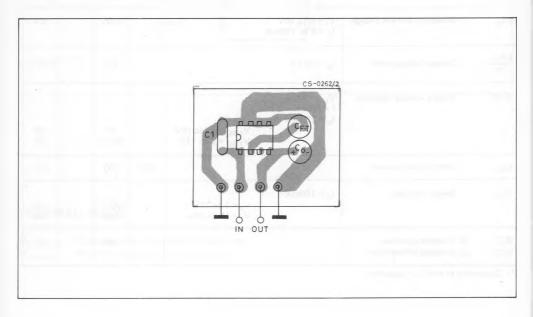

Fig. 2 - P.C. board and component layout of fig. 1 (1:1 scale)

## PRINCIPLE OF OPERATION

During normal operation (input voltage upper than  $V_{1\,MIN} = V_{OUT\,NOM} + \Delta V_{I/O}$ ). The device works as a normal voltage regulator built around the OP1 of the block diagram.

The series pass element use a PNP-NPN connection to reduce the dropout. The reference voltage of the OP1 is derived from a REF through the OP2 and Q3, acting as an active zener diode of value  $V_{\rm RFF}$ .

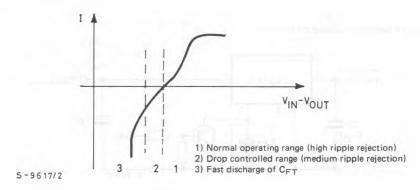

In this condition the device works in the range (1) of the characteristic of the non linear drop control unit (see fig. 3).

The output voltage is fixed to its nominal value:

$$V_{OUT NOM} = V_{REF} (1 + \frac{R1}{R2}) = V_{CFT} (1 + \frac{R1}{R2})$$

$$\frac{R1}{R2}$$

= INTERNALLY FIXED RATIO = 2.4

The ripple rejection is quite high (70 dB) and independent from  $C_{\text{FT}}$  value.

On the usual voltage regulators, when the input voltage goes below the nominal value, the regulation transistors (series element) saturate bringing the system out of regulation making it very sensible to every variation of the input voltage. On the contrary, a control loop on the L4916 consents to avoid the saturation of the series element by regulating the value of the reference voltage (pin 2). In fact, whenever the input voltage decreases below V<sub>MIN</sub> the supervisor loop, utilizing a non linear OTA, forces the reference voltage at pin 2 to decrease by discharging C<sub>FT</sub>.

So, during the static mode, when the input voltage goes below  $V_{MIN}$  the drop out is kept fixed to about 1.6V. In this condition the device works as a low pass filter in the range (2) of the OTA characteristic. The fipple rejection is externally adjustable acting on  $C_{\text{FT}}$  as follows:

SVR (jw) =

$$\left| \frac{V_1 (jw)}{V_{out} (jw)} \right| =$$

$$1 + \frac{10^{-6}}{\frac{gm}{jwC_{FT}}} (1 + \frac{R1}{R2})$$

Where: gm =  $2 \cdot 10^{-5} \ \Omega^{-1}$  = OTA'S typical transconductance value on linear region

$$\frac{R1}{R2}$$

= fixed ratio

$C_{FT}$  = value of capacitor in  $\mu F$

The reaction time of the supervisor loop is given by the transconductance of the OTA and by  $C_{\rm FT}$ . When the value of the ripple voltage is so high and its negative peak is fast enough to determine an istantaneous decrease of the dropout till 1.2V, the OTA works in a higher transconductance condition [range (3) of the characteristic] and discharge the capacitor rapidously.

If the ripple frequency is high enough the capacitor won't charge itself completely, and the output voltage reaches a small value allowing a better ripple rejection; the device's again working as a filter (fast transient range).

With  $C_{FT} = 10 \ \mu F$ ; f = 100 Hz a SVR of 35 is obtained.

Fig. 3 - Nonliner transfer characteristic of the drop control unit

Fig. 4 - Supply voltage rejection vs. input voltage

Fig. 5 - Supply voltage rejection vs. frequency

Fig. 6 - Vo vs. supply voltage

Fig. 7 - Quiescent current vs. input voltage

Fig. 8 - Dropout vs. load current

Fig. 9 - Inhibit function realized on CFT pin.