SNOSAJ2-FEBRUARY 2005 www.ti.com

# LF198JAN Monolithic Sample-and-Hold Circuits

Check for Samples: LF198JAN

### **FEATURES**

- Operates from ±5V to ±18V supplies

- Less than 10 µs acquisition time

- TTL, PMOS, CMOS compatible logic input

- 0.5 mV typical hold step at  $C_h = 0.01 \mu F$

- Low input offset

- 0.002% gain accuracy

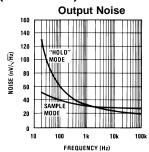

- Low output noise in hold mode

- Input characteristics do not change during hold mode

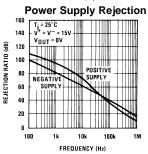

- High supply rejection ratio in sample or hold

- Wide bandwidth

- **Space Qualified** Logic inputs on the LF198 are fully differential with low input current, allowing direct connection to TTL, PMOS, and CMOS. Differential threshold is 1.4V. The LF198 will operate from ±5V to ±18V supplies.

### DESCRIPTION

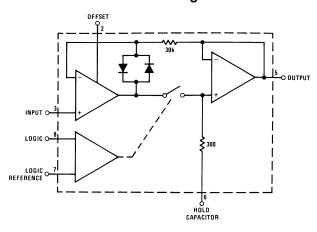

The LF198 is a monolithic sample-and-hold circuit which utilizes BI-FET technology to obtain ultra-high dc accuracy with fast acquisition of signal and low droop rate. Operating as a unity gain follower, dc gain accuracy is 0.002% typical and acquisition time is as low as 6 µs to 0.01%. A bipolar input stage is used to achieve low offset voltage and wide bandwidth. Input offset adjust is accomplished with a single pin, and does not degrade input offset drift. The wide bandwidth allows the LF198 to be included inside the feedback loop of 1 MHz op amps without having stability problems. Input impedance of 10<sup>10</sup>Ω allows high source impedances to be used without degrading accuracy.

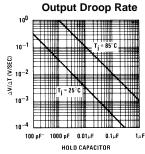

P-channel junction FET's are combined with bipolar devices in the output amplifier to give droop rates as low as 5 mV/min with a 1 µF hold capacitor. The JFET's have much lower noise than MOS devices used in previous designs and do not exhibit high temperature instabilities. The overall design guarantees no feed-through from input to output in the hold mode, even for input signals equal to the supply voltages.

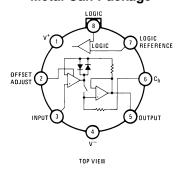

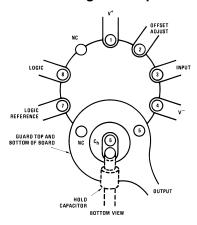

### **Connection Diagrams**

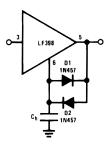

#### Metal Can Package

Figure 1.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

SNOSAJ2 – FEBRUARY 2005 www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

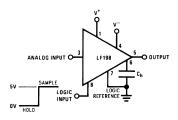

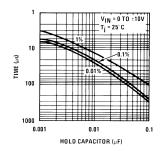

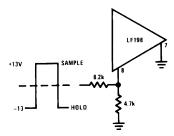

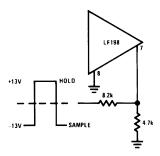

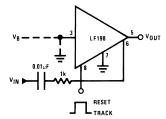

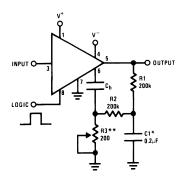

# **Typical Connection and Performance Curve**

Figure 2. Acquisition Time

### **Functional Diagram**

Submit Documentation Feedback

# **Absolute Maximum Ratings (1)**

| Supply Voltage                                    | ±18V                           |

|---------------------------------------------------|--------------------------------|

| Power Dissipation (Package Limitation) (2)        | 500 mW                         |

| Operating Ambient Temperature Range               | -55°C ≤T <sub>A</sub> ≤ +125°C |

| Storage Temperature Range                         | −65°C to +150°C                |

| Maximum Junction Temperature (T <sub>Jmax</sub> ) | +150°C                         |

| Input Voltage                                     | Equal to Supply Voltage        |

| Logic To Logic Reference Differential Voltage (3) | +7V, -30V                      |

| Output Short Circuit Duration                     | Indefinite                     |

| Hold Capacitor Short Circuit Duration             | 10 sec                         |

| Lead Temperature (Soldering, 10 sec.)             | 300°C                          |

| Thermal Resistance                                |                                |

| $\theta_{ m JA}$                                  |                                |

| Metal Can (Still Air @ 0.5W)                      | 160°C/W                        |

| Metal Can (500 LF/Min Air Flow @ 0.5W)            | 84°C/W                         |

| θ <sub>JC</sub>                                   |                                |

| Metal Can                                         | 48°C/W                         |

| ESD Tolerance (4)                                 | 500V                           |

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions

- (2) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any temperature is P<sub>D</sub> = (T<sub>JMAX</sub> T<sub>A</sub>)/θ<sub>JA</sub>, or the number given in the Absolute Maximum Ratings, whichever is lower.

- Maximum Ratings, whichever is lower. .

(3) Although the differential voltage may not exceed the limits given, the common-mode voltage on the logic pins may be equal to the supply voltages without causing damage to the circuit. For proper logic operation, however, one of the logic pins must always be at least 2V below the positive supply and 3V above the negative supply.

- (4) Human body model, 100pF discharged through 1.5KΩ

### **Quality Conformance Inspection**

Mil-Std-883, Method 5005 — Group A

| Subgroup | Description         | Temperature (°C) |

|----------|---------------------|------------------|

| 1        | Static tests at     | +25°C            |

| 2        | Static tests at     | +125°C           |

| 3        | Static tests at     | −55°C            |

| 4        | Dynamic tests at    | +25°C            |

| 5        | Dynamic tests at    | +125°C           |

| 6        | Dynamic tests at    | −55°C            |

| 7        | Functional tests at | +25°C            |

| 8A       | Functional tests at | +125°C           |

| 8B       | Functional tests at | −55°C            |

| 9        | Switching tests at  | +25°C            |

| 10       | Switching tests at  | +125°C           |

| 11       | Switching tests at  | −55°C            |

# **Electrical Characteristics DC Parameters**

| Symbol                | Parameter                       | ter Conditions                                                           |  |           |           |    | Sub-<br>groups |  |

|-----------------------|---------------------------------|--------------------------------------------------------------------------|--|-----------|-----------|----|----------------|--|

| V <sub>IO</sub>       | Input Offset Voltage            | $+V_{CC} = 3.5V, -V_{CC} = -26.5V,$                                      |  | -3.0      | 3.0       | mV | 1              |  |

|                       |                                 | V <sub>CM</sub> = 11.5V                                                  |  | -5.0      | 5.0       | mV | 2, 3           |  |

|                       |                                 | $+V_{CC} = 26.5V, -V_{CC} = -3.5V,$                                      |  | -3.0      | 3.0       | mV | 1              |  |

|                       |                                 | V <sub>CM</sub> = -11.5V                                                 |  | -5.0      | 5.0       | mV | 2, 3           |  |

|                       |                                 | $+V_{CC} = 15V, -V_{CC} = -15V,$                                         |  | -3.0      | 3.0       | mV | 1              |  |

|                       |                                 | $V_{CM} = 0V$                                                            |  | -5.0      | 5.0       | mV | 2, 3           |  |

|                       |                                 | $+V_{CC} = 7V, -V_{CC} = -3V,$                                           |  | -3.0      | 3.0       | mV | 1              |  |

|                       |                                 | $V_{CM} = 2V$                                                            |  | -5.0      | 5.0       | mV | 2, 3           |  |

|                       |                                 | $+V_{CC} = 3V, -V_{CC} = -7V,$                                           |  | -3.0      | 3.0       | mV | 1              |  |

|                       |                                 | V <sub>CM</sub> = -2V                                                    |  | -5.0      | 5.0       | mV | 2, 3           |  |

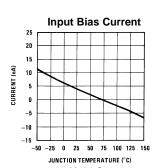

| I <sub>IB</sub>       | Input Bias Current              | $+V_{CC} = 3.5V, -V_{CC} = -26.5V,$                                      |  | -1.0      | 25        | nA | 1              |  |

|                       |                                 | V <sub>CM</sub> = 11.5V                                                  |  | -25       | 75        | nA | 2, 3           |  |

|                       |                                 | $+V_{CC} = 26.5V, -V_{CC} = -3.5V, V_{CM} =$                             |  | -1.0      | 25        | nA | 1              |  |

|                       |                                 | -11.5V                                                                   |  | -25       | 75        | nA | 2, 3           |  |

|                       |                                 | $+V_{CC} = 15V, -V_{CC} = -15V,$                                         |  | -1        | 25        | nA | 1              |  |

|                       |                                 | $V_{CM} = 0V$                                                            |  | -25       | 75        | nA | 2, 3           |  |

|                       |                                 | $+V_{CC} = 7V, -V_{CC} = -3V,$                                           |  | -1        | 25        | nA | 1              |  |

|                       |                                 | $V_{CM} = 2V$                                                            |  | -25       | 75        | nA | 2, 3           |  |

|                       |                                 | +V <sub>CC</sub> = 3V, -V <sub>CC</sub> = -7V,                           |  | -1.0      | 25        | nA | 1              |  |

|                       |                                 | $V_{CM} = -2V$                                                           |  | -25       | 75        | nA | 2, 3           |  |

| Z <sub>I</sub>        | Input Impedance                 | $+V_{CC} = 3.5V$ to 26.6V,                                               |  | 2.0       |           | GΩ | 1              |  |

| •                     | , .                             | $-V_{CC} = -26.5V$ to $-3.5V$ , $V_{CM} = 11.5V$ to $-11.5V$             |  | 1.0       |           | GΩ | 2, 3           |  |

| V <sub>IO Adj</sub> + | Input Offset Voltage Adjustment | $+V_{CC} = 15V, -V_{CC} = -15V,$<br>$V_{CM} = 0V$                        |  | 6.0       |           | mV | 1, 2, 3        |  |

| V <sub>IO Adj</sub> - | Input Offset Voltage Adjustment | $+V_{CC} = 15V, -V_{CC} = -15V,$<br>$V_{CM} = 0V$                        |  |           | -6.0      | mV | 1, 2, 3        |  |

| PSRR+                 | Power Supply Rejection Ratio    | $-V_{CC} = -18V,$<br>+ $V_{CC} = 18V \text{ to } 12V$                    |  | 80        |           | dB | 1, 2, 3        |  |

| PSRR-                 | Power Supply Rejection Ratio    | +V <sub>CC</sub> = 18V,<br>-V <sub>CC</sub> = -12V to -18V               |  | 80        |           | dB | 1, 2, 3        |  |

| Icc                   | Supply Current                  | $+V_{CC} = 15V, -V_{CC} = -15V,$                                         |  | 1.0       | 5.5       | mA | 1,2            |  |

|                       |                                 | $V_{CM} = 0V$                                                            |  | 1.0       | 6.5       | mA | 3              |  |

| A <sub>E</sub>        | Gain Error                      | +V <sub>CC</sub> = 3.5V to 26.5V,<br>-V <sub>CC</sub> = -26.5V to -3.5V, |  | 0.00<br>5 | 0.00<br>5 | %  | 1              |  |

|                       |                                 | $V_{CM} = -11.5V$ to 11.5V                                               |  | -0.02     | 0.02      | %  | 2, 3           |  |

|                       |                                 | $+V_{CC} = 3V$ to $7V$ ,                                                 |  | -0.02     | 0.02      | %  | 1              |  |

|                       |                                 | $-V_{CC} = -7V$ to $-3V$ , $V_{CM} = -2V$ to $2V$                        |  | -0.04     | 0.04      | %  | 2, 3           |  |

| R <sub>SC</sub>       | Series Charge Resistance        | $+V_{CC} = 15V, -V_{CC} = -15V, V_{CM} = 0V$                             |  | 75        | 400       | Ω  | 1, 2, 3        |  |

| I <sub>IH</sub> (a)   | Logical 1 Input Current         | $+V_{CC} = 8.5V, -V_{CC} = -21.5V$                                       |  | 0         | 10        | μΑ | 1, 2, 3        |  |

| I <sub>IH</sub> (b)   | Logical 1 Input Current         | $+V_{CC} = 8.5V, -V_{CC} = -21.5V$                                       |  | 0         | 10        | μΑ | 1, 2, 3        |  |

| I <sub>IL</sub> (a)   | Logical 0 Input Current         | +V <sub>CC</sub> = 21.5V, -V <sub>CC</sub> = -8.5V                       |  | -1.0      | 1.0       | μΑ | 1, 2, 3        |  |

| I <sub>IL</sub> (b)   | Logical 0 Input Current         | +V <sub>CC</sub> = 21.5V, -V <sub>CC</sub> = -8.5V                       |  | -1.0      | 1.0       | μΑ | 1, 2, 3        |  |

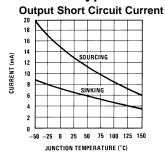

| I <sub>OS</sub> +     | Output Short Circuit Current    | $+V_{CC} = 15V, -V_{CC} = -15V, V_{CM} = 0V$                             |  | -25       |           | mA | 1, 2, 3        |  |

| I <sub>OS</sub> -     | Output Short Circuit Current    | $+V_{CC} = 15V, -V_{CC} = -15V, V_{CM} = 0V$                             |  |           | 25        | mA | 1, 2, 3        |  |

## **Electrical Characteristics DC Parameters (continued)**

| Symbol              | Parameter                     | Conditions                                                                                                 | Notes | Min       | Max  | Unit | Sub-<br>groups |

|---------------------|-------------------------------|------------------------------------------------------------------------------------------------------------|-------|-----------|------|------|----------------|

| I <sub>CH</sub> +   | Hold Capacitor Charge Current | $+V_{CC} = 15V, -V_{CC} = -15V,$                                                                           |       |           | -3.0 | mA   | 1              |

|                     |                               | $V_{CM} = 0V$                                                                                              |       |           | -2.0 | mA   | 2, 3           |

| I <sub>CH</sub> -   | Hold Capacitor Charge Current | $+V_{CC} = 15V, -V_{CC} = -15V,$                                                                           |       | 3.0       |      | mA   | 1              |

|                     |                               | $V_{CM} = 0V$                                                                                              |       | 2.0       |      | mA   | 2, 3           |

| V <sub>Th</sub> (H) | Differential Logic Threshold  | +V <sub>CC</sub> = 15V, -V <sub>CC</sub> = -15V,<br>V <sub>CM</sub> = 0V<br>Logic = 2.0V, Logic Ref = 2.0V |       | 1.0       |      | mA   | 1, 2, 3        |

| V <sub>Th</sub> (L) | Differential Logic Threshold  | +V <sub>CC</sub> = 15V, -V <sub>CC</sub> = -15V,<br>V <sub>CM</sub> = 0V<br>Logic = 0.8V, Logic Ref = 2.0V |       | -10       | 10   | μΑ   | 1, 2, 3        |

| I <sub>HL</sub> +   | Hold Mode Leakage Current     | $+V_{CC} = 3.5V, -V_{CC} = -26.5V, V_{CM} = -11.5V$                                                        | (1)   | 0.10<br>0 | 0.10 | nA   | 1              |

|                     |                               | S                                                                                                          |       | -50       | 50   | nA   | 2              |

| I <sub>HL</sub> -   | Hold Mode Leakage Current     | +V <sub>CC</sub> = 26.5V, -V <sub>CC</sub> = -3.5V, V <sub>CM</sub> = 11.5V                                | (2)   | 0.10<br>0 | 0.10 | nA   | 1              |

|                     |                               |                                                                                                            |       | -50       | 50   | nA   | 2              |

| Z <sub>O</sub>      | Output Impedance              | +V <sub>CC</sub> = 15V, -V <sub>CC</sub> = -15V,<br>V <sub>CM</sub> = 0V                                   |       |           | 2.0  | Ω    | 1, 2, 3        |

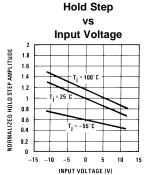

| $V_{HS}$            | (HOLD) Step Voltage           | $+V_{CC} = 3.5V, -V_{CC} = -26.5V, V_{CM} =$                                                               | (3)   | -2.0      | 2.0  | mV   | 1              |

|                     |                               | 11.5V                                                                                                      |       | -5.0      | 5.0  | mV   | 2, 3           |

|                     |                               | $+V_{CC} = 26.5V, -V_{CC} = -3.5V, V_{CM} =$                                                               | (3)   | -2.0      | 2.0  | mV   | 1              |

|                     |                               | -11.5V                                                                                                     |       | -5.0      | 5.0  | mV   | 2, 3           |

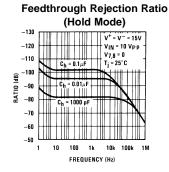

| $F_{RR}$            | Feedthrough Rejection Ratio   | $+V_{CC} = 15V, -V_{CC} = -15V,$                                                                           |       | 86        |      | dB   | 1              |

|                     |                               | $V_{CM} = 0V, V_{I} = 0V \text{ to } 11.5V$                                                                |       | 80        |      | dB   | 2, 3           |

|                     |                               | $+V_{CC} = 15V, -V_{CC} = -15V,$                                                                           |       | 86        |      | dB   | 1              |

|                     |                               | $V_{CM} = 0V, V_I = 11.5V \text{ to } 0V$                                                                  |       | 80        |      | dB   | 2, 3           |

|                     |                               | $+V_{CC} = 15V, -V_{CC} = -15V,$                                                                           |       | 86        |      | dB   | 1              |

|                     |                               | $V_{CM} = 0V, V_{I} = 0V \text{ to -11.5V}$                                                                |       | 80        |      | dB   | 2, 3           |

|                     |                               | $+V_{CC} = 15V, -V_{CC} = -15V,$                                                                           |       | 86        |      | dB   | 1              |

|                     |                               | $V_{CM} = 0V, V_{I} = -11.5V \text{ to } 0V$                                                               |       | 80        |      | dB   | 2, 3           |

<sup>(1)</sup> Leakage current is measured at a junction temperature of 25°C. The effects of junction temperature rise due to power dissipation or elevated ambient can be calculated by doubling the 25°C value for each 11°C increase in chip temperature. Leakage is guaranteed over full input signal range.

<sup>(2)</sup> Leakage current is measured at a junction temperature of 25°C. The effects of junction temperature rise due to power dissipation or elevated ambient can be calculated by doubling the 25°C value for each 11°C increase in chip temperature. Leakage is guaranteed over full input signal range.

<sup>(3)</sup> Hold step is sensitive to stray capacitive coupling between input logic signals and the hold capacitor. 1 pF, for instance, will create an additional 0.5 mV step with a 5V logic swing and a 0.01μF hold capacitor. Magnitude of the hold step is inversely proportional to hold capacitor value.

SNOSAJ2 – FEBRUARY 2005 www.ti.com

## **AC/DC Parameters**

| Symbol                             | Parameter                                | Conditions                                                      | Notes | Min | Max | Unit                 | Sub-<br>groups |

|------------------------------------|------------------------------------------|-----------------------------------------------------------------|-------|-----|-----|----------------------|----------------|

| Delta V <sub>IO</sub> /<br>Delta T | Input Offset Voltage Temp<br>Sensitivity |                                                                 |       | -20 | 20  | μV/°C                | 8A, 8B         |

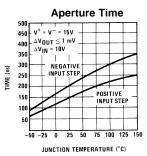

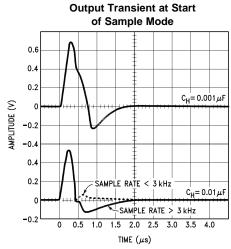

| $T_{AQ}$                           | Aquisition Time                          | +V <sub>CC</sub> = 15V, -V <sub>CC</sub> = -15V                 |       |     | 25  | μS                   | 7              |

| T <sub>AP</sub>                    | Aperture Time                            | +V <sub>CC</sub> = 15V, -V <sub>CC</sub> = -15V                 |       |     | 300 | nS                   | 7              |

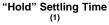

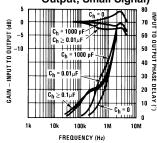

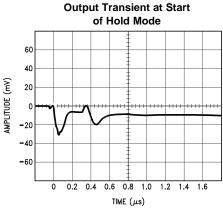

| T <sub>S</sub>                     | Settling Time                            | +V <sub>CC</sub> = 15V, -V <sub>CC</sub> = -15V                 |       |     | 1.5 | μS                   | 7              |

| F <sub>RR</sub> AC                 | Feedthrough Rejection Ratio              | $+V_{CC} = 15V$ , $-V_{CC} = -15V$ , $V_{I} = 20Vpp$            |       | 86  |     | dB                   | 7              |

| TR <sub>TS</sub>                   | Transient Response (settling time)       | $+V_{CC} = 3.5V$ , $-V_{CC} = -26.5V$ , $V_{I} = 100$ mV pulse  |       |     | 2.5 | μS                   | 7              |

|                                    |                                          | $+V_{CC} = 26.5V$ , $-V_{CC} = -3.5V$ , $V_{I} = 100$ mV pulse  |       |     | 2.5 | μS                   | 7              |

| TR <sub>OS</sub>                   | Transient Response (overshoot)           | $+V_{CC} = 3.5V$ , $-V_{CC} = -26.5V$ , $V_{I} = 100$ mV pulse  |       |     | 40  | %                    | 7              |

|                                    |                                          | $+V_{CC} = 26.5V, -V_{CC} = -3.5V, V_{I} = 100mV \text{ pulse}$ |       |     | 40  | %                    | 7              |

| en <sub>H</sub>                    | Noise                                    | +V <sub>CC</sub> = 15V, -V <sub>CC</sub> = -15V                 |       |     | 10  | ${\rm mV}_{\rm RMS}$ | 7              |

| en <sub>S</sub>                    | Noise                                    | +V <sub>CC</sub> = 15V, -V <sub>CC</sub> = -15V                 |       |     | 10  | ${\rm mV}_{\rm RMS}$ | 7              |

# **DC Parameters: Drift Values**

Delta calculations performed on S-Level devices at group B, subgroup 5 ONLY.

| Symbol          | Parameters           | Conditions                                        | Notes | Min  | Max | Unit | Sub-<br>groups |

|-----------------|----------------------|---------------------------------------------------|-------|------|-----|------|----------------|

| V <sub>IO</sub> | Input Offset Voltage | $+V_{CC} = 15V, -V_{CC} = -15V,$<br>$V_{CM} = 0V$ |       | -0.5 | 0.5 | mV   | 1              |

| I <sub>IB</sub> | Input Bias Current   | $+V_{CC} = 15V, -V_{CC} = -15V,$<br>$V_{CM} = 0V$ |       | -2.5 | 2.5 | nA   | 1              |

### **Typical Performance Characteristics**

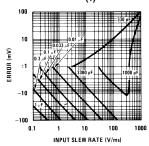

# Dynamic Sampling Error

# Hold Step

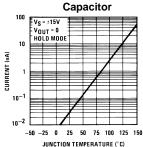

# Leakage Current into Hold

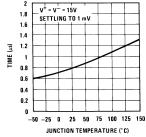

# Phase and Gain (Input to Output, Small Signal)

# TEXAS INSTRUMENTS

## **Typical Performance Characteristics (continued)**

See Definition

www.ti.com

# **Logic Input Configurations**

# TTL & CMOS 3V ≤ V<sub>LOGIC</sub> (Hi State) ≤ 7V

Threshold = 1.4V

Threshold = 1.4V\*Select for 2.8V at pin 8

# **CMOS**

$7V \le V_{LOG/C}$  (Hi State)  $\le 15V$

Threshold =  $0.6 (V^+) + 1.4V$

Threshold =  $0.6 (V^+) - 1.4V$

Copyright © 2005, Texas Instruments Incorporated

SNOSAJ2 – FEBRUARY 2005 www.ti.com

#### Op Amp Drive

Threshold ≈ +4V

Threshold = -4V

### **Application Hints**

#### HOLD CAPACITOR

Hold step, acquisition time, and droop rate are the major trade-offs in the selection of a hold capacitor value. Size and cost may also become important for larger values. Use of the curves included with this data sheet should be helpful in selecting a reasonable value of capacitance. Keep in mind that for fast repetition rates or tracking fast signals, the capacitor drive currents may cause a significant temperature rise in the LF198.

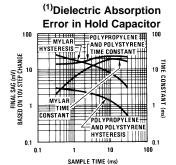

A significant source of error in an accurate sample and hold circuit is dielectric absorption in the hold capacitor. A mylar cap, for instance, may "sag back" up to 0.2% after a quick change in voltage. A long sample time is required before the circuit can be put back into the hold mode with this type of capacitor. Dielectrics with very low hysteresis are polystyrene, polypropylene, and Teflon. Other types such as mica and polycarbonate are not nearly as good. The advantage of polypropylene over polystyrene is that it extends the maximum ambient temperature from 85°C to 100°C. Most ceramic capacitors are unusable with > 1% hysteresis. Ceramic "NPO" or "COG" capacitors are now available for 125°C operation and also have low dielectric absorption. For more exact data, see the curve *Dielectric Absorption Error*. The hysteresis numbers on the curve are final values, taken after full relaxation. The hysteresis error can be significantly reduced if the output of the LF198 is digitized quickly after the hold mode is initiated. The hysteresis relaxation time constant in polypropylene, for instance, is 10—50 ms. If A-to-D conversion can be made within 1 ms, hysteresis error will be reduced by a factor of ten.

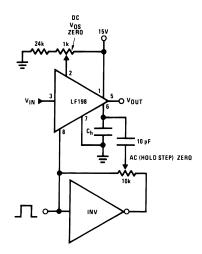

#### DC AND AC ZEROING

DC zeroing is accomplished by connecting the offset adjust pin to the wiper of a 1 k $\Omega$  potentiometer which has one end tied to V<sup>+</sup> and the other end tied through a resistor to ground. The resistor should be selected to give  $\approx$ 0.6 mA through the 1k potentiometer.

AC zeroing (hold step zeroing) can be obtained by adding an inverter with the adjustment pot tied input to output. A 10 pF capacitor from the wiper to the hold capacitor will give  $\pm 4$  mV hold step adjustment with a 0.01  $\mu$ F hold capacitor and 5V logic supply. For larger logic swings, a smaller capacitor (< 10 pF) may be used.

### **LOGIC RISE TIME**

For proper operation, logic signals into the LF198 must have a minimum dV/dt of 1.0 V/ $\mu$ s. Slower signals will cause excessive hold step. If a R/C network is used in front of the logic input for signal delay, calculate the slope of the waveform at the threshold point to ensure that it is at least 1.0 V/ $\mu$ s.

#### **SAMPLING DYNAMIC SIGNALS**

Sample error to moving input signals probably causes more confusion among sample-and-hold users than any other parameter. The primary reason for this is that many users make the assumption that the sample and hold amplifier is truly locked on to the input signal while in the sample mode. In actuality, there are finite phase delays through the circuit creating an input-output differential for fast moving signals. In addition, although the output may have settled, the hold capacitor has an additional lag due to the  $300\Omega$  series resistor on the chip. This means that at the moment the "hold" command arrives, the hold capacitor voltage may be somewhat different than the actual analog input. The effect of these delays is opposite to the effect created by delays in the logic which switches the circuit from sample to hold. For example, consider an analog input of 20 Vp-p at 10 kHz. Maximum dV/dt is  $0.6 \text{ V/}\mu\text{s}$ . With no analog phase delay and 100 ns logic delay, one could expect up to  $(0.1 \, \mu\text{s})(0.6 \, \text{V/}\mu\text{s}) = 60 \, \text{mVerror}$  if the "hold" signal arrived near maximum dV/dt of the input. A positive-going input would give a +60 mV error. Now assume a 1 MHz (3 dB) bandwidth for the overall analog loop. This generates a phase delay of 160 ns. If the hold capacitor sees this exact delay, then error due to analog delay will be  $(0.16 \, \mu\text{s})(0.6 \, \text{V/}\mu\text{s}) = -96 \, \text{mV}$ . Total output error is +60 mV (digital) -96 mV (analog) for a total of -36 mV. To add to the confusion, analog delay is proportioned to hold capacitor value while digital delay remains constant. A family of curves (dynamic sampling error) is included to help estimate errors.

A curve labeled *Aperture Time* has been included for sampling conditions where the input is steady during the sampling period, but may experience a sudden change nearly coincident with the "hold" command. This curve is based on a 1 mV error fed into the output.

A second curve, *Hold Settling Time* indicates the time required for the output to settle to 1 mV after the "hold" command.

### **DIGITAL FEEDTHROUGH**

Fast rise time logic signals can cause hold errors by feeding externally into the analog input at the same time the amplifier is put into the hold mode. To minimize this problem, board layout should keep logic lines as far as possible from the analog input and the  $C_h$  pin. Grounded guarding traces may also be used around the input line, especially if it is driven from a high impedance source. Reducing high amplitude logic signals to 2.5V will also help.

#### **Guarding Technique**

Figure 3. Use 10-pin layout. Guard around Chis tied to output.

# TEXAS INSTRUMENTS

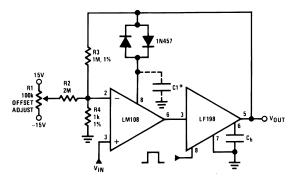

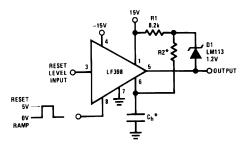

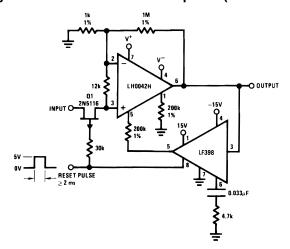

## **Typical Applications**

Figure 4. X1000 Sample & Hold

\*For lower gains, the LM108 must be frequency compensated

Use  $\approx \frac{100}{A_V}$  pF from comp 2 to ground

Figure 5. Sample and Difference Circuit (Output Follows Input in *Hold* Mode)

$V_{OUT} = V_B + \Delta V_{IN}(HOLD MODE)$

Figure 6. Ramp Generator with Variable Reset Level

\*Select for ramp rate  $\frac{\Delta V}{\Delta T} = \frac{1.2V}{(\text{R2}) (C_{\text{h}})}$

Submit Documentation Feedback

www.ti.com

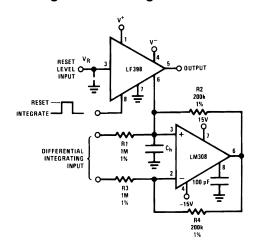

Figure 7. Integrator with Programmable Reset Level

$$V_{OUT} \left( \text{Hold Mode} \right) = \left[ \frac{1}{\left( \text{R1} \right) \left( \text{C}_{\text{h}} \right)} \int_{0}^{t} \!\! V_{\text{IN}} \, \text{d}t \, \right] + \left[ V_{\text{R}} \, \right]$$

Figure 8. Output Holds at Average of Sampled Input

Select (R<sub>h</sub>) (C<sub>h</sub>)

$$\gg \frac{1}{2\pi f_{\text{IN}} \text{ (Min)}}$$

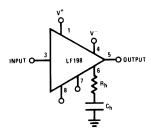

Figure 9. Increased Slew Current

Copyright © 2005, Texas Instruments Incorporated

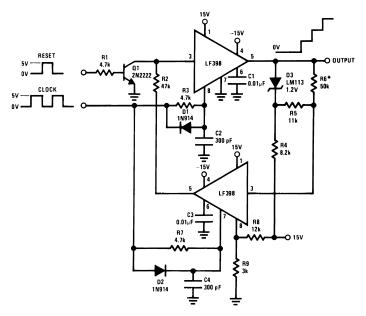

Figure 10. Reset Stabilized Amplifier (Gain of 1000)

$$\begin{split} &V_{OS} \leq 20 \mu \text{V (No trim)} \\ &Z_{IN} \approx 1 \text{ M}\Omega \\ &\frac{\Delta V_{OS}}{\Delta t} \approx 30 \mu \text{V/sec} \\ &\frac{\Delta V_{OS}}{\Delta T} \approx 0.1 \mu \text{V/°C} \end{split}$$

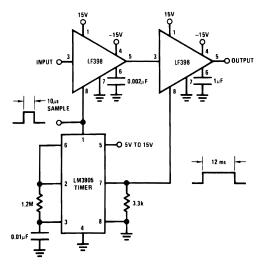

Figure 11. Fast Acquisition, Low Droop Sample & Hold

Submit Documentation Feedback

www.ti.com

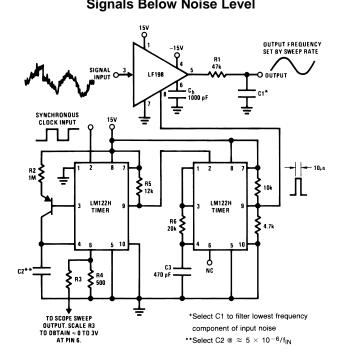

Figure 12. Synchronous Correlator for Recovering Signals Below Noise Level

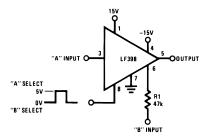

Figure 13. 2-Channel Switch

|                 | A                  | В         |

|-----------------|--------------------|-----------|

| Gain            | 1 ± 0.02%          | 1 ± 0.2%  |

| Z <sub>IN</sub> | 10 <sup>10</sup> Ω | 47 kΩ     |

| BW              | ≃ 1 MHz            | ≃ 400 kHz |

| Crosstalk       | -90 dB             | -90 dB    |

| @ 1 kHz         |                    |           |

| Offset          | ≤ 6 mV             | ≤ 75 mV   |

Figure 14. DC & AC Zeroing

Figure 15. Staircase Generator

\*Select for step height  $50k \rightarrow \cong 1V$  Step

Submit Documentation Feedback

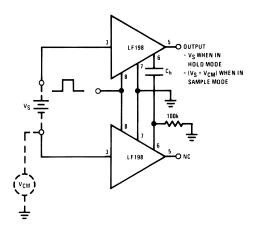

Figure 16. Differential Hold

Figure 17. Capacitor Hysteresis Compensation

### **Definition of Terms**

**Hold Step:** The voltage step at the output of the sample and hold when switching from sample mode to hold mode with a steady (dc) analog input voltage. Logic swing is 5V.

**Acquisition Time:** The time required to acquire a new analog input voltage with an output step of 10V. Note that acquisition time is not just the time required for the output to settle, but also includes the time required for all internal nodes to settle so that the output assumes the proper value when switched to the hold mode.

**Gain Error:** The ratio of output voltage swing to input voltage swing in the sample mode expressed as a per cent difference.

Hold Settling Time: The time required for the output to settle within 1 mV of final value after the "hold" logic command.

**Dynamic Sampling Error:** The error introduced into the held output due to a changing analog input at the time the hold command is given. Error is expressed in mV with a given hold capacitor value and input slew rate. Note that this error term occurs even for long sample times.

**Aperture Time:** The delay required between "Hold" command and an input analog transition, so that the transition does not affect the held output.

<sup>\*</sup>Select for time constant C1 =  $\frac{\tau}{100k}$

<sup>\*\*</sup>Adjust for amplitude

SNOSAJ2 – FEBRUARY 2005 www.ti.com

## **REVISION HISTORY SECTION**

| Date<br>Released | Revision | Section                       | Originator | Changes                                                                          |

|------------------|----------|-------------------------------|------------|----------------------------------------------------------------------------------|

| 02/25/05         | Α        | New release, Corporate format | L. Lytle   | 1 MDS converted to corp. datasheet format. MJLF198–X Rev 2B0 MDS to be archived. |

www.ti.com 26-Jan-2013

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan | Lead/Ball Finish | MSL Peak Temp    | Op Temp (°C) | Top-Side Markings                                           | Samples |

|------------------|--------|--------------|--------------------|------|-------------|----------|------------------|------------------|--------------|-------------------------------------------------------------|---------|

| JL198BGA         | ACTIVE | TO-99        | LMC                | 8    | 20          | TBD      | POST-PLATE       | Level-1-NA-UNLIM | 00 10 120    | JL198BGA<br>JM38510/12501BGA Q ACO<br>JM38510/12501BGA Q >T | Samples |

| JL198SGA         | ACTIVE | TO-99        | LMC                | 8    | 20          | TBD      | POST-PLATE       | Level-1-NA-UNLIM |              | JL198SGA<br>JM38510/12501SGA Q ACO<br>JM38510/12501SGA Q >T | Samples |

| JM38510/12501BGA | ACTIVE | TO-99        | LMC                | 8    | 20          | TBD      | POST-PLATE       | Level-1-NA-UNLIM | 00 10 120    | JL198BGA<br>JM38510/12501BGA Q ACO<br>JM38510/12501BGA Q >T | Samples |

| JM38510/12501SGA | ACTIVE | TO-99        | LMC                | 8    | 20          | TBD      | POST-PLATE       | Level-1-NA-UNLIM | 00 10 120    | JL198SGA<br>JM38510/12501SGA Q ACO<br>JM38510/12501SGA Q >T | Samples |

| M38510/12501BGA  | ACTIVE | TO-99        | LMC                | 8    | 20          | TBD      | POST-PLATE       | Level-1-NA-UNLIM |              | JL198BGA<br>JM38510/12501BGA Q ACO<br>JM38510/12501BGA Q >T | Samples |

| M38510/12501SGA  | ACTIVE | TO-99        | LMC                | 8    | 20          | TBD      | POST-PLATE       | Level-1-NA-UNLIM |              | JL198SGA<br>JM38510/12501SGA Q ACO<br>JM38510/12501SGA Q >T | Samples |

<sup>&</sup>lt;sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

26-Jan-2013

(4) Only one of markings shown within the brackets will appear on the physical device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF LF198JAN, LF198JAN-SP:

Military: LF198JAN

Space: LF198JAN-SP

NOTE: Qualified Version Definitions:

- Military QML certified for Military and Defense Applications

- Space Radiation tolerant, ceramic packaging and qualified for use in Space-based application

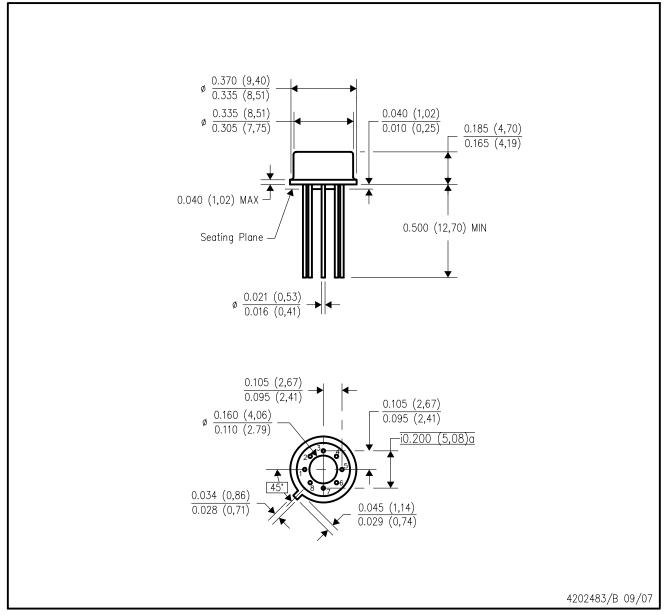

# LMC (O-MBCY-W8)

# METAL CYLINDRICAL PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Leads in true position within 0.010 (0,25) R @ MMC at seating plane.

- D. Pin numbers shown for reference only. Numbers may not be marked on package.

- E. Falls within JEDEC MO-002/TO-99.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>