# LH0038/LH0038C True Instrumentation Amplifier

# **General Description**

The LH0038/LH0038C is a precision true instrumentation amplifier (TIA) capable of amplifying very low level signals, such as thermocouple and low impedance strain gauge outputs. Precision thin film gain setting resistors are included in the package to allow the user to set the closed-loop gain from 100 to 2000. Since the resistors are of a homogeneous single chip construction, they track almost perfectly so that temperature variations of closed loop gain are virtually eliminated.

LH0038 exhibits excellent CMRR, PSRR, gain linearity, as well as extremely low input offset voltage, offset voltage drift and input noise voltage.

The devices are provided in a hermetically sealed 16-lead DIP. The LH0038 is guaranteed from  $-55^{\circ}$ C to  $+125^{\circ}$ C; whereas the LH0038C is guaranteed from  $-25^{\circ}$ C to  $+85^{\circ}$ C.

#### **Features**

- Ultra-low input offset voltage 25 µV typ., 100 µV max

- Ultra-low input offset drift

0.25 μV/°C max

■ Ultra-low input noise

0.2 μVp-p

■ Pin strap gain options 100, 200, 400, 500, 1k, 2k■ Excellent PSRR and CMRR

120 dB

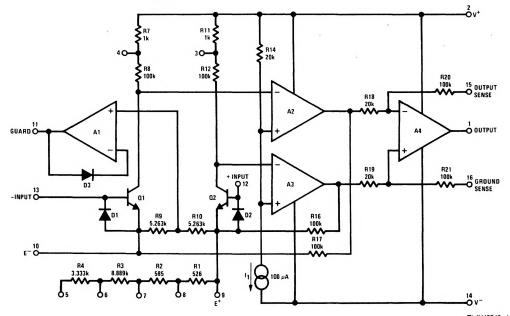

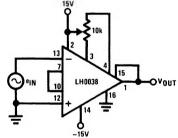

### **Simplified Schematic Diagram**

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications. (Note 4)

Supply Voltage

Input Voltage

Differential Input Voltage (Note 1)

± 1V

Power Dissipation (Note 3)

± 18V

± Vs 500 mW

**Short Circuit Duration**

Operating Temperature Range

LH0038 LH0038C -55°C to +125°C -25°C to +85°C

Continuous

Storage Temperature

-65°C to +150°C

Lead Temperature (Soldering, 10 sec.)

260°C

ESD rating to be determined.

#### DC Electrical Characteristics (Note 2)

| 0                     |                                    |                                       |                         | LH0038 |      | LH0038C |     |      |         |            |  |

|-----------------------|------------------------------------|---------------------------------------|-------------------------|--------|------|---------|-----|------|---------|------------|--|

| Symbol                | Parameter                          | Condition                             | ns                      | Min    | Тур  | Max     | Min | Тур  | Max     | Units      |  |

| V <sub>IOS</sub>      | Input Offset Voltage               | $R_S = 50\Omega$                      | T <sub>A</sub> = 25°C   |        | 25   | 100     |     | 30   | 150     | μV         |  |

|                       |                                    | V <sub>CM</sub> = 0V                  |                         |        |      | 125     |     |      | 220     | μ <b>ν</b> |  |

| ΔV <sub>IOS</sub> /ΔΤ | Input Offset Voltage<br>Tempco     |                                       |                         |        | 0.1  | 0.25    |     | 0.2  | 1.0     | μV/°C      |  |

| Voos                  | Output Offset Voltage              |                                       | T <sub>A</sub> = 25°C   |        | 3    | 10      |     | 5    | 25      |            |  |

|                       |                                    |                                       |                         |        |      | 15      |     |      | 30      | m∨         |  |

| ΔV <sub>OOS</sub> /ΔT | Output Offset Voltage<br>Tempco    |                                       |                         |        | 25   |         |     | 25   |         | μ۷/°С      |  |

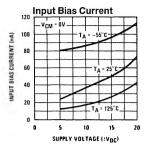

| lB                    | Input Bias Current                 |                                       | $T_A = 25^{\circ}C$     |        | 50   | 100     |     | 50   | 100     |            |  |

|                       |                                    |                                       |                         |        |      | 200     |     |      | 200     | nA         |  |

| los                   | Input Offset Current               |                                       | $T_A = 25^{\circ}C$     |        | 2    | 5       |     | 7    | 10      | 1171       |  |

|                       |                                    |                                       |                         |        |      | 8       |     |      | 15      |            |  |

| ΔΙ <sub>Β</sub> /ΔΤ   | Input Bias Current<br>Tempco       |                                       |                         |        | 500  |         |     | 500  |         | pA/°C      |  |

| A <sub>VCL</sub>      | Closed Loop Gain                   | Gain Pins Jumpered                    |                         |        |      |         |     |      |         | _          |  |

|                       |                                    | None                                  |                         |        | 100  |         |     | 100  |         | ]          |  |

|                       |                                    | 6-10                                  |                         |        | 200  |         |     | 200  | · · · · |            |  |

|                       |                                    | 6-9, 10-5<br>6-10, 5-9<br>7-10        |                         |        | 400  |         |     | 400  |         | V/V        |  |

|                       |                                    |                                       |                         |        | 500  |         |     | 500  |         |            |  |

|                       |                                    |                                       |                         |        | 1000 |         |     | 1000 |         |            |  |

|                       |                                    | 8-10                                  |                         |        | 2000 |         |     | 2000 |         |            |  |

|                       | Closed Loop Gain                   | A <sub>VCL</sub> = 100, 200           |                         |        | 0.1  | 0.3     |     | 0.1  | 0.4     |            |  |

|                       | Error                              | A <sub>VCL</sub> = 400, 500           |                         |        | 0.2  | 0.3     |     | 0.2  | 0.6     | %          |  |

|                       |                                    | A <sub>VCL</sub> = 1000               |                         |        | 0.3  | 0.5     |     | 0.5  | 1.0     |            |  |

|                       |                                    | A <sub>VCL</sub> = 2000               |                         |        | 1.0  | 2.0     |     | 1.5  | 3.0     |            |  |

|                       | Gain Temperature<br>Coefficient    | A <sub>VCL</sub> = 1k                 |                         |        | 7    |         |     | 7    |         | ppm/°C     |  |

|                       | Gain Nonlinearity                  | 100 ≤ A <sub>VCL</sub> ≤ 2k           |                         |        | 1    |         |     | 1    |         | ppm        |  |

| V <sub>INCM</sub>     | Common-Mode Input<br>Voltage Range |                                       |                         | ±10    | ±12  |         | ±10 | ±12  |         |            |  |

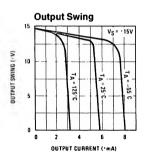

| Vo                    | Output Voltage                     | $R_L \ge 10  k\Omega$                 |                         | ±10    | ±12  |         | ±10 | ±12  |         | \          |  |

| ٧s                    | Supply Voltage Range               |                                       |                         | ±5     |      | ±18     | ±5  |      | ± 18    |            |  |

|                       | Guard Voltage Error                | $-10V < V_{CM} < +10V_{CM}$           | <b>/</b>                |        | ±10  | ± 100   |     | ±10  | ±100    | mV         |  |

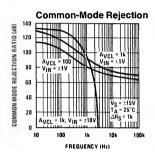

| CMRR                  | Common-Mode                        | V <sub>IN</sub> = ±10V                | A <sub>VCL</sub> = 100  | 94     | 110  |         | 86  | 110  |         |            |  |

|                       | Rejection Ratio                    |                                       | A <sub>VCL</sub> = 1000 | 114    | 120  |         | 106 | 110  |         | ٠,         |  |

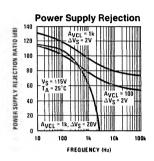

| PSRR                  | Power Supply                       | $\pm 5V \le \Delta V_{S} \le \pm 15V$ | A <sub>VCL</sub> = 100  | 94     | 110  |         | 94  | 110  |         | dB         |  |

|                       | Rejection Ratio                    |                                       | A <sub>VCL</sub> = 1000 | 110    | 120  |         | 100 | 110  |         |            |  |

# DC Electrical Characteristics (Note 2) (Continued)

| Symbol               | Parameter                       | Conditions                                     | LH00 |     | H0038 |     | LH0038C |      | Units |

|----------------------|---------------------------------|------------------------------------------------|------|-----|-------|-----|---------|------|-------|

| Cymbol               |                                 |                                                | Min  | Тур | Max   | Min | Тур     | Max  | Units |

| losc                 | Output Short<br>Circuit Current | $T_A = 25^{\circ}C$                            | ±2   | ±5  | ±10   | ±2  | ±5      | ± 10 | mA    |

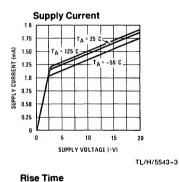

| Is                   | Supply Current                  | $T_A = 25^{\circ}C$                            |      | 1.6 | 2.0   |     | 1.6     | 3.0  |       |

| R <sub>IN</sub> DIFF | Input Resistance                | A <sub>VCL</sub> = 1000, T <sub>A</sub> = 25°C |      | 5   |       |     | 5       |      | МΩ    |

| RINCM                | Common-Mode Input<br>Resistance |                                                |      | 1   |       |     | 1       |      | GΩ    |

| R <sub>OUT</sub>     | Output Resistance               |                                                |      | 1   |       |     | 1       |      | mΩ    |

# AC Electrical Characteristics $V_S = \pm 15V$ , $T_A = 25^{\circ}C$

| Symbol         | Parameter                              | Comment   | Cond                  | Тур                     | Units |        |

|----------------|----------------------------------------|-----------|-----------------------|-------------------------|-------|--------|

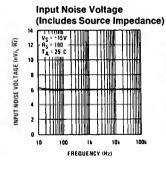

| en             | Equivalent Input Noise Voltage         | Figure 1  | $R_S = 0, f = 0.1 to$ | ), f = 0.1 to 10Hz      |       | μ∨р-р  |

| en             | Equivalent Input Spot Noise            | Figure 1  | $R_S = 100\Omega$     | f = 10 Hz               | 6.5   |        |

|                | Voltage                                |           |                       | f = 100 Hz              | 6.0   | nV/√Hz |

|                |                                        |           |                       | f = 1 kHz               | 6.0   |        |

|                | {                                      |           |                       | f = 10 kHz              | 6.0   |        |

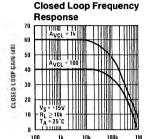

| BW             | Large Signal Bandwidth                 |           | $V_{OUT} = \pm 10V$   |                         | 1.6   | kHz    |

| S <sub>r</sub> | Slew Rate                              |           | $V_{OUT} = \pm 10V$   |                         | 0.3   | V/μs   |

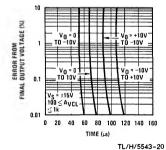

| ts             | Settling Time to 0.01%                 | Figure 13 |                       | 20V Step                | 120   |        |

|                |                                        |           |                       | -10V Step               | 80    | μs     |

|                | 1                                      |           |                       | + 10V Step              | 60    |        |

| t <sub>r</sub> | Rise Time                              |           | ΔV <sub>OUT</sub>     | A <sub>VCL</sub> = 100  | 6     | 6      |

|                |                                        |           |                       | A <sub>VCL</sub> = 1000 | 13    | μs     |

| l <sub>n</sub> | Equivalent Input Spot<br>Noise Current |           | $R_S = 100 M\Omega$   | f = 10 Hz               | 0.1   | pA/√Hz |

Note 1: The inputs are protected by diodes for overvoltage protection. Excessive currents will flow for differential voltages in excess of ±1V. Input current should be limited to less than 10 mA.

Note 2: Unless otherwise noted these specifications apply for V<sub>S</sub> = ±15.0V, pin 15 connected to pin 1, pin 16 connected to ground, over the temperature range -55°C to +125°C for the LH0038 and -25°C to +85°C for LH0038C. T<sub>A</sub> ≈ T<sub>j</sub> unless otherwise specified.

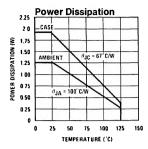

Note 3: See Typical Performance Characteristics for Thermal Resistance Information.

Note 4: Refer to RETS0038D for LH0038D military specifications.

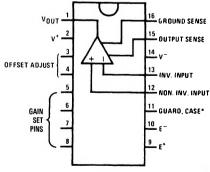

# **Connection Diagram**

# **Dual-In-Line Package**

**Top View**

TL/H/5543-2

\*Guard output is connected to the case. Order Number LH0038 or LH0038CD See NS Package Number D16D

# **Typical Performance Characteristics**

FREQUENCY (Hz)

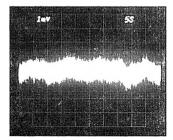

Wide Band Noise

**Pulse Response**

TL/H/5543-4  $V_S = \pm 15V$ ,  $R_S = 1 k\Omega$ ,  $A_V = 10k$ , DUT = 1kVertical sensitivity: 0.1 μV/CM

Horizontal sensitivity: 5 s/CM Bandwidth: 0.1 Hz to 10 Hz

$V_S = \pm 15V$  $R_L \geq \, 10 \, k\Omega$  $A_{VCL} = 1k$

TL/H/5543-5

V<sub>S</sub> = ±15V  $R_L \geq 10 k\Omega$ A<sub>VCL</sub> = 1k

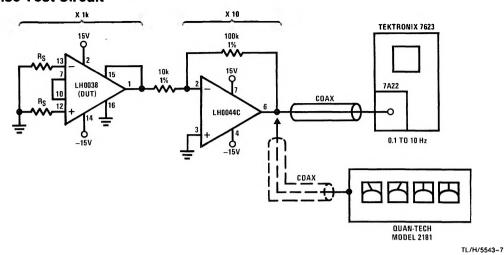

#### **Noise Test Circuit**

FIGURE 1

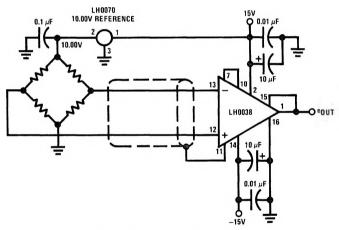

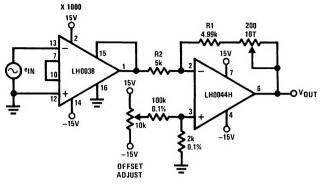

# **Typical Application**

FIGURE 2. X1000 Bridge Amplifier

# **Applications Information**

#### THEORY OF OPERATION

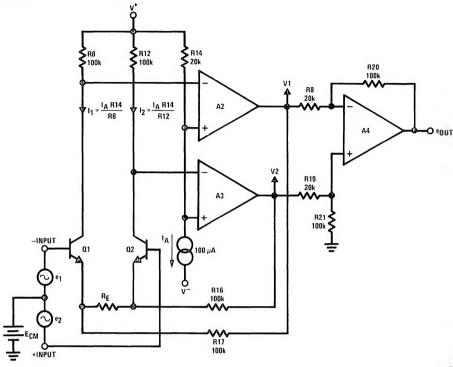

The LH0038 is a 3-stage, true instrumentation amplifier composed of a well matched transistor differential pair, Q1 and Q2, a common-mode loop amplifier, A2 and A3, and a differential to single ended amplifier, A4. A simplified schematic is shown in *Figure 3*.

Current source, I<sub>A</sub>, establishes a voltage across R14 of approximately 2V, which results in a 2V drop across R8 and R12. This constant voltage forces the first stage current to

be 20  $\mu$ A per side. The action of A2 and A3 is such that 20  $\mu$ A is maintained constant despite the presence of common-mode signals. The differential outputs of A2 and A3 are applied to differential amplifier, A4, which converts the signal to a single-ended output and provides gain of 5. The total gain of the amplifier is, therefore, the fixed gain of 5 multiplied by the gain of the composite input stage.

FIGURE 3. LH0038 Simplified Schematic

TL/H/5543-9

The closed loop gain of the composite amplifier may be better understood by referring to Figure 3. The Q1-A2 loop may be viewed as differential amplifier with the inverting input at the base and non-inverting input at the emitter. Combining small signal AC and large signal DC analysis =

$$v1 = e1 \left( \frac{R17 + R_E}{R_E} \right) - e2 \left( \frac{R17}{R_E} \right) + E_{CM} - V_{BE1} - I_1R17$$

(1)

By similar analysis:

$$v2 = e2 \left( \frac{R16 + R_E}{R_E} \right) - e1 \left( \frac{R16}{R_E} \right) + E_{CM} - V_{BE2} - I_2R16$$

(2)

For I<sub>1</sub>  $\equiv$  I<sub>2</sub>, R17  $\equiv$  R16, V<sub>BE1</sub>  $\equiv$  V<sub>BE2</sub>, subtracting equation (1) from (2) results in:

$$v2 - v1 = (e2 - e1) \left( \frac{R16 + R_E}{R_E} \right) + (e2 - e1) \left( \frac{R16}{R_E} \right)$$

(3)

$$\frac{v2 - v1}{e2 - e1} = \frac{2R16}{R_E} + 1 \tag{4}$$

The differential input voltage (v2 - v1) is amplified by the closed loop gain of A4:

$$e_{OUT} = (A_{VCL4}) (e2 - e1)$$

(5)

where:

$$A_{VCL4} = \frac{R20}{R8} = 5.00$$

$$A_{VCL} = 5\left(\frac{2R16}{R_E} + 1\right) \tag{6}$$

As an example, with all gain pins open,  $R_E=10.525~k\Omega$ , and;

$$A_{VCL} = 5\left(\frac{(2)(100k)}{R_E} + 1\right) = 100.0$$

(7)

All other closed loop gain configurations place a precision resistor in parallel with  $R_E(R9+R10)$ . For example, for a gain of 200, pin 6 is connected to pin 10 and the gain is predicted by:

$$A_{VCL} = 5.00 \left[ \frac{(2) (100k)}{(10.526) \| (10.000k)} + 1 \right]$$

$$= (5.00) (40) = 200$$

(8)

# CLOSED LOOP GAIN CONSIDERATIONS USING INTERNAL RESISTORS

Table 1 summarizes the primary gain configurations available with the LH0038. Obviously, other gains are possible. Using the internally supplied resistors has the advantage that R16, R17, and R<sub>E</sub> all track thermally, minimizing the device's gain error as a function of temperature.

Gain adjustment by paralleling or series padding internally supplied resistors is generally discouraged since external resistors will generally not thermally track. It is recommended that the gain adjustment be done in a subsequent stage as shown in Figure 4.

FIGURE 4. Recommended Gain Adjust Circuit

TL/H/5543-10

**TABLE I. LH0038 Internal Gain Configurations**

|   | Overall<br>Gain | First<br>Stage<br>Gain | Pin<br>Configuration            | Effective<br>R <sub>E</sub> |  |  |  |  |

|---|-----------------|------------------------|---------------------------------|-----------------------------|--|--|--|--|

|   | 100             | 20                     | All Gain Pins Open              | 10.5260 kΩ                  |  |  |  |  |

|   | 200             | 40                     | Pin 6 to Pin 10                 | 5.1281 kΩ                   |  |  |  |  |

| ı | 400             | 80                     | Pin 6 to Pin 9, Pin 10 to Pin 5 | $2.5316~\mathrm{k}\Omega$   |  |  |  |  |

|   | 500             | 100                    | Pin 6 to Pin 10, Pin 9 to Pin 5 | 2.0202 k $\Omega$           |  |  |  |  |

|   | 1000            | 200                    | Pin 7 to Pin 10                 | 1.0050 kΩ                   |  |  |  |  |

|   | 2000            | 400                    | Pin 8 to Pin 10                 | 0.5013 kΩ                   |  |  |  |  |

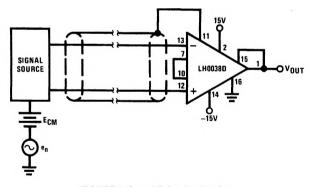

#### **GUARD DRIVE**

The LH0038 is provided with a guard drive output, which will always be at the input common-mode voltage. The guard

drive amplifier is short-circuit proof and is capable of driving several thousand pF without danger of latch-up or oscillation.

The guard drive tied to a shielded input cable will greatly reduce noise pick-up, and also improve AC CMRR by maintaining the shield at the common-mode voltage. Figure 5 illustrates the proper use of the guard drive. The guard drive output is also connected to the case to provide electrostatic shielding to the system.

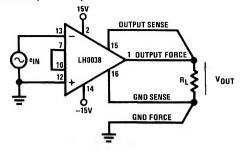

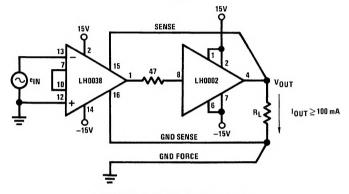

#### **REMOTE OUTPUT SENSE**

The feedback network of the LH0038 may be closed directly at the load in order to eliminate errors due to lead resistance. Also, a unity gain buffer; e.g. LH0002, may be included within the feedback loop to increase output current capability as shown in Figure 7.

FIGURE 5. Guard Drive Application

**FIGURE 6. Remote Sense Connection**

FIGURE 7. Output Buffer Connection

TL/H/5543-13

#### OFFSET NULL

Offset of the LH0038 is trimmed by the factory to a very low value. The offset may be further trimmed using a 10 k $\Omega$ , 10 turn, 100 ppm/°C potentiometer as shown in Figure 8. However, a drift increase of 0.3  $\mu$ V/°C will be caused for each 100  $\mu$ V of offset adjusted. The recommended offset null is shown in Figure 4 and is accomplished in the following stage.

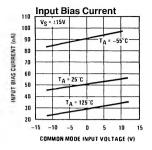

#### **BIAS CURRENT CONSIDERATIONS**

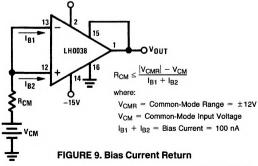

The LH0038 exhibits bias current of approximately 50 nA per side, and requires a path to ground or supply. The practical limitation to the maximum resistance between the inputs and ground is dicated by negative common-mode range as shown in *Figure 9*. For example, for  $V_{CM}=-10V, \, R_{CM} \leq 20 \, M\Omega.$

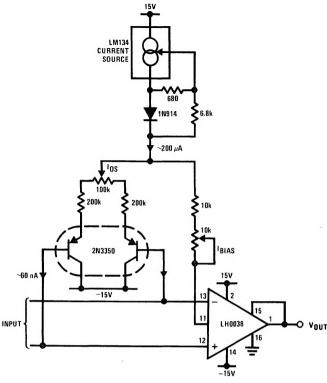

The LH0038 input stage bias was optimized for minimum voltage noise so the input bias currents are higher than might otherwise be expected. Note, however, that the input currents are very well matched, resulting in an offset current value much lower than one might infer from the bias current. In order to take advantage of this low offset current, the source impedances at both inputs should be matched to minimize DC drift. Further, bias current is relatively constant with temperature (as opposed to an FET stage), so one can consider bias current compensation schemes such as shown in *Figure 10*. The danger with such techniques is that the offset current and noise contributed by the bias current compensator will dominate the system noise.

TL/H/5543-12

TL/H/5543-14

FIGURE 8. Offset Adjust Circuit (See also Figure 4)

**FIGURE 10. Bias Current Compensation**

TL/H/5543-16

#### **SETTLING TIME**

The LH0038 has been purposely over-compensated, and is therefore remarkably free from any undesirable transient response. Small signal settling time is governed by gain-bandwidth product; large signal settling time is dominated by slew rate.

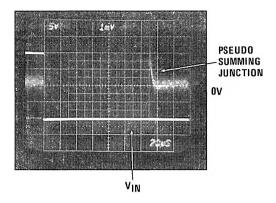

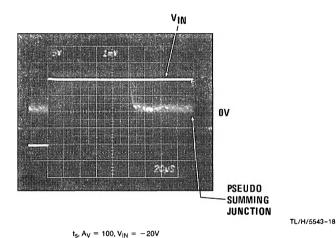

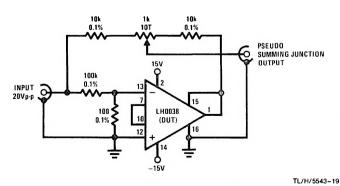

Figure 11 shows an input voltage step of +10V to -10V applied, through a 1000 to 1 voltage divider, to the device configured for an inverting gain of 1000. The output of the device will therefore be equal to the negative of the input after the device is completely settled. By resistively subtracting the input before the divider from the device output, a pseudo summing node is generated. The voltage at this pseudo summing junction goes "off screen" on the photos, since in the first small time increment the input goes instantaneously to -10 mV and the output is still at +10V. About 130  $\mu$ s after the input has gone negative, the output slews back in range and begins an exponential approach to the final value. Figure 12 is the same set-up for a -10V to +10V input pulse. Note that there is no overshoot in either case. The test circuit is shown in Figure 13.

#### **HIGH FREQUENCY CMRR**

The LH0038 resistor ratios are carefully trimmed for optimum CMRR at DC through 60 Hz. Inevitably, this rejection will degrade at higher frequencies due to 2 separate effects: stray capacitance mismatch and slew rate limiting in the in-

put stage. In most discrete instrumentation amplifier realizations, the stray capacitance mismatch dominates simply because the stray capacitances are relatively large (this can be trimmed out in a discrete amplifier). In a hybrid circuit such as the LH0038, stray capacitance is minimized, so the effects of mismatch are also minimized.

The response to a pulse or noise spike applied as a common-mode signal may be dominated by the slew characteristics of the input stage. Whenever the common-mode input slew rate exceeds 0.2 V/µs, the 2 input amplifiers will apply identical ramp signals to the final stage and cause its output to go to near 0V. Note that the amplifier is not really active under these conditions as normal mode signal variations will not be coupled to the output. Some time may be required for the amplifier to settle after a transient of this kind before the output can be considered representative of the input. Slew rate limiting will not normally be the limiting factor for sine wave common-mode signals as 0.2 V/µs corresponds to about 2 kHz (20 Vp-p).

#### **POWER SUPPLY DECOUPLING**

Although the LH0038 exhibits in excess of 120 dB PSRR at DC, the figure degrades to 100 dB at 120 Hz. It is recommended that both V $^+$  and V $^-$  leads be by-passed with 1  $\mu F$  electrolytic in shunt with 0.01  $\mu F$  ceramic disc no further than 1 inch from the device.

$t_{S}, A_{V} = 100, V_{IN} = -20V$

FIGURE 11. Settling Time

FIGURE 12. Settling Time

FIGURE 13. Settling Time Test Circuit

FIGURE 14. Settling Time

#### **Definition of Terms**

Bandwidth: That frequency at which the voltage gain is reduced to 3 dB below the low frequency.

Common-Mode Rejection Ratio, CMRR: The ratio of the input common-mode voltage range to the peak-to-peak change in input offset voltage over this range.

Input Offset Voltage,  $V_{IOS}$ : The voltage which must be applied to the inputs to force the outputs of the input stage to 0V.  $V_{IOS}$  can be calculated by measuring  $V_{OS}$  at closed loop gains of 100 and 2000 and using the following equation:

$$V_{IOS} = \frac{(V_{OS}) \, 2k - (V_{OS}) \, 100}{1900}$$

Where:

$(V_{OS})2k$  = overall offset voltage for  $A_{VCL}$  = 2k.

$(V_{OS})100$  = overall offset voltage for  $A_{VCL}$  = 100.

**Gain Non-Linearity:** The deviation of the gain from a straight line drawn through the end points expressed as a percent of full-scale (10V for operations on  $\pm\,15V$  supply). Note that this is a more stringent specification than deviation from the best straight line and is double the number that would be specified if the percentage were based on a 20V ( $\pm\,10V$ ) range.

Guard Voltage Error: The voltage difference between the guard drive output and the average of the 2 input voltages.

Input Bias Current, IB: The average of the 2 input currents.

Input Common-Mode Voltage Range, V<sub>INCM</sub>: The range of voltages on the input terminals for which the amplifier is operational. Note that the specifications are not guaranteed over the full common-mode voltage range unless specifically stated.

**Input Offset Current, I<sub>OS</sub>:** The difference in the currents into the 2 input terminals when the output is at zero.

**Input Resistance:** The ratio of the change in input voltage to the change in input current on either input with the other grounded.

**Overall Offset Voltage, V<sub>OS</sub>:** The output voltage when both inputs are connected to 0V.  $V_{OS}$  is composed of input amplifier offset voltage effects,  $V_{IOS}$ , and output amplifier effects,  $V_{OOS}$ . It is given by:

$$V_{OS} = (A_{VCL})(V_{IOS}) - V_{OOS}$$

Where:

A<sub>VCI</sub> = closed loop gain = 100 to 2k

V<sub>IOS</sub> = input stage offset voltage

$V_{OOS}$  = output stage offset voltage

Output Offset Voltage,  $V_{OOS}$ : The output voltage when theoutputs of the input stage are forced to 0V.  $V_{OOS}$  may be calculated by measuring  $V_{OS}$  at closed loop gains of 100 and 2000 and using the following equation:

$$V_{OOS} = (20) (V_{OS}) 100 - (V_{OS}) 2k$$

Where:

( $V_{OS}$ ) 100 = overall offset voltage for  $A_{VCL}$  = 100

(VOS) 2k = overall offset voltage for AvcI

Output Voltage, Vo: The peak output voltage swing, referred to zero.

Offset Voltage Temperature Drift,  $\Delta V_{IOS}/\Delta T$ : The average drift rate of offset voltage for a thermal variation from room temperature to the indicated temperature extreme.

Power Supply Rejection Ratio, PSRR: The ratio of the change in input offset voltage to the change in power supply voltages producing it.

Settling times, t<sub>s</sub>: The time between the initiation of the input step function and the time when the output voltage has settled to within a specified error band of the final output voltage.

Slew Rate, S<sub>r</sub>: The internally-limited rate of change in output voltage with a large-amplitude step function applied to the input.

**Supply Current**,  $\pm l_s$ : The current required from the power supply to operate the amplifier with no load and the output midway between the supplies.

Supply Voltage Range: The range of voltages on the supply terminals for which the device is operational. Note that the specifications are not guaranteed over the full supply voltage range unless specifically stated.

**Transient Response,** t<sub>r</sub>: The closed-loop step-function response of the amplifier under small-signal conditions.

Unity Gain Bandwidth: The frequency range from DC to the frequency where the amplifier open loop gain rolls off to 1.

Closed Loop Gain, A<sub>VCL</sub>: The ratio of output voltage to input voltage under the stated conditions of source resistance (R<sub>S</sub>) and load resistance (R<sub>L</sub>).

Voltage Gain Error: The deviation in percent between the ideal voltage gain and the value obtained when the device is configured for that gain.