# 6/4-Bit VID Programmable Current DAC for Point of Load Regulators with Adjustable Start-Up Current

Check for Samples: LM10011

## FEATURES

- 1.0% Output Current Accuracy (0°C to +100°C)

- 1.25% Output Current Accuracy (–40°C to +125°C)

- Input Voltage Range: +2.97V to +5.5V

- Pin Selectable VID Format (6/4 bit)

- 16 Selectable Start-Up Currents

- Precision Enable to Support Custom UVLO

- SON-10 3mm x 3mm Footprint, 0.5mm Pitch

- Footprint Compatible with the LM10010

## **APPLICATIONS**

- Broadband, Networking, and Wireless

Communications

- Notebook Power Solutions

- Portable Instruments

- Battery-Powered Equipment

- Powering Digital Loads with a 6-bit or 4-bit, 4 Pin VID Interface

## DESCRIPTION

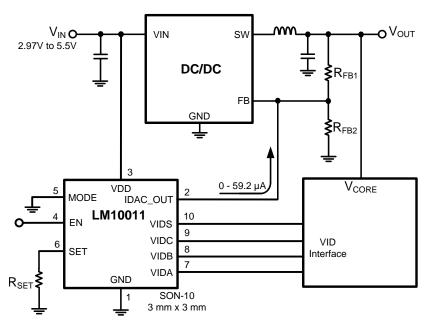

The LM10011 is a precision, digitally programmable device used to control the output voltage of a DC/DC converter. The LM10011 outputs a DC current proportional to a 6-bit or 4-bit input word. By connecting the IDAC\_OUT pin to the feedback node of a regulator, the regulator output voltage can be adjusted to a desired range and resolution set by the user. As the input word counts up, the output voltage is adjusted higher based on the values of the feedback resistors in the converter.

The current from the IDAC\_OUT pin on start-up is programmable by an external resistor to cover the range of 0 to  $56.4\mu$ A with 4 bits of resolution. The MODE pin allows programming of the device through a 4-bit parallel VID interface or through a 6-bit interface consisting of upper and lower 3-bit VID codes. The LM10011 is specifically designed to program a wide variety of Texas Instruments DC/DC converters for VID (Voltage Identification) applications.

## **TYPICAL APPLICATION CIRCUIT**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

$\overline{M}$

# LM10011

#### www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

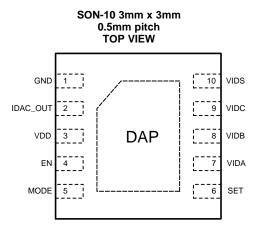

#### **CONNECTION DIAGRAM**

SNVS822 - DECEMBER 2012

#### **PIN DESCRIPTIONS**

| PII      | N   | DECODIDITION                                                                                                                                                                                      |  |  |  |  |  |  |  |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| NAME     | NO. | DESCRIPTION                                                                                                                                                                                       |  |  |  |  |  |  |  |

| GND      | 1   | Ground.                                                                                                                                                                                           |  |  |  |  |  |  |  |

| IDAC_OUT | 2   | Output pin of the current DAC that connects to the feedback node of the regulator.                                                                                                                |  |  |  |  |  |  |  |

| VDD      | 3   | Positive supply input. Operating voltage is 2.97V to 5.5V. It is recommended to add a small 1nF or greater bypass capacitor from this pin to GND.                                                 |  |  |  |  |  |  |  |

| EN       | 4   | Precision enable input. The LM10011 will operate when the EN pin voltage exceeds 1.34V.                                                                                                           |  |  |  |  |  |  |  |

| MODE     | 5   | MODE will set the VID operating mode. Connecting MODE to VDD will select a 4-bit parallel interface. Connecting MODE to GND will select a 4 pin, 6-bit interface.                                 |  |  |  |  |  |  |  |

| SET      | 6   | A resistor connected from SET to GND will set the start-up code (current) at the IDAC_OUT pin. There are 16 different start-up codes to select from.                                              |  |  |  |  |  |  |  |

| VIDA     | 7   | VID digital input. In 6-bit mode: Bit 0 when VIDS transitions low; Bit 3 when VIDS transitions high. In 4-bit mode: Bit 0.                                                                        |  |  |  |  |  |  |  |

| VIDB     | 8   | VID digital input. In 6-bit mode: Bit 1 when VIDS transitions low; Bit 4 when VIDS transitions high. In 4-bit mode: Bit 1.                                                                        |  |  |  |  |  |  |  |

| VIDC     | 9   | VID digital input. In 6-bit mode: Bit 2 when VIDS transitions low; Bit 5 when VIDS transitions high. In 4-bit mode: Bit 2.                                                                        |  |  |  |  |  |  |  |

| VIDS     | 10  | VID select line. In 6-bit mode: Transition low selects lower 3 bits, Transition high selects upper 3 bits and updates the IDAC_OUT current to reflect the present VID code. In 4-bit mode: Bit 3. |  |  |  |  |  |  |  |

| DAP      | DAP | Die Attach Pad. Not electrically connected to device, connect to system ground plane for reduced thermal resistance.                                                                              |  |  |  |  |  |  |  |

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted)

|                           |                  | MIN  | MAX  | UNIT |

|---------------------------|------------------|------|------|------|

| VDD, EN, IDAC_OUT, MODE   |                  | -0.3 | 6    | V    |

| VIDA, VIDB, VIDC, VIDS    |                  | -0.3 | 6    | V    |

| ESD Rating <sup>(3)</sup> | Human Body Model |      | 2    | kV   |

| Storage Temperature       | -65              | +150 | °C   |      |

| Junction Temperature      |                  |      | +150 | °C   |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(3) The human body model is a 100 pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin.

#### **OPERATING CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                        | MIN  | TYP MAX  | UNIT |

|----------------------------------|------|----------|------|

| VDD                              | 2.97 | 5.5      | V    |

| IDAC_OUT                         | -0.3 | VDD-1.75 | V    |

| VIDA, VIDB, VIDC, VIDS, EN, MODE | -0.3 | 5.5      | V    |

| Junction Temperature             | -40  | +125     | °C   |

| Ambient Temperature              | -40  | +125     | °C   |

#### THERMAL INFORMATION

|                    |                                                             | LM10011 |       |

|--------------------|-------------------------------------------------------------|---------|-------|

|                    | THERMAL METRIC <sup>(1)</sup>                               | SON-10  | UNITS |

|                    |                                                             | 10 PINS |       |

| θ <sub>JA</sub>    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 52.1    |       |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 30.6    |       |

| $\theta_{JB}$      | Junction-to-board thermal resistance <sup>(4)</sup>         | 26.8    | °C/W  |

| Ψ <sub>JT</sub>    | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.9     | °C/W  |

| $\Psi_{JB}$        | Junction-to-board characterization parameter <sup>(6)</sup> | 26.9    |       |

| $\theta_{JCbot}$   | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 7.7     |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### SNVS822 - DECEMBER 2012

### **ELECTRICAL CHARACTERISTICS**

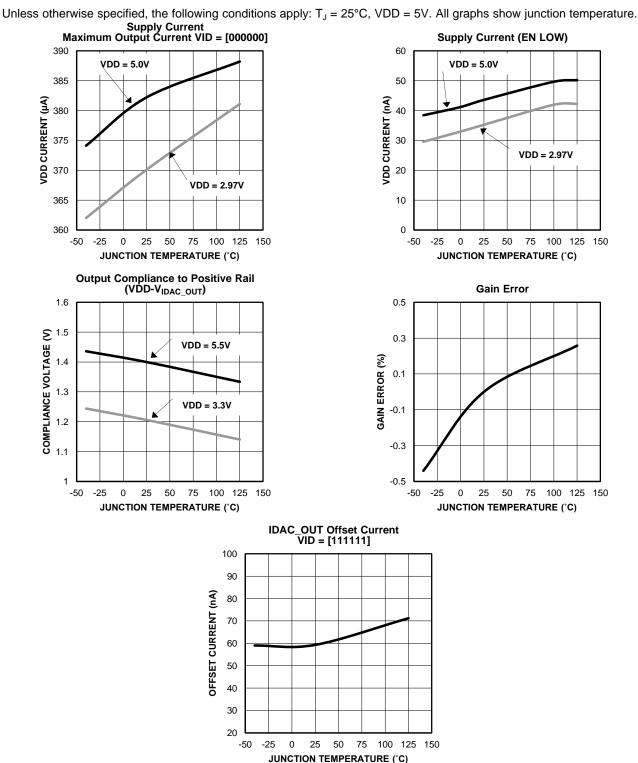

Limits in standard type are for  $T_J = 25^{\circ}$ C only. Limits appearing in boldface type apply over the full operating junction temperature range ( $-40^{\circ}$ C <  $T_J$  < +125°C). Unless otherwise noted, specifications apply to the Typical Application Circuit.

|                | PARAMETER                                  | TEST CONDITIONS                                           | MIN   | TYP  | MAX  | UNIT  |

|----------------|--------------------------------------------|-----------------------------------------------------------|-------|------|------|-------|

| Supply, UVLO   | , and Enable                               |                                                           |       |      |      |       |

| IQ             | Quiescent current                          | VDD=5.0V, V <sub>EN</sub> =2.0V                           |       | 260  | 300  | μA    |

| IQ_FS          | Quiescent current, IDAC_OUT =<br>IFS_6     | VDD=5.0V, V <sub>EN</sub> =2.0V, IFS_6                    |       | 382  |      | μΑ    |

| IQ_DIS         | Quiescent current disabled                 | VDD=5.0V, V <sub>EN</sub> =0.0V                           |       | 45   | 65   | μA    |

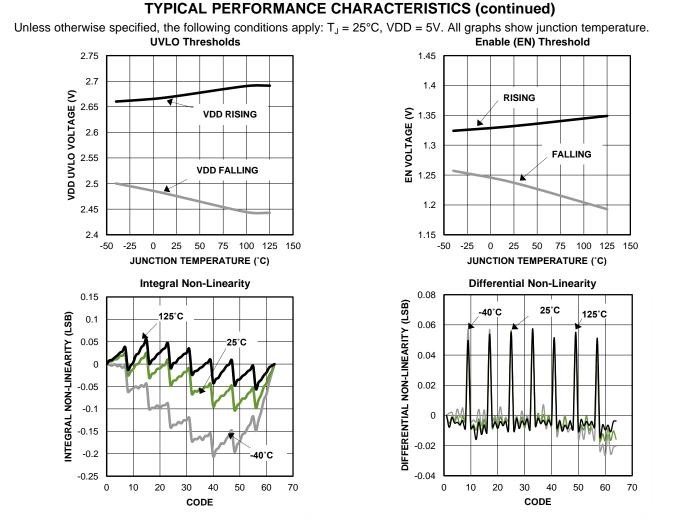

| VUVLO_R        | Under voltage rising threshold             | VDD Rising                                                |       | 2.65 | 2.95 | V     |

| VUVLO_F        | Under voltage falling threshold            | VDD Falling                                               | 2.2   | 2.45 |      | V     |

| VUVLO_HYS      | Hysteresis                                 |                                                           |       | 200  |      | mV    |

| VEN            | Enable rising threshold                    | V <sub>EN</sub> Rising                                    | 1.20  | 1.34 | 1.45 | V     |

| VEN_HYS        | Enable hysteresis                          |                                                           | 50    | 100  | 180  | mV    |

| IEN            | Enable pull-up current                     |                                                           |       | 2    |      | μA    |

| IDAC_OUT       |                                            |                                                           |       |      |      |       |

| ACC            | Accuracy                                   | Measured at full scale                                    | -1.25 |      | 1.25 | %     |

| ACC            | Accuracy                                   | Measured at full scale, 0°C to 100°C                      | -1.0  |      | 1.0  | %     |

| LSB_6          | DAC step size, 6-bit mode                  | IFS_6/(2 <sup>6</sup> -1)                                 |       | 940  |      | nA    |

| LSB_4          | DAC step size, 4-bit mode                  | IFS_4 /(2 <sup>4</sup> -1)                                |       | 3.76 |      | μA    |

| IFS_6          | Full-scale output current (6-bit mode)     | VID[5:0] = 000000b                                        |       | 59.2 |      | μA    |

| IFS_4          | Full-scale output current (4-bit mode)     | VID[3:0] = 0000b                                          |       | 56.4 |      | μΑ    |

| INL            | Integral non-linearity                     |                                                           | -1    |      | 1    | LSB_6 |

| DNL            | Differential non-linearity                 |                                                           | -0.25 |      | 0.25 | LSB_6 |

| OFFSET         | Offset current                             | VID[5:0] = 111111b (6-bit), VID[3:0] = 1111b (4-bit)      |       | 60   |      | nA    |

| VOUT_MAX       | IDAC_OUT compliance voltage                | VDD=3V, VDD-VIDAC_OUT                                     |       |      | 1.75 | V     |

| Start-Up Set C | Current                                    |                                                           |       |      |      |       |

| VSETFSR        | SET pin voltage FSR                        |                                                           | 1.12  | 1.2  | 1.23 | V     |

| SETRES         | SET ADC resolution                         |                                                           |       | 4    |      | bits  |

| SETRNG         | SET ADC current full-scale range           |                                                           |       | 56.4 |      | μA    |

| ISET           | SET Current                                |                                                           | 4.75  | 5.1  | 5.40 | μA    |

| SET0           | Start-up DAC error, code 0                 | $R_{SET} = 0\Omega$ , $I_{DAC OUT} = 56.4 \mu A$          | 0     |      | 0    | LSB   |

| SET1           | Start-up DAC error, code 1                 | $R_{SET} = 21.0 k\Omega^{(1)}, I_{DAC OUT} = 52.7 \mu A$  | 0     |      | 0    | LSB   |

| SET2           | Start-up DAC error, code 2                 | $R_{SET} = 35.7 k\Omega^{(1)}, I_{DAC OUT} = 48.9 \mu A$  | 0     |      | 0    | LSB   |

| SET3           | Start-up DAC error, code 3                 | $R_{SET} = 51.1 k\Omega^{(1)}, I_{DAC_OUT} = 45.2 \mu A$  | 0     |      | 0    | LSB   |

| SET4           | Start-up DAC error, code 4 <sup>(2)</sup>  | $R_{SET} = 71.5 k\Omega^{(1)}, I_{DAC OUT} = 41.4 \mu A$  | 0     |      | +1   | LSB   |

| SET5           | Start-up DAC error, code 5 <sup>(2)</sup>  | $R_{SET} = 86.6 k \Omega^{(1)}, I_{DAC_OUT} = 37.7 \mu A$ | 0     |      | +1   | LSB   |

| SET6           | Start-up DAC error, code 6 <sup>(2)</sup>  | $R_{SET} = 105 k \Omega^{(1)}, I_{DAC_OUT} = 33.9 \mu A$  | 0     |      | +1   | LSB   |

| SET7           | Start-up DAC error, code 7 <sup>(2)</sup>  | $R_{SET} = 118 k \Omega^{(1)}, I_{DAC_OUT} = 30.1 \mu A$  | 0     |      | +1   | LSB   |

| SET8           | Start-up DAC error, code 8 <sup>(2)</sup>  | $R_{SET} = 140 k \Omega^{(1)}, I_{DAC_OUT} = 26.4 \mu A$  | 0     |      | +1   | LSB   |

| SET9           | Start-up DAC error, code 9 <sup>(2)</sup>  | $R_{SET} = 154 k \Omega^{(1)}, I_{DAC_OUT} = 22.6 \mu A$  | 0     |      | +1   | LSB   |

| SET10          | Start-up DAC error, code 10 <sup>(2)</sup> | $R_{SET} = 169k\Omega^{(1)}, I_{DAC_OUT} = 18.8\mu A$     | 0     |      | +1   | LSB   |

| SET11          | Start-up DAC error, code 11 <sup>(2)</sup> | $R_{SET} = 182k\Omega^{(1)}, I_{DAC_OUT} = 15.1\mu A$     | 0     |      | +1   | LSB   |

| SET12          | Start-up DAC error, code 12 <sup>(2)</sup> | $R_{SET} = 200 k \Omega^{(1)}, I_{DAC OUT} = 11.3 \mu A$  | 0     |      | +1   | LSB   |

| SET13          | Start-up DAC error, code 13 <sup>(2)</sup> | $R_{SET} = 215k\Omega^{(1)}, I_{DAC_OUT} = 7.59\mu A$     | 0     |      | +1   | LSB   |

| SET14          | Start-up DAC error, code 14 <sup>(2)</sup> | $R_{SET} = 237 k \Omega^{(1)}, I_{DAC OUT} = 3.80 \mu A$  | 0     |      | +1   | LSB   |

(1)

$R_{SET}$  is based on 1% E96 standard resistor values. "+1" LSB implies a positive step in CODE. LSB is in reference to LSB\_4. (2)

#### **ELECTRICAL CHARACTERISTICS (continued)**

Limits in standard type are for  $T_J = 25^{\circ}$ C only. Limits appearing in boldface type apply over the full operating junction temperature range (-40°C <  $T_J$  < +125°C). Unless otherwise noted, specifications apply to the Typical Application Circuit.

|                       | PARAMETER                                 | TEST CONDITIONS                                         | MIN  | TYP | MAX  | UNIT |  |

|-----------------------|-------------------------------------------|---------------------------------------------------------|------|-----|------|------|--|

| SET15                 | Start-up DAC error, code 15               | $R_{SET} = 301 k\Omega^{(1)}, I_{DAC_OUT} = 0.06 \mu A$ | 0    |     | 0    | LSB  |  |

| ID Logic In           | outs <sup>(3)</sup>                       |                                                         |      |     |      |      |  |

| V <sub>IL</sub>       | Input voltage low                         |                                                         |      |     | 0.75 | V    |  |

| VIH                   | Input voltage high                        |                                                         | 1.0  |     |      | V    |  |

| IIL                   | Input current low                         |                                                         | -3.5 |     |      | μA   |  |

| I <sub>IH</sub>       | Input current high                        |                                                         |      |     | 5    | μA   |  |

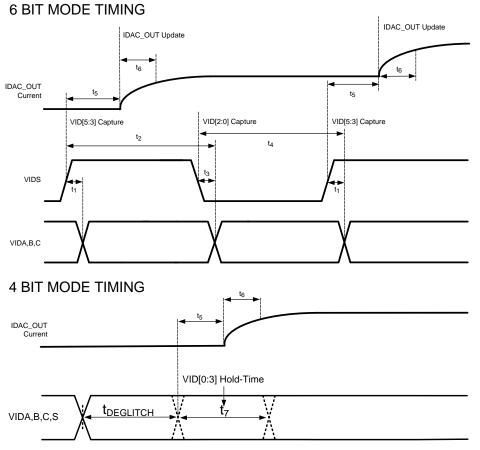

| t <sub>DEGLITCH</sub> | Input deglitch time                       |                                                         |      | 3.6 |      | μs   |  |

| t <sub>1</sub>        | Input delay time                          | VIDS rising edge                                        |      |     | 1    | μs   |  |

| t <sub>2</sub>        | Input hold time VIDA, VIDB, VIDC valid    | VIDS falling edge                                       | 20   |     |      | μs   |  |

| t <sub>3</sub>        | Input delay time                          | VIDS falling edge                                       |      |     | 1    | μs   |  |

| t <sub>4</sub>        | Input hold time VIDA, VIDB, VIDC valid    | VIDS rising edge                                        | 20   |     |      | μs   |  |

| t <sub>5</sub>        | Delay to beginning of IDAC_OUT transition | Measured from VIDS rising edge                          |      | 6.3 | 10   | μs   |  |

| t <sub>6</sub>        | IDAC_OUT transition time                  | Time constant for exponential rise                      |      | 40  |      | μs   |  |

| t <sub>7</sub>        | Minimum hold time in 4-bit mode           | VIDA, VIDB, VIDC, VIDS                                  |      | 4.4 |      | μs   |  |

(3) For VID timing, see TIMING DIAGRAM

#### SNVS822 - DECEMBER 2012

#### **TIMING DIAGRAM**

Figure 1. Timing Diagram for LM10011 Communications

LM10011

www.ti.com

SNVS822 - DECEMBER 2012

www.ti.com

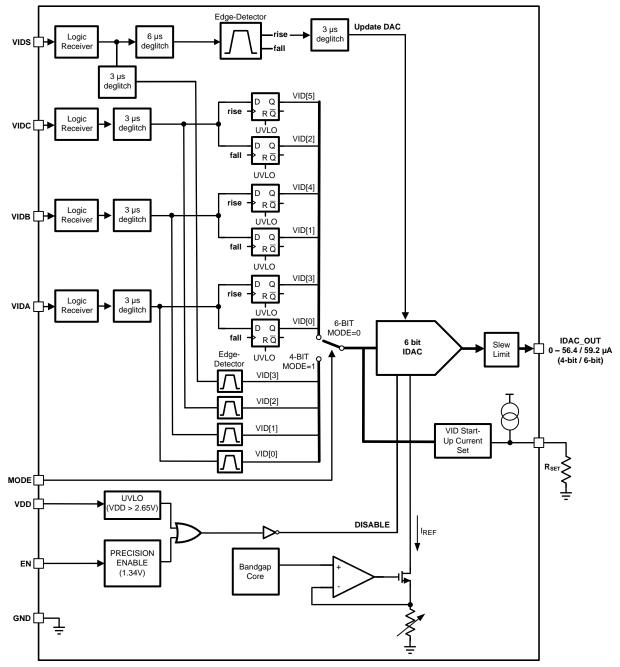

#### **BLOCK DIAGRAM**

Figure 2. LM10011 Block Diagram

SNVS822 - DECEMBER 2012

www.ti.com

## **FUNCTIONAL DESCRIPTION**

#### GENERAL

The LM10011 is a precision current DAC used for controlling any point of load regulator with an adjustable resistor feedback network. Four VID communication lines (VIDA,B,C,S) are used to write a 6-bit or 4-bit VID value. The output of the IDAC (IDAC\_OUT) is used to inject a precision current into the feedback node of a regulator, thus adjusting the output voltage. With this method, it is possible to precisely control the output voltage of the regulator.

An enable pin (EN) is provided to allow for a reduced quiescent current when not in use. Also, the VDD line is monitored so that an under-voltage event will shut-down the LM10011 (IDAC\_OUT =  $0.0\mu$ A).

The device is available in a 10-pad No-Pullback Package (SON-10). The LM10011 can be used in numerous applications with regulators from 2.97V to 5.5V supplies. A block diagram of the LM10011 is shown in Figure 2.

#### THEORY OF OPERATION

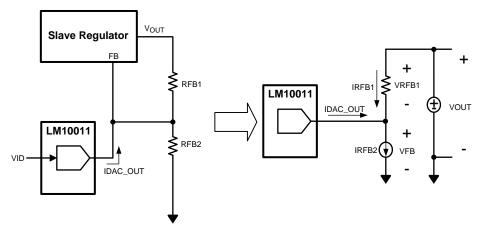

The LM10011 can be treated as a D/A converter, converting digital VID codes to analog outputs. The LM10011 DAC analog output is a current that flows out of the IDAC\_OUT pin. The IDAC\_OUT pin is intended to be connected to the feedback node of a voltage regulator as shown in Figure 3. In a typical voltage regulator, the current in  $R_{FB2}$  is constant by virtue of the regulator feedback loop maintaining the reference voltage at the feedback node. The current flowing through  $R_{FB2}$  is the same current flowing through  $R_{FB1}$ . When current is injected into the feedback node by the LM10011, less current is required from the  $R_{FB1}$  resistor. The consequence of this is that the output voltage of the regulator will decrease to maintain the total amount of current in  $R_{FB2}$  in order to regulate at the correct feedback (reference) voltage.

Each VID code corresponds to a different IDAC\_OUT current and thus a different output voltage. Increasing the VID code lowers the IDAC\_OUT current and raises the output voltage. Decreasing the VID code raises the IDAC\_OUT current and lowers the output voltage. All VID codes are decoded into a 6-bit or 4-bit current DAC output whether the MODE equals 0 (connected to GND) or 1 (connected to VDD).

Figure 3. Output Voltage (V<sub>OUT</sub>) is Controlled Via Current Injection into the Feedback Node

#### CURRENT DAC

The LM10011 current DAC is based on a low voltage bandgap reference setting a current through a precision adjustable resistor. This bandgap is trimmed for precision and gives excellent performance over temperature. The output current has a maximum full-scale range [VID = 00000b] of 59.2µA and is adjustable with a 6/4-bit VID word. This allows for 64/16 settings, with a resolution of 940nA / 3.76µA respectively. The current DAC also has a slew limit to prevent abrupt changes in the output. The slew limit is represented as a time constant,  $t_6 = 40\mu$ s, in the Electrical Characteristics table. A deglitch filter for the VID inputs provides noise immunity and effectively adds a small delay from the transition of a VID line to the change in IDAC\_OUT current.

#### **VID PROGRAMMING, 6-BIT MODE**

Four pins are used to communicate with the LM10011. In 6-bit mode (MODE=0), VIDA, VIDB, and VIDC are data lines, while VIDS is a latching strobe that programs in the LM10011 data. As shown in the timing diagram in Figure 1, the falling edge of VIDS latches in the data from VIDA, VIDB, and VIDC as the lower three LSB of the IDAC\_OUT value, [2:0]. After a minimum hold time ( $t_2$ ), the rising edge of VIDS latches in the data from VIDA, VIDB, and VIDC as the upper three LSB of the IDAC\_OUT value, [5:3]. Internally, a delay ( $t_3$ , $t_1$ ) on VIDS allows for the setting of all VIDA, B, C lines to change simultaneously as VIDS rises or falls.

#### **VID PROGRAMMING, 4-BIT MODE**

The LM10011 includes a 4-bit mode to facilitate parallel VID communication. In 4-bit mode (MODE=1), VIDC, VIDB, VIDA and VIDS are all parallel data lines. As shown in the timing diagram in Figure 1, a changing edge of any of the VID communication lines will change the IDAC\_OUT current to the corresponding new 4-bit value found on the data lines. There is a 3µs deglitch filter to eliminate spurious noise events. The data must overcome the deglitch time and the minimum hold time ( $t_7$ ) or else the IDAC\_OUT pin current may not reflect the value indicated at the VID data inputs. During the hold time, no other data line can be transitioned.

As mentioned in a previous section, for both the 4-bit and 6-bit mode, the VID data word is set so that the lowest output current is seen at the highest VID data word (59.2µA at a code of 0d in 6-bit mode and 56.4µA in 4-bit mode). Conversely, the lowest current is seen at the highest VID data word (0.06µA at 63d/15d). During VID operation with the regulator, this will translate to the lowest output voltage with the lowest VID word, 0d, and the highest output voltage with the highest VID word, 63d or 15d. The communications pins can be used with a low voltage microcontroller, with a maximum  $V_{IL}$  of 0.75V and a minimum  $V_{IH}$  of 1.0V.

#### PROGRAMMING THE START-UP CURRENT

Depending on the value of  $R_{SET}$  during start-up (when VDD>VUVLO\_R and EN>VEN), the output current on the IDAC\_OUT pin will take on one of 16 discrete values corresponding to the currents available in the 4-bit mode. These discrete start-up currents can be programmed by connecting a resistor ( $R_{SET}$ ) from the SET pin to GND. If the EN voltage is toggled or a UVLO is triggered during operation, the current will default back to the value set by the  $R_{SET}$  resistor. It takes only one VID command transition in either 4-bit or 6-bit mode to change the current to something other than the pre-programmed start-up current. The required  $R_{SET}$  resistors and their corresponding start-up currents codes can be found in Table 1.

| VID Code    | Nominal IDAC_OUT Current (μA) | R <sub>SET</sub> (kΩ) |

|-------------|-------------------------------|-----------------------|

| 0000b (0d)  | 56.4                          | 0                     |

| 0001b (1d)  | 52.7                          | 21.0                  |

| 0010b (2d)  | 48.9                          | 35.7                  |

| 0011b (3d)  | 45.2                          | 51.1                  |

| 0100b (4d)  | 41.4                          | 71.5                  |

| 0101b (5d)  | 37.7                          | 86.6                  |

| 0110b (6d)  | 33.9                          | 105                   |

| 0111b (7d)  | 30.1                          | 118                   |

| 1000b (8d)  | 26.4                          | 140                   |

| 1001b (9d)  | 22.6                          | 154                   |

| 1010b (10d) | 18.8                          | 169                   |

| 1011b (11d) | 15.1                          | 182                   |

| 1100b (12d) | 11.3                          | 200                   |

| 1101b (13d) | 7.59                          | 215                   |

| 1110b (14d) | 3.80                          | 237                   |

| 1111b (15d) | 0.06                          | 301                   |

Table 1. Start-Up / 4-Bit Mode Currents with Corresponding R<sub>SET</sub> Values and Output Currents.

#### SNVS822 -DECEMBER 2012

www.ti.com

Codes 0100b (4d) through 1110b (14d) will start-up into either the selected code or 1 code higher. This means that the output voltage of the POL may start-up into the selected output voltage or 1 LSB higher.

#### **ENABLE PIN AND UVLO**

The enable (EN) pin allows the output of the device to be enabled or disabled (IDAC\_OUT =  $0.0\mu$ A) with an external control signal. This pin is a precision analog input that enables the device when the voltage exceeds 1.34V. The EN pin has 100 mV of hysteresis and will disable the output when the enable voltage falls below 1.23V. If EN is not used, it can be left open, and will be pulled high by an internal 2µA current source. Since the EN pin has a precise turn-on threshold it can be used along with an external resistor divider network from VDD to configure the device to turn-on at a precise input voltage.

The LM10011 has a built-in under-voltage lockout (UVLO) protection circuit that keeps the device from operating until the input voltage reaches 2.65V (typical). The UVLO threshold has 200 mV of hysteresis that keeps the LM10011 from responding to power-on glitches during start-up. Note that descending below the EN voltage and/or the UVLO voltage are functionally the same as a reset. Bringing the device back from a low enable setting or from a VDD UVLO event will reset the IDAC\_OUT current to its start-up R<sub>SET</sub> setting.

#### **APPLICATION INFORMATION**

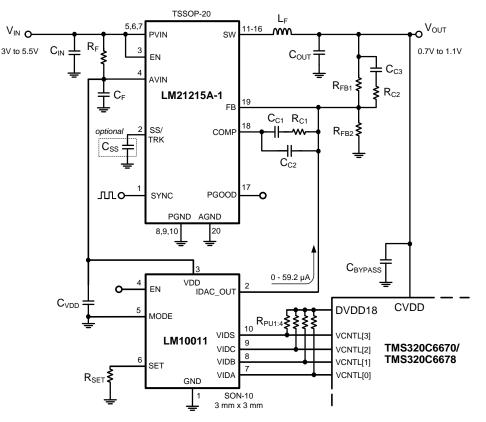

#### 6-Bit MODE DESIGN EXAMPLE

In this example, an LM21215A-1 is used as the voltage regulator and the desired range of output voltage operation is 0.7V to 1.1V. The LM10011 can provide control of the output voltage within this range with 6 bits or 4 bits of resolution. For this example, the 400mV of voltage range translates to a  $V_{OUT\_LSB}$  of 400mV/63 = 6.4mV (26.7mV in 4-bit mode) at the regulator output. In this calculation, 1% resistor values are used. A schematic for this example is shown in Figure 4.

Figure 4. Typical Application Circuit

#### SETTING THE V<sub>OUT</sub> RANGE AND LSB

Looking at the Typical Application Circuit in Figure 4, the following equation defines  $V_{OUT}$  of a given regulator (valid for  $V_{OUT} > V_{FB}$ ):

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R_{FB1}}{R_{FB2}}\right) - IDAC_OUT \times R_{FB1}$$

Here, the output voltage is a function of the resistor divider from R<sub>FB1</sub> and R<sub>FB2</sub>. Using the LM10011, there is a current supplied by the IDAC\_OUT pin that helps drive current through the feedback resistor R<sub>FB2</sub>, thus lowering the necessary current supplied through R<sub>FB1</sub>, and hence lowering V<sub>OUT</sub>. To calculate the nominal (maximum) V<sub>OUT</sub>, use an IDAC\_OUT value of 0µA.

The change in the output voltage can be analyzed based on the resolution of the current DAC from the LM10011 compared to the desired resolution of the output swing of the regulator.  $R_{FB1}$  is designed to provide the desired  $V_{OUT\_LSB}$  with the equation:

$$V_{OUT\_LSB} = LSB \times R_{FB1}$$

Copyright © 2012, Texas Instruments Incorporated

(1)

#### SNVS822 - DECEMBER 2012

TEXAS INSTRUMENTS

www.ti.com

(5)

(7)

Where LSB = LSB\_6 (940nA) from the EC table. Based on the desired nominal  $V_{OUT}$  (with IDAC\_OUT = 0µA) and the calculated  $R_{FB1}$  from Equation 2,  $R_{FB2}$  can be solved using Equation 1.

#### **4-Bit MODE DESIGN EXAMPLE**

Designing with the LM10011 in 4-bit mode is similar to designing in 6-bit mode. The only differences are the LSB value (LSB = LSB\_4=  $3.76\mu$ A) in Equation 2 and full scale current range (IDAC\_OUT =  $56.4\mu$ A).

#### Setting the Start-Up Voltage with R<sub>SET</sub>

$R_{SET}$  is chosen depending on the required start-up voltage for the particular application. The user must use Equation 3 and solve for the required IDAC\_OUT by inputting the known values of  $R_{FB1}$  and  $R_{FB2}$ ,  $V_{FB}$ , and the desired start-up output voltage,  $V_{OUT}$ . Once IDAC\_OUT is solved for, choose an  $R_{SET}$  based on Table 1 to select a start-up code to yield a current closely matching the calculated result. Use the equation below to solve for the required IDAC\_OUT value at start-up.

$$IDAC\_OUT = \frac{1}{R_{FB1}} \left( V_{FB} x \left( 1 + \frac{R_{FB1}}{R_{FB2}} \right) - V_{OUT} \right)$$

<sup>(3)</sup>

#### **EXAMPLE SOLUTION**

While in 6-bit mode, assuming a 400mV output range, 64 VID codes, and an IDAC LSB of 0.940 $\mu$ A, it is desired to have a V<sub>OUT</sub> with an LSB of 6.4mV and a default value of 1.1V with a 1.05V start-up voltage using an LM21215A-1 regulator (V<sub>FB</sub> = 0.6V):

$$6.4 \text{mV} = 0.940 \mu \text{A x R}_{\text{FB1}}$$

(4)

$$R_{FB1} = 6.8 k\Omega$$

Using 1% standard resistor values,  $R_{FB1}$  can be set to 6.81k $\Omega$ . Now calculate  $R_{FB2}$  based on  $R_{FB1}$  and the maximum  $V_{OUT}$  of 1.1V using Equation 1.

$$1.1V = .6V \times \left(1 + \frac{6.81 k\Omega}{R_{FB2}}\right) - 0V$$

(6)

$R_{FB2} = 8.1 k\Omega$

Using 1% standard resistor values,  $R_{FB2}$  can be set to 8.06k $\Omega$ . This will yield a regulator output range of 0.704V (CODE 0d) to 1.107V (CODE 63d). Values calculated here will be dependent on the accuracy of the regulator, the LM10011 IDAC\_OUT, and the resistor values used in the circuit.

Table 2 shows the codes and some of the resultant values of the IDAC current and the corresponding regulator output voltage for the previous example.

| VID Code      | IDAC_OUT Current (µA) | Regulator Voltage (V) |  |  |

|---------------|-----------------------|-----------------------|--|--|

| 000000b (0d)  | 59.2                  | 0.704                 |  |  |

| 000001b (1d)  | 58.3                  | 0.710                 |  |  |

| 000010b (2d)  | 57.4                  | 0.716                 |  |  |

| 000011b (3d)  | 56.4                  | 0.729                 |  |  |

|               |                       |                       |  |  |

| 111100b (60d) | 2.87                  | 1.087                 |  |  |

| 111101b (61d) | 1.93                  | 1.094                 |  |  |

| 111110b (62d) | 1.00                  | 1.100                 |  |  |

| 111111b (63d) | 0.06                  | 1.107                 |  |  |

Table 2. 6-Bit VID Codes with IDAC Current and Regulator Voltage for the Example in Figure 4.

The required IDAC\_OUT value during start-up can be calculated based on the desired start-up voltage of 1.05V and the  $R_{FB1}$  and  $R_{FB2}$  resistors found in the previous calculations. Using Equation 3 to solve for the required start-up IDAC\_OUT current results in a start-up current of 8.36µA.

$$IDAC\_OUT = \frac{1}{6.81k\Omega} \left[ 0.6V \, x \left[ 1 + \frac{6.81k\Omega}{8.06k\Omega} \right] - 1.05V \right] = 8.36\mu A$$

<sup>(8)</sup>

Choose a resistor in Table 1 that selects a start-up code that produces a current close to 8.36µA. An R<sub>SET</sub> of 215k $\Omega$  selects a nominal start-up code of 13d yielding a current of 7.59µA and start-up voltage of 1.054V. Note that using an R<sub>SET</sub> of 215k $\Omega$  may also select a code of 14d (+1 LSB) yielding a current of 3.80µA and a start-up voltage of 1.081V

#### PC BOARD GUIDELINES

The following guidelines should be followed when designing the PC board for the LM10011:

- Place the LM10011 close to the regulator feedback pin to minimize the FB trace length.

- Place a small capacitor, C<sub>VDD</sub>, (1nF) directly adjacent to the VDD and GND pins of the LM10011 to help minimize transients which may occur on the input supply line.

- The high current path from the board's input to the load and the return path should be parallel and close to each other to minimize loop inductance.

- The ground connections for the various components around the LM10011 should be connected directly to each other, and to the LM10011's GND pins, and then connected to the system ground at one point. Do not connect the various component grounds to each other through the high current ground line.

- For additional information about the operation of the regulator, please consult the respective datasheet and application notes on the respective evaluation boards.

## **IDAC\_OUT Current Values**

# Table 3. IDAC\_OUT Currents and Corresponding VID Codes.

| VID Code (6-Bit [4-Bit]) | IDAC Current (µA) |

|--------------------------|-------------------|

| Od                       | 59.2              |

| 1d                       | 58.3              |

| 2d                       | 57.4              |

| 3d [0d]                  | 56.4              |

| 4d                       | 55.5              |

| 5d                       | 54.6              |

| 6d                       | 53.6              |

| 7d [1d]                  | 52.7              |

| 8d                       | 51.7              |

| 9d                       | 50.8              |

| 10d                      | 49.8              |

| 11d [2d]                 | 48.9              |

| 12d                      | 48.0              |

| 13d                      | 47.0              |

| 14d                      | 46.1              |

| 15d [3d]                 | 45.2              |

| 16d                      | 44.2              |

| 17d                      | 43.3              |

| 18d                      | 42.3              |

| 19d [4d]                 | 41.4              |

| 20d                      | 40.5              |

| 21d                      | 39.5              |

| 22d                      | 38.6              |

| 23d [5d]                 | 37.7              |

| 24d                      | 36.7              |

| 25d                      | 35.7              |

| 26d                      | 34.8              |

| 27d [6d]                 | 33.9              |

| 28d                      | 33.0              |

| 29d                      | 32.0              |

| 30d                      | 31.1              |

| 31d [7d]                 | 30.1              |

# Table 3. IDAC\_OUT Currents and Corresponding VID Codes. (continued)

| VID Code (6-Bit [4-Bit]) | IDAC Current (µA) |

|--------------------------|-------------------|

| 32d                      | 29.2              |

| 33d                      | 28.2              |

| 34d                      | 27.3              |

| 35d [8d]                 | 26.4              |

| 36d                      | 25.4              |

| 37d                      | 24.5              |

| 38d                      | 23.6              |

| 39d [9d]                 | 22.6              |

| 40d                      | 21.6              |

| 41d                      | 20.7              |

| 42d                      | 19.8              |

| 43d [10d]                | 18.8              |

| 44d                      | 17.9              |

| 45d                      | 17.0              |

| 46d                      | 16.0              |

| 47d [11d]                | 15.1              |

| 48d                      | 14.1              |

| 49d                      | 13.2              |

| 50d                      | 12.3              |

| 51d [12d]                | 11.3              |

| 52d                      | 10.4              |

| 53d                      | 9.50              |

| 54d                      | 8.52              |

| 55d [13d]                | 7.59              |

| 56d                      | 6.60              |

| 57d                      | 5.70              |

| 58d                      | 4.74              |

| 59d [14d]                | 3.80              |

| 60d                      | 2.87              |

| 61d                      | 1.93              |

| 62d                      | 1.00              |

| 63d [15d]                | 0.06              |

7-Feb-2013

### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|-------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      |             | (2)                        |                  | (3)                |              | (4)               |         |

| LM10011SD/NOPB   | ACTIVE | SON          | DSC     | 10   | 1000        | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   |                   | Samples |

| LM10011SDX/NOPB  | ACTIVE | SON          | DSC     | 10   | 4500        | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   |                   | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

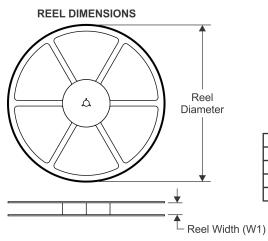

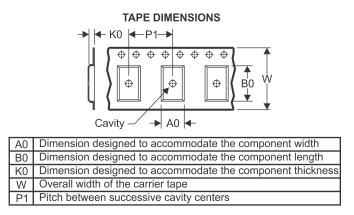

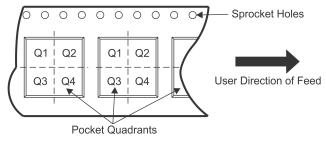

#### TAPE AND REEL INFORMATION

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimens | ions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-------------|------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

|             | Device           | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LM100       | 11SD/NOPB        | SON             | DSC                | 10 | 1000 | 178.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LM100       | 11SDX/NOPB       | SON             | DSC                | 10 | 4500 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

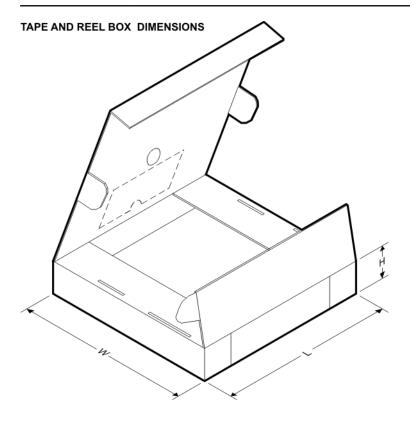

# PACKAGE MATERIALS INFORMATION

8-Feb-2013

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM10011SD/NOPB  | SON          | DSC             | 10   | 1000 | 203.0       | 190.0      | 41.0        |

| LM10011SDX/NOPB | SON          | DSC             | 10   | 4500 | 358.0       | 343.0      | 63.0        |

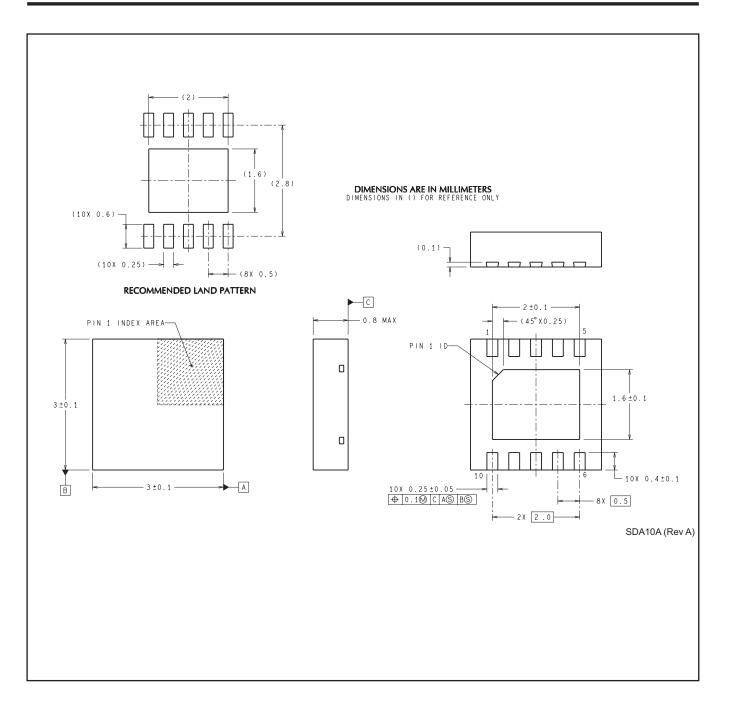

# **MECHANICAL DATA**

# DSC0010A

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |  |  |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|--|--|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |  |  |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |  |  |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |  |  |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |  |  |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |  |  |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |  |  |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |  |  |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |  |  |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |  |  |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |  |  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |  |  |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |  |  |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |  |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated