National Semiconductor

# LM2926/LM2927 Low Dropout Regulator with Delayed Reset

### **General Description**

The LM2926 is a 5V, 500 mA, low dropout regulator with delayed reset. The microprocessor reset flag is set low by thermal shutdown, short circuits, overvoltage conditions, dropout, and power-up. After the fault condition is corrected, the reset flag remains low for a delay time determined by the delay capacitor. Hysteresis is included in the reset circuit to prevent oscillations, and a reset output is guaranteed down to 3.2V supply input. A latching comparator is used to discharge the delay capacitor, which guarantees a full reset pulse even when triggered by a relatively short fault condition. A patented quiescent current reduction circuit drops the ground pin current to 8 mA at full load when the input-output differential is 3V or more.

Familiar PNP regulator features such as reverse battery protection, transient protection, and overvoltage shutdown are included in the LM2926 making it suitable for use in automotive and battery operated equipment.

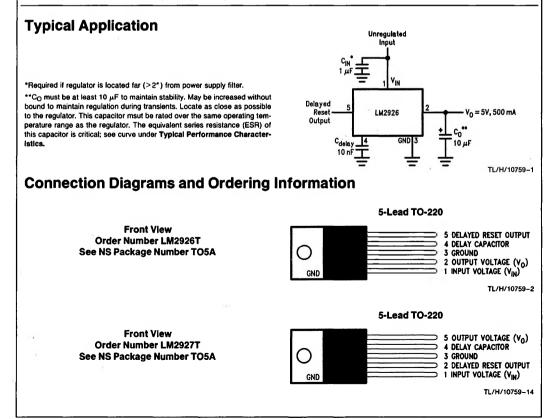

The LM2927 is electrically identical to the LM2926 but has a different pin-out. The LM2927 is pin-for-pin compatible with

the L4947 and TLE4260 alternatives. The LM2926 is pinfor-pin compatible with the LM2925.

### Features

- 5% output accuracy over entire operating range

- Dropout voltage typically 350 mV at 500 mA output

- Externally programmed reset delay

- Short circuit proof

- Reverse battery proof

- Thermally protected

- LM2926 is pin-for-pin compatible with the LM2925

- P+ Product Enhancement tested

### Applications

- Battery operated equipment

- Microprocessor-based systems

- Portable instruments

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications. е

| Input | Vo | Itage |

|-------|----|-------|

| •     |    |       |

| Survival                  |              |

|---------------------------|--------------|

| t = 100 ms                | 80V          |

| t = 1 ms                  | -50V         |

| Continuous                | -18V to +26V |

| Reset Output Sink Current | 10 mA        |

| ESD Susceptibility (Note 2)               | 2 kV               |

|-------------------------------------------|--------------------|

| Power Dissipation (Note 3)                | internally Limited |

| Junction Temperature (T <sub>JMAX</sub> ) | 150°C              |

| Storage Temperature Range                 | -40°C to +150°C    |

| Lead Temperature (Soldering, 10 sec.)     | 260°C              |

# **Operating Ratings** (Note 1)

| Junction Temperature Range (T <sub>J</sub> ) | -40°C to +125°C |

|----------------------------------------------|-----------------|

| Maximum Input Voltage                        | 26V             |

# **Electrical Characteristics** $V_{IN} = 14.4V$ , $C_O = 10 \ \mu$ F, $-40^{\circ}C \le T_J \le 125^{\circ}C$ , unless otherwise specified.

| Parameter                                | Conditions                                                                                                             | Typ<br>(Note 4) | Limit<br>(Note 5) | Units<br>(Limit) |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|

| REGULATOR OUTPUT                         |                                                                                                                        |                 |                   |                  |

| Output Voltage                           | $5 \text{ mA} \le I_{O} \le 500 \text{ mA},$<br>T <sub>J</sub> = 25°C                                                  | 5               | 4.85              | V (min)<br>V     |

|                                          |                                                                                                                        |                 | 5.15              | V (max)          |

| a 11 -                                   | ,5 mA ≤ I <sub>O</sub> ≤ 500 mA                                                                                        | 5               | 4.75              | V (min)<br>V     |

|                                          |                                                                                                                        |                 | 5.25              | V (max)          |

| Line Regulation                          | $I_{O} = 5 \text{ mA}, 9V \le V_{IN} \le 16V$                                                                          | 1               | 25                | mV<br>mV (max)   |

|                                          | $I_{O} = 5 \text{ mA}, 7V \le V_{IN} \le 26V$                                                                          | 3               | 50                | mV<br>mV (max)   |

| Load Regulation                          | $5 \text{ mA} \leq I_{O} \leq 500 \text{ mA}$                                                                          | 5               | 60                | mV<br>mV (max)   |

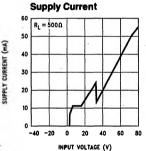

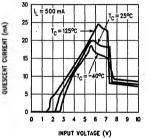

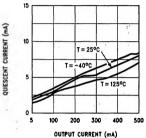

| Quiescent Current                        | l <sub>O</sub> = 5 mA                                                                                                  | 2               | 3                 | mA<br>mA (max)   |

|                                          | i <sub>O</sub> = 500 mA                                                                                                | 8               | 30                | mA<br>mA (max)   |

| Quiescent Current at Low V <sub>IN</sub> | $I_{O} = 5 \text{ mA}, V_{IN} = 5V$                                                                                    | 3               | . 10              | mA<br>mA (max)   |

|                                          | $I_{O} = 500 \text{ mA}, V_{IN} = 6V$                                                                                  | 25              | 60                | mA<br>mA (max)   |

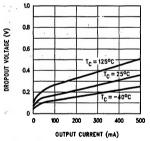

| Dropout Voltage (Note 6)                 | $I_{O} = 5 \text{ mA}, T_{J} = 25^{\circ}\text{C}$                                                                     | 60              | 200               | mV<br>mV (max)   |

|                                          | $I_0 = 5 \text{ mA}$                                                                                                   |                 | 300               | mV (max)         |

|                                          | l <sub>O</sub> = 500 mA, T <sub>J</sub> = 25°C                                                                         | 350             | 600               | mV<br>mV (max)   |

|                                          | $I_0 = 500  \text{mA}$                                                                                                 |                 | 700               | mV (max)         |

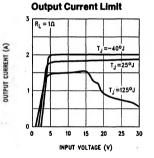

| Short Circuit Current                    | $V_{\rm IN} = 8V, R_{\rm L} = 1\Omega$                                                                                 | 2               | 800               | mA (min)<br>A    |

| <u>6.</u>                                |                                                                                                                        |                 | 3                 | A (max)          |

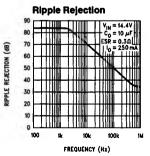

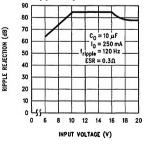

| Ripple Rejection                         | $f_{\text{RIPPLE}} = 120 \text{ Hz}, \text{ V}_{\text{RIPPLE}} = 1 \text{ Vrms}, \text{ I}_{\text{O}} = 50 \text{ mA}$ |                 | 60                | dB (min)         |

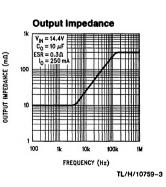

| Output Impedance                         | $I_{O} = 50 \text{ mAdc and } 10 \text{ mArms } @ 1 \text{ kHz}$                                                       | 100             |                   | mΩ               |

| Output Noise                             | 10 Hz to 100 kHz, I <sub>O</sub> = 50 mA                                                                               | 1               |                   | mVrms            |

| Long Term Stability                      | 10 C                                                                                                                   | 20              |                   | mV/1000 H        |

| Maximum Operational Input Voltage        | Continuous                                                                                                             |                 | 26                | V (min)          |

| Parameter                                           | Conditions                                                                                     | Typ<br>(Note 4) | Limit<br>(Note 5) | Units<br>(Limit) |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|

| EGULATOR OUTPUT (Continued)                         |                                                                                                |                 |                   |                  |

| Peak Transient Input Voltage                        | $V_0 \le 7V$ , $R_L = 100\Omega$ , $t_f = 100$ ms                                              |                 | 80                | V (min)          |

| Reverse DC Input Voltage                            | $V_{O} \ge -0.6V, R_{L} = 100\Omega$                                                           |                 | -18               | V (min)          |

| Reverse Transient Input Voltage                     | $t_r = 1 \text{ ms}, R_L = 100\Omega$                                                          |                 | -50               | V (min)          |

| ESET OUTPUT                                         |                                                                                                |                 |                   |                  |

| Threshold                                           | $\Delta V_O$ Required for Reset Condition (Note 7)                                             | -250            | -80               | mV (min)<br>mV   |

|                                                     |                                                                                                |                 | -400              | mV (max)         |

| Output Low Voltage                                  | $I_{SINK} = 1.6 \text{ mA}, V_{IN} = 3.2 \text{V}$                                             | 0.15            | 0.4               | V (max)          |

| Internal Pull-Up Resistance                         |                                                                                                | 30              |                   | kΩ               |

| Delay Time                                          | C <sub>DELAY</sub> = 10 nF (See Timing Curve)                                                  | 19              |                   | ms               |

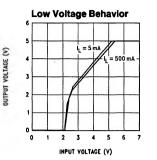

| Minimum Operational V <sub>IN</sub><br>on Power Up  | Delayed Reset Output $\leq$ 0.8V,<br>I <sub>SINK</sub> = 1.6 mA, R <sub>L</sub> = 100 $\Omega$ | 2.2             | 3.2               | V<br>V (min)     |

| Minimum Operational V <sub>O</sub><br>on Power Down | Delay Reset Output ≤ 0.8V,<br>I <sub>SINK</sub> = 10 μA, V <sub>IN</sub> = 0V                  | 0.7             |                   | v                |

| ELAY CAPACITOR PIN                                  |                                                                                                |                 |                   |                  |

| Threshold Difference ( $\Delta V_{DELAY}$ )         | Change in Delay Capacitor Voltage Required for<br>Reset Output to Return High                  | 3.75            | 3.5               | V (min)<br>V     |

|                                                     |                                                                                                |                 | 4.1               | V (max)          |

| Charging Current (I <sub>DELAY</sub> )              |                                                                                                | 2.0             | 1.0               | μΑ (min)<br>μΑ   |

|                                                     |                                                                                                |                 | 3.0               | μA (max)         |

LM2926/LM2927

Note 1: Absolute MaxImum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: Human body model; 100 pF discharged through a 1.5  $k\Omega$  resistor.

Note 3: The maximum power dissipation is a function of  $T_{JMAX}$ , and  $\theta_{JA}$ , and  $T_A$ , and is limited by thermal shutdown. The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{JMAX}-T_A)/\theta_{JA}$ . If this dissipation is exceeded, the die temperature will rise above 150°C and the device will go into thermal shutdown. For the LM2926 and LM2927, the junction-to-ambient thermal resistance is 53°C/W, and the junction-to-case thermal resistance is 3°C/W.

Note 4: Typicals are at  $T_J = 25^{\circ}C$  and represent the most likely parametric norm.

Note 5: Limits are 100% guaranteed by production testing.

Note 6: Dropout voltage is the input-output differential at which the circuit ceases to regulate against any further reduction in input voltage. Dropout voltage is measured when the output voltage (V<sub>O</sub>) has dropped 100 mV from the nominal value measured at V<sub>IN</sub> = 14.4V.

Note 7: The reset flag is set LOW when the output voltage has dropped an amount,  $\Delta V_O$ , from the nominal value measured at  $V_{IN}$  = 14.4V.

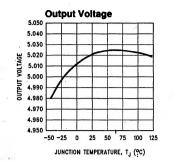

## **Typical Performance Characteristics**

ε

VOLTAGE (

OUTPUT

QUIESCENT CURRENT

E

SERIES RESISTANCE

EQUIVALENT

**Output Capacitor ESR** 100 10 FRE 1.0 0. 0.01 0 100 200 300 400 500

OUTPUT CURRENT (mA)

LM2926/LM2927

## **Applications Information**

#### EXTERNAL CAPACITORS

The LM2926/7 output capacitor is required for stability. Without it, the regulator output will oscillate at amplitudes as high as several volts peak-to-peak at frequencies up to 500 kHz. Although 10  $\mu$ F is the minimum recommended value, the actual size and type may vary depending upon the application load and temperature range. Capacitor equivalent series resistance (ESR) also affects stability. The region of stable operation is shown in the **Typical Performance Characteristics** (Output Capacitor ESR curve).

Output capacitors can be increased in size to any desired value above 10  $\mu$ F. One possible purpose of this would be to maintain the output voltage during brief conditions of input transients that might be characteristic of a particular system.

Capacitors must also be rated at all ambient temperatures expected in the system. Many aluminum electrolytics freeze at temperatures below  $-30^{\circ}$ C, reducing their effective capacitance to zero. To maintain regulator stability down to  $-40^{\circ}$ C, capacitors rated at that temperature (such as tantalums) must be used.

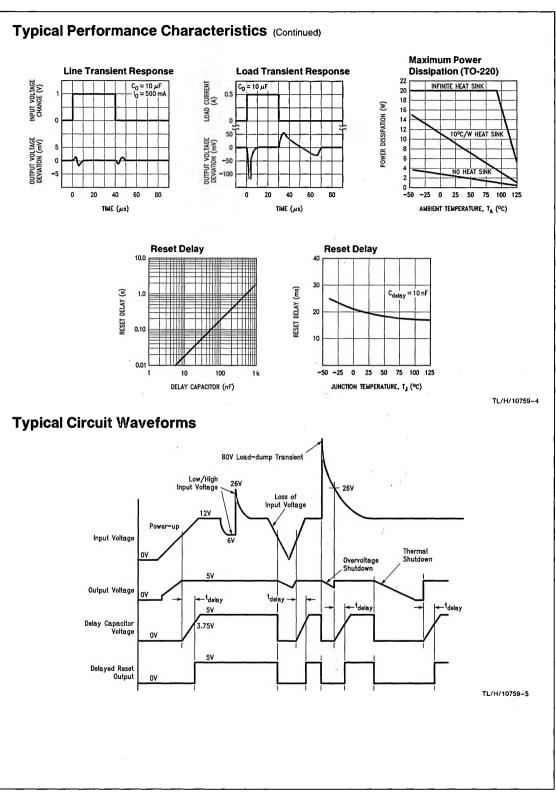

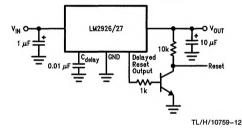

#### DELAYED RESET

The delayed reset output is designed to hold a microprocessor in a reset state on system power-up for a programmable time interval to allow the system clock and other powered circuitry to stabilize. A full reset interval is also generated whenever the output voltage falls out of regulation. The circuit is tripped whenever the output voltage of the regulator is out of regulation by the Reset Threshold value. This can be caused by low input voltages, over current conditions, over-voltage shutdown, thermal shutdown, and by both power-up and power-down sequences. When the reset circuit detects one of these conditions, the delay capacitor is discharged by an SCR and held in a discharged state by a saturated NPN switch. As long as the delay capacitor is held low, the reset output is also held low. Because of the action of the SCR, the reset output cannot glitch on noise or transient fault conditions. A full reset pulse is obtained for any fault condition that trips the reset circuit.

When the output regains regulation, the SCR is switched off and a small current ( $I_{DELAY} = 2 \mu A$ ) begins charging the delay capacitor. When the capacitor voltage increases  $3.75V (\Delta V_{DELAY})$  from its discharged value, the reset output is again set HIGH. The delay time is calculated by:

delay time =

$$\frac{C_{DELAY} \Delta V_{DELAY}}{I_{DELAY}}$$

(1)

or

de

play time

$$\approx 1.9 \times 10^6 \,\mathrm{C}_{\mathrm{DELAY}}$$

(2)

The constant, 1.9  $\times$  10<sup>6</sup>, has a ±20% tolerance from device to device. The total delay time error budget is the sum of the 20% device tolerance and the tolerance of the external capacitor. For a 20% timing capacitor tolerance, the worst case total timing variation would amount to ±40%, or a ratio of 2.33:1. In most applications the minimum expected reset pulse is of interest. This occurs with minimum C<sub>DELAY</sub>, minimum  $\Delta V_{DELAY}$ , and maximum I<sub>DELAY</sub>.  $\Delta V_{DELAY}$  and I<sub>DELAY</sub> are fully specified in the Electrical Characteristics. Graphs showing the relationship between delay time and both temperature and C<sub>DELAY</sub> are shown in the **Typical Performance Characteristics**.

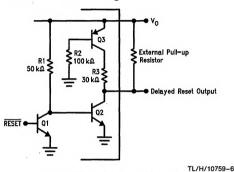

As shown in *Figure 1*, the delayed reset output is pulled low by an NPN transistor (Q2), and pulled high to V<sub>O</sub> by an internal 30 k $\Omega$  resistor (R3) and PNP transistor (Q3). The reset output will operate when V<sub>O</sub> is sufficient to bias Q2 (0.7V or more). At lower voltages the reset output will be in a high impedance condition. Because of differences in the V<sub>BE</sub> of Q2 and Q3 and the values of R1 and R2, Q2 is guaranteed by design to bias *before* Q3, providing a smooth transition from the high impedance state when V<sub>O</sub> < 0.7V, to the active low state when V<sub>O</sub> > 0.7V.

FIGURE 1. Delay Reset Output

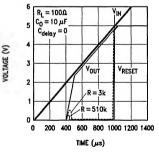

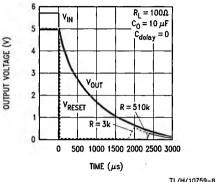

The static reset characteristics are shown in *Figure 2*. This shows the relationship between the input voltage, the regultor output and reset output. Plots are shown for various external pull-up resistors ranging in value from 3 k $\Omega$  to an open circuit. Any external pull-up resistance causes the reset output to follow the regulator output until Q2 is biased ON. C<sub>DELAY</sub> has no effect on this characteristic.

TL/H/10759-7

#### FIGURE 2. Reset Output Behavior during Power-Up

*Figure 2* is useful for determing reset performance at any particular input voltage. Dynamic performance at power-up will closely follow the characteristics illustrated in *Figure 2*, except for the delay added by  $C_{DELAY}$  when  $V_O$  reaches 5V. The dynamic reset characteristics at power-down are illustrated by the curve shown in *Figure 3*. At time t= 0 the input voltage is instantaneously brought to 0V, leaving the output powered by  $C_O$ . As the voltage on  $C_O$  decays (discharged by a 100 $\Omega$  load resistor), the reset output is held low. As  $V_O$  drops below 0.7V, the reset rises up slightly should there be any external pull-up resistance. With no external resistance, the reset line stays low throughout the entire power down cycle. If the input voltage does not fall instantaneously, the reset signal will tend to follow the performance characteristics shown in *Figure 2*.

### Applications Information (Continued)

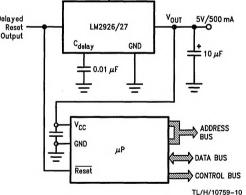

### SYSTEM DESIGN CONSIDERATIONS

Many microprocessors are specified for operation at 5V  $\pm$  10%, although they often continue operating well outside this range. Others, such as certain members of the COPS family of microcontrollers, are specified for operation as low as 2.4V.

FIGURE 3. Reset Output Behavior during Power-Down

Of particular concern is low voltage operation, which occurs in battery operated systems when the battery reaches the end of its discharge cycle. Under this condition, when the supply voltage is outside the guaranteed operating range, the clock may continue to run and the microprocessor will attempt to execute instructions. If the supply voltage is outside the guaranteed operating range, the instructions may not execute properly and a hardware reset such as is supplied by the LM 2926/7 may fail to bring the processor under control. The LM2926/7 reset output may be more efficiently employed in certain applications as a means of defeating memory WRITE lines, clocks, or external loads, rather than depending on unspecified microprocessor operating conditions.

In critical applications the microprocessor reset input should be fully characterized and guaranteed to operate until the clock ceases oscillating.

#### INPUT TRANSIENTS

The LM2926/7 are guaranteed to withstand positive input transients to 80V followed by an exponential decay of  $\tau = 20$  ms ( $t_f = 100$  ms, or 5 time constants) while maintaining an output of less than 7V. The regulator remains operational to 26 V<sub>DC</sub>, and shuts down if this value is exceeded.

# Applications Information (Continued)

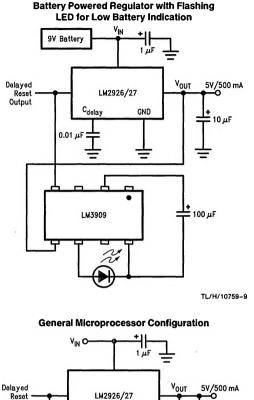

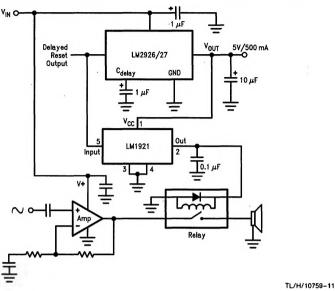

#### Using the Reset to De-Activate Power Loads. The LM1921 is a Fully Protected 1 Amp High-Side Driver.

#### **Generating an Active High Reset Signal**

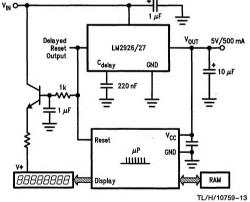

Using the Reset to Ensure an Accurate Display on Power-Up or Power-Down