SNOSAE9C - AUGUST 2004-REVISED OCTOBER 2011

# LMV422 Dual Rail-to-Rail Output Operational Amplifier with Power Select

Check for Samples: LMV422

#### **FEATURES**

- Supply voltage 2.7V to 5.5V

- Supply current per channel

- Low power mode 2 μA

- Full power mode 400 μA

- Input common mode voltage range −0.3V to 3.8V

- CMRR 85 dB

- · Output voltage swing Rail-to-Rail

- Input offset voltage 1 mV

- Bandwidth

- Low power mode 27 kHz

- Full power mode 8 MHz

- Stable for A<sub>V</sub> ≥ +2 or A<sub>V</sub> ≤ -1

#### **APPLICATIONS**

- AC coupled circuits

- Portable instrumentation

- Smoke detectors

#### DESCRIPTION

The LMV422 dual rail-to-rail output amplifier offers a power select pin (PS) that allows the user to select one of two power modes depending on the level of performance desired. This is ideal for AC coupled circuits where the circuit needs to be kept active to maintain a quiescent charge on the coupling capacitors with minimum power consumption.

For portable applications, the LMV422 operates in low power mode consuming only 2  $\mu$ A of supply current per channel at a bandwidth of 27 kHz. This allows the user to reduce the power consumption of an amplifier while maintaining an active circuit. For additional bandwidth and output current drive the amplifier can be switched to full power mode with 8 MHz bandwidth while consuming only 400  $\mu$ A per channel.

The LMV422 features a rail-to-rail output voltage swing in addition to an input common mode range that includes ground. The LMV422 is designed for closed loop gains of plus two (or minus one) or greater. The LMV422 is offered in a 10-Pin MSOP miniature package to ease the adoption in applications where board area is at a premium.

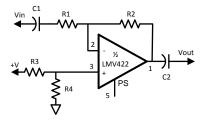

#### **Typical Application**

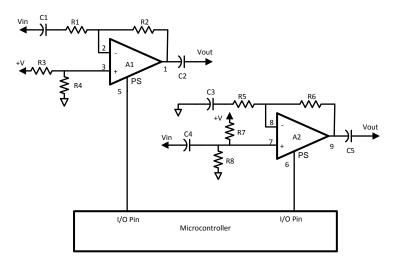

Figure 1. AC Coupled Application

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

SNOSAE9C - AUGUST 2004-REVISED OCTOBER 2011

www.ti.com

# Absolute Maximum Ratings

| ESD Tolerance <sup>(2)</sup>                      |                 |

|---------------------------------------------------|-----------------|

| Human Body                                        | 2000V           |

| Machine Model                                     | 200V            |

| V <sub>IN</sub> Differential                      | ±2V             |

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) | 2.5V to 5.5V    |

| Storage Temperature Range                         | −65°C to +150°C |

| Junction Temperature (3)                          | +150°C          |

| Soldering Information                             |                 |

| Infrared or Convection (20 sec)                   | 235°C           |

| Wave Soldering Lead Temp. (10 sec)                | 260°C           |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

- (2) Human Body Model, 1.5 kΩ in series with 100 pF, Machine Model, 0Ω in series with 200 pF.

- (3) The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub>, and T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>D</sub> = (T<sub>J(MAX)</sub> T<sub>A</sub>)/ θ<sub>JA</sub>. All numbers apply for packages soldered directly onto a PC board.

### Operating Ratings (1)

| Supply Voltage (V <sup>+</sup> – V <sup>-</sup> ) | 2.7V to 5.5V   |

|---------------------------------------------------|----------------|

| Temperature Range <sup>(2)</sup>                  | -40°C to +85°C |

| Package Thermal Resistance (θ <sub>JA</sub> )     |                |

| 10-Pin MSOP                                       | 210°C/W        |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

(2) Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

## **5V Full Power Mode Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ ,  $PS = V^-$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                                   | Conditions                                                                | Min<br>(1)          | Typ   | <b>Max</b> (1)    | Units  |

|--------------------|---------------------------------------------|---------------------------------------------------------------------------|---------------------|-------|-------------------|--------|

| V <sub>OS</sub>    | Input Offset Voltage                        |                                                                           |                     | 1     | 4<br>5.5          | mV     |

| ΔV <sub>OS</sub>   | Input Offset Voltage Difference             | V <sub>OS</sub> in Full Power Mode –<br>V <sub>OS</sub> in Low Power Mode |                     | 0.1   | 1                 | mV     |

| TC V <sub>OS</sub> | Input Offset Average Drift                  | (3)                                                                       |                     | 2     |                   | μV/C   |

| В                  | Input Bias Current                          |                                                                           |                     | 5     |                   | pA     |

| CMRR               | Common Mode Rejection Ratio                 | V <sub>CM</sub> Stepped from 0V to 3.5V                                   | 68<br><b>60</b>     | 85    |                   | dB     |

| PSRR               | Power Supply Rejection Ratio                | V <sup>+</sup> = 2.7V to 5V                                               | 66<br><b>60</b>     | 90    |                   | dB     |

| CMVR               | Input Common Mode Voltage<br>Range          | CMRR ≥ 50 dB                                                              | -0.3                |       | 3.8               | V      |

| A <sub>VOL</sub>   | Large Signal Voltage Gain                   | $V_O = 0.75V$ to 4.25V<br>$R_L = 1 M\Omega$                               | 72<br><b>70</b>     | 100   |                   | dB     |

|                    |                                             | $V_{O} = 0.75V \text{ to } 4.25V$<br>$R_{L} = 10 \text{ k}\Omega$         | 75<br><b>70</b>     | 102   |                   |        |

| Vo                 | Output Swing High                           | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                               | 4.93<br><b>4.88</b> | 4.97  |                   | V      |

|                    |                                             | $R_L = 1 \text{ M}\Omega \text{ to V}^+/2$                                | 4.94<br><b>4.89</b> | 4.98  |                   |        |

|                    | Output Swing Low                            | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                               |                     | 33    | 180<br><b>230</b> | mV     |

|                    |                                             | $R_L = 1 M\Omega$ to $V^+/2$                                              |                     | 25    | 120<br><b>170</b> |        |

| I <sub>SC</sub>    | Output Short Circuit Current                | Sourcing, V <sub>O</sub> = 0V<br>V <sub>ID</sub> = 100 mV                 | 3                   | 5     |                   | mA     |

|                    |                                             | Sinking, $V_0 = 5V$<br>$V_{ID} = -100 \text{ mV}$                         | 9                   | 16    |                   |        |

| I <sub>S</sub>     | Supply Current Per Channel                  | PS ≤ 0.5V                                                                 |                     | 400   | 650<br><b>900</b> | μА     |

| SR                 | Slew Rate (4)                               | $V_{O} = 3V, A_{V} = +2$                                                  | 1.8                 | 3.8   |                   | V/µs   |

| GBW                | Gain Bandwidth Product                      |                                                                           |                     | 8     |                   | MHz    |

| e <sub>n</sub>     | Input-Referred Voltage Noise                | f = 100 kHz                                                               |                     | 20    |                   | nV/√Hz |

|                    |                                             | f = 1 kHz                                                                 |                     | 25    |                   |        |

| n                  | Input-Referred Current Noise                | f = 1 kHz                                                                 |                     | 0.006 |                   | pA/√Hz |

| t <sub>LF</sub>    | Time from Low Power Mode to Full Power Mode |                                                                           |                     | 210   |                   | ns     |

| TH <sub>PS</sub>   | Full Power Mode Voltage<br>Threshold        |                                                                           |                     |       | 0.5               | V      |

| I <sub>PS</sub>    | Input Current PS pin (5)                    |                                                                           |                     | -2    |                   | μA     |

All limits are guaranteed by testing or statistical analysis.

Copyright © 2004–2011, Texas Instruments Incorporated

Typical values represent the most likely parametric norm.

Offset voltage average drift is determined by dividing the change in V<sub>OS</sub> at temperature extremes into the total temperature change. Slew rate is the average of the rising and falling slew rates.

Positive current corresponds to current flowing into the device.

## **5V Low Power Mode Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ ,  $PS = V^+$  or Open. **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                                   | Conditions                                                                | <b>Min</b><br>(1)   | Typ  | Max<br>(1)        | Units  |

|--------------------|---------------------------------------------|---------------------------------------------------------------------------|---------------------|------|-------------------|--------|

| V <sub>OS</sub>    | Input Offset Voltage                        |                                                                           |                     | 1    | 4<br><b>5.5</b>   | mV     |

| ΔV <sub>OS</sub>   | Input Offset Voltage Difference             | V <sub>OS</sub> in Full Power Mode –<br>V <sub>OS</sub> in Low Power Mode |                     | 0.1  | 1                 | mV     |

| TC V <sub>OS</sub> | Input Offset Average Drift                  | (3)                                                                       |                     | 2    |                   | μV/C   |

| В                  | Input Bias Current                          |                                                                           |                     | 5    |                   | рА     |

| CMRR               | Common Mode Rejection Ratio                 | V <sub>CM</sub> Stepped from 0V to 3.5V                                   | 60<br><b>55</b>     | 82   |                   | dB     |

| PSRR               | Power Supply Rejection Ratio                | V <sup>+</sup> = 2.7V to 5V                                               | 62<br><b>60</b>     | 90   |                   | dB     |

| CMVR               | Input Common-Mode Voltage<br>Range          | CMRR ≥ 50 dB                                                              | 0                   |      | 3.5               | V      |

| A <sub>VOL</sub>   | Large Signal Voltage Gain                   | $R_L = 1 M\Omega$<br>$V_O = 0.75 \text{ to } 4V$                          | 62<br><b>54</b>     | 72   |                   | dB     |

| Vo                 | Output Swing High                           | $R_L = 1 M\Omega$                                                         | 4.94<br><b>4.89</b> | 4.98 |                   | ٧      |

|                    | Output Swing Low                            | $R_L = 1 M\Omega$                                                         |                     | 150  | 200<br><b>250</b> | mV     |

| I <sub>SC</sub>    | Output Short Circuit Current                | Sourcing, $V_O = 0V$<br>$V_{ID} = 200 \text{ mV}$                         | 40                  | 140  |                   | μА     |

|                    |                                             | Sinking, $V_0 = 5V$<br>$V_{ID} = -200 \text{ mV}$                         | 25                  | 130  |                   |        |

| s                  | Supply Current per channel                  | PS ≥ 4. 5V                                                                |                     | 2    | 3.5<br><b>4.5</b> | μA     |

| SR                 | Slew Rate <sup>(4)</sup>                    | V <sub>O</sub> = 3V, A <sub>V</sub> = +2                                  | 8                   | 14   |                   | V/ms   |

| GBW                | Gain Bandwidth Product                      |                                                                           |                     | 27   |                   | kHz    |

| e <sub>n</sub>     | Input-Referred Voltage Noise                | f = 100 kHz                                                               |                     | 40   |                   | nV/√Hz |

|                    |                                             | f = 1 kHz                                                                 |                     | 60   |                   |        |

| n                  | Input-Referred Current Noise                | f = 1 kHz                                                                 |                     | 0.06 |                   | pA/√Hz |

| <sup>L</sup> FL    | Time from Full Power Mode to Low Power Mode |                                                                           |                     | 500  |                   | ns     |

| TH <sub>PS</sub>   | Low Power Mode Voltage<br>Threshold         |                                                                           | 4.5                 |      |                   | V      |

| PS                 | Input Current PS pin (5)                    |                                                                           |                     | 8    |                   | nA     |

- (1) All limits are guaranteed by testing or statistical analysis.

- (2) Typical values represent the most likely parametric norm.

- (3) Offset voltage average drift is determined by dividing the change in V<sub>OS</sub> at temperature extremes into the total temperature change.

- (4) Slew rate is the average of the rising and falling slew rates.

- (5) Positive current corresponds to current flowing into the device.

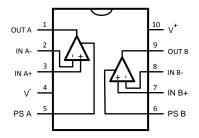

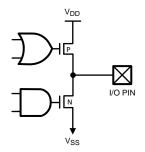

#### **Connection Diagram**

Figure 2. 10-Pin MSOP (Top View)

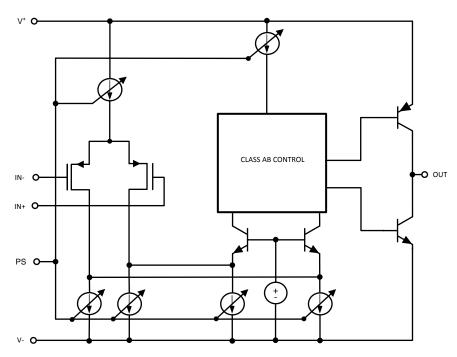

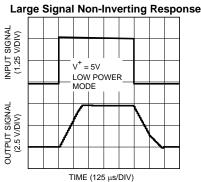

# **Simplified Schematic**

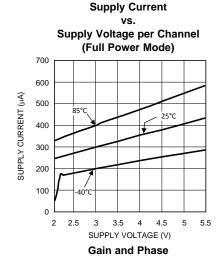

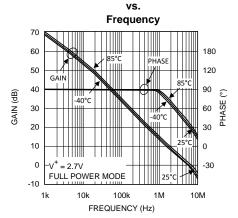

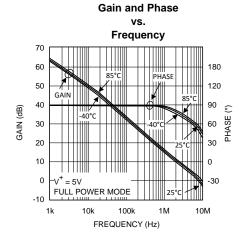

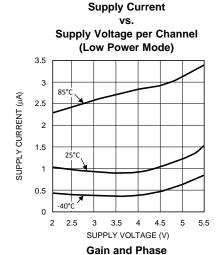

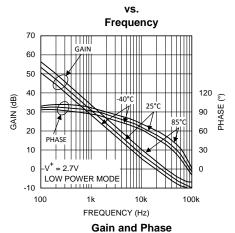

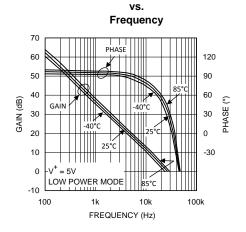

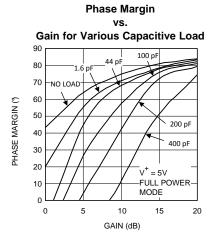

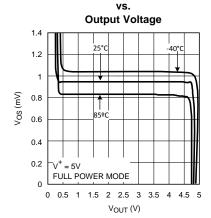

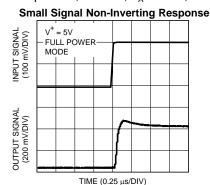

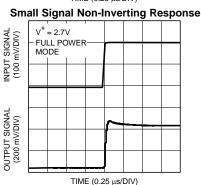

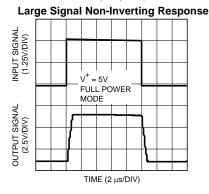

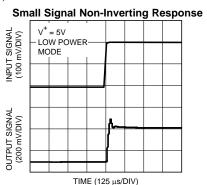

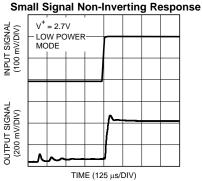

### **Typical Performance Characteristics**

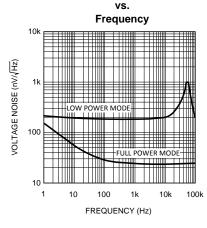

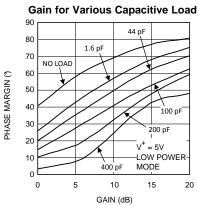

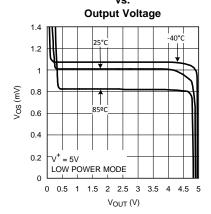

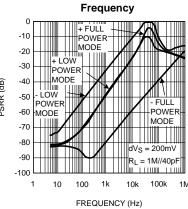

Unless otherwise specified,  $V^+ = 5V$ ,  $T_A = 25$ °C,  $PS = V^+$  for Full Power Mode,  $PS = V^-$  for Low Power Mode.

#### **Typical Performance Characteristics (continued)**

Unless otherwise specified,  $V^+ = 5V$ ,  $T_A = 25$ °C,  $PS = V^+$  for Full Power Mode,  $PS = V^-$  for Low Power Mode.

# Noise

# Phase Margin vs.

# Input Offset Voltage vs.

#### PSRR vs.

## **Typical Performance Characteristics (continued)**

Unless otherwise specified,  $V^+ = 5V$ ,  $T_A = 25$ °C,  $PS = V^+$  for Full Power Mode,  $PS = V^-$  for Low Power Mode.

## **Application Information**

The LMV422 is a dual rail-to-rail output amplifier that can be switched between two active power modes. The power select pin (PS) provides a method to optimize the power consumption, bandwidth and short circuit current. When the PS pin is set to greater than 4.5V (Figure 3) or left open, the LMV422 is in Low Power Mode operating at a bandwidth of 27 kHz and is consuming only 2  $\mu$ A of supply current per channel. Setting the PS pin to less than 0.5V, switches the LMV422 to Full Power Mode with a bandwidth of 8 MHz and supply current of 400  $\mu$ A per channel (Figure 4). The PS pin should not exceed the supply voltage. The active power modes of the two amplifiers can be set independently.

PS PS

Figure 3. Low Power Mode

Figure 4. Full Power Mode

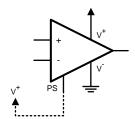

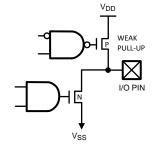

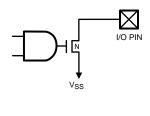

The LMV422 PS pin has an internal pull up and a logic level control gate that makes it easy for the PS pin to be controlled by the output of a logic gate or the output pin of a microcontroller. The following figures show the three typical output configurations for logic gates and microcontrollers.

Figure 5. (a) Typical Output Configurations for Logic Gates and Microcontrollers

Figure 6. (b) Typical Output Configurations for Logic Gates and Microcontrollers

Figure 7. (c) Typical Output Configurations for Logic Gates and Microcontrollers

#### **CAPACITIVE LOAD TOLERANCE**

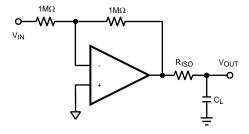

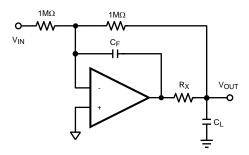

The LMV422 is optimized for maximum bandwidth when operating at a minimum closed loop gain of +2 or -1; therefore, it is not recommended that it be configured as a buffer. Like many other op amps, the LMV422 may oscillate when the applied load appears capacitive. The threshold of the oscillation varies both with load and circuit gain. (See Phase Margin vs. Gain for Various Capacitive Loads.) The load capacitance interacts with the amplifier's output resistance to create an additional pole. If this pole frequency is too low, it will degrade the amplifier's phase margin so that the amplifier is no longer stable.

Figure 8 and Figure 9 show the addition of a small value resistor  $R_{ISO}$  or  $R_X$  (50 $\Omega$  to 100 $\Omega$ ) in series with the op amp's output. Figure 9 shows the addition of a capacitor  $C_F$  (5 pF to 10 pF) between the inverting input and the output pin. This additional capacitor returns the phase margin to a safe value without interfering with lower frequency circuit operation. Note that in all cases, the output will ring heavily when the load capacitance is near the threshold for oscillation.

Figure 8. Capacitive Load Tolerance

Figure 9. Capacitive Load Tolerance

#### **AC COUPLED CIRCUITS**

The two power modes makes the LMV422 ideal for AC coupled circuits where the circuit needs to be kept active to maintain a quiescent charge on the coupling capacitors with minimum power consumption.

Figure 10 shows a schematic of an inverting and non-inverting AC coupled amplifiers using the LMV422 with the PS pins controlled by I/O ports of a microcontroller.

The advantage of the low power active mode for AC coupled amplifiers is the elimination of the time needed to re-establish a quiescent operating point when the amplifier is switched to a full power mode. When amplifiers without a low power active mode are used in low power applications, there are two ways to minimize power consumption. The first is turning off the amplifiers by switching off power to the op amps using a transistor switch. The second is using an amplifier with a shut down pin. Both of these methods have the problem of allowing the coupling capacitors, C1, C2, C3, C4, and C5, to discharge the quiescent DC voltage stored on them when the amplifiers are placed in the shut down state. When the amplifiers are turned on again, the quiescent DC voltages must reestablish themselves. During this time, the amplifier's output is not usable because the output signal is a mixture of the amplified input signal and the charging voltage on the coupling capacitors. The settling time can range from several milliseconds to several seconds depending on the resistor and capacitor values.

When the LMV422 is placed into the low power mode the power consumption is minimal but the amplifier is active to maintain the quiescent DC voltage on the coupling capacitors. The transition back to the operational high power mode is fast, within a few hundred nanoseconds. The active low power mode of the LMV422 satisfies the two critical aspects of a low power AC amplifier design. The values of the gain resistors, bias resistors, and coupling capacitors can be chosen independently of the turn on and stabilization time.

Figure 10. Inverting and Non-Inverting AC Coupled Amplifiers Using the LMV422

SNOSAE9C - AUGUST 2004 - REVISED OCTOBER 2011

#### **RESISTIVE LOAD**

The LMV422 has a minimum current drive of 3 mA in full power mode. The minimum resistive load should be 10  $\mbox{k}\Omega$

The current drive in the low power mode is 140 uA, the minimum resistive load should be 100 k $\Omega$ .

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>