#### 2 x 8 CROSSPOINT MATRIX

- VERY LOW ON RESISTANCE

- HIGH CROSS-TALK AND OFF-STATE ISOLATION

- SERIAL SWITCH ADDRESSING, μ-PROCESSOR COMPATIBLE

The M089 and M099 are 2x8 crosspoint matrices consisting of 16 N-channel MOS transistors. Both devices are similar in operation, the only difference being that in the M099 the "all switches reset" function is implemented by a microprocessor command.

Both devices have been specially designed to provide switches with low cross-talk, high off-state isolation (both better than -90 dB) and low on-resistance.

#### **ABSOLUTE MAXIMUM RATINGS\***

| -0.5 to | 17                        | V                       |

|---------|---------------------------|-------------------------|

| -0.5 to | 17                        | V                       |

|         | 10                        | V                       |

|         | 640                       | mW                      |

| 0 to    | 70                        | °C                      |

| -40 to  | 70                        | °C                      |

| -65 to  | 150                       | °C                      |

|         | -0.5 to<br>0 to<br>-40 to | -0.5 to 17<br>10<br>640 |

<sup>\*</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING NUMBERS:**

M089/M099 B1 for dual-in-line plastic package M089/M099 D1 for dual-in-line ceramic package

M089/M099 F1 for dual-in-line ceramic package, frit seal

<sup>\*\*</sup> With respect to V<sub>SS</sub> (GND) pin.

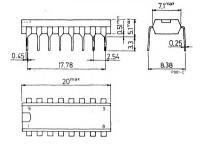

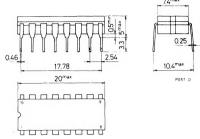

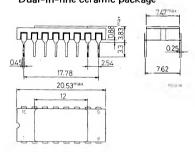

# MECHANICAL DATA (dimensions in mm)

#### Dual-in-line plastic package

# Dual-in-line ceramic package frit seal

# Dual-in-line ceramic package

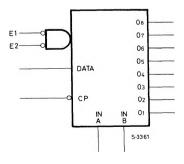

# PIN CONNECTIONS

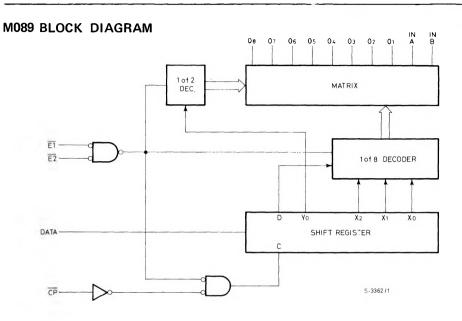

# LOGIC DIAGRAM

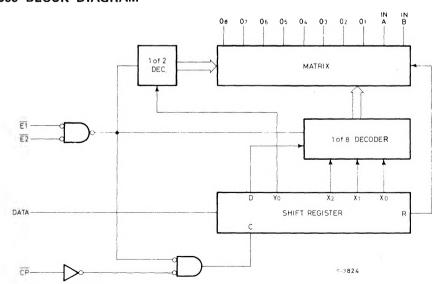

#### M099 BLOCK DIAGRAM

#### CIRCUIT DESCRIPTION

The M089 and M099 are capable of forming any combination of switch conditions in an 8x2 matrix. Each switch is individually set and a latch maintains it in its set condition.

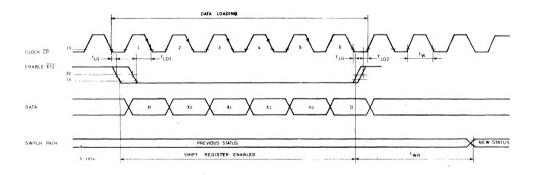

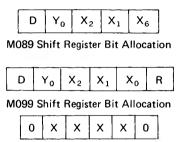

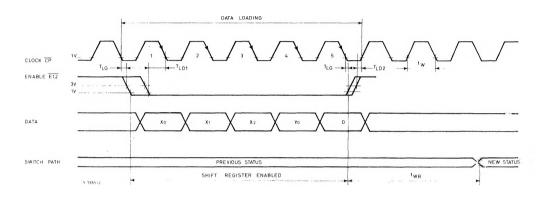

The switch address and control bits are loaded serially into an internal shift register (5 bit for M089, 6 bit for M099) when inputs  $E_1$ , and  $E_2$  are low. The address bits in both matrices consist of: 3 input selection bits  $(X_0-X_2)$  and a single output selection bit  $(Y_0)$ . A fifth (control) bit (D) defines whether the chosen switch is to be opened or closed.

In the M099 a sixth bit (R) is an "all switch reset". Reset occurs on the low to high transition of the enable inputs when both D and R are zero.

During normal selection the R bit must be a 1.

M099 Reset Word.

Data bits are clocked into the shift register on the high to low transition of the clock input (CP). If more than 5 (or 6 in the case of the M090) clock transmission are applied during loading of the shift register the last 5 (or 6) data bits are loaded into it. The status of the switch addressed changes on the low to high transition of one or both enable inputs.

#### **ENABLE INPUTS TRUTH TABLE**

| -              | _              | FUNC                | CTION                |  |  |

|----------------|----------------|---------------------|----------------------|--|--|

| E <sub>1</sub> | Ē <sub>2</sub> | M089                | M099                 |  |  |

| L              | L              | Data                | Load                 |  |  |

|                | L              |                     | addressed            |  |  |

| L              |                | addressed<br>switch | switch<br>changed or |  |  |

| _              |                | changed             | all switch<br>reset  |  |  |

#### DATA BIT TRUTH TABLE

| – M089 – |                                       |  |  |  |

|----------|---------------------------------------|--|--|--|

| Data     | Switch status after enable transition |  |  |  |

| L        | disconnect                            |  |  |  |

| Н        | connect                               |  |  |  |

#### DATA AND RESET BIT TRUTH TABLE

| – M099 only – |   |                               |  |  |  |

|---------------|---|-------------------------------|--|--|--|

| D             | R | Switch status                 |  |  |  |

| L             | L | all switches reset            |  |  |  |

| н             | L | no change                     |  |  |  |

| L             | н | addressed switch disconnected |  |  |  |

| н             | н | addressed switch connected    |  |  |  |

## DATA BITS TRUTH TABLE FOR SWITCH SELECTION

|      | O <sub>1</sub><br>Y <sub>0</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | 02   | 03   | 04   | 05   | 06   | 07   | Og   |

|------|-------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| IN A | 1111                                                                          | 1011 | 1101 | 1001 | 1110 | 1010 | 1100 | 1000 |

| IN B | 0111                                                                          | 0011 | 0101 | 0001 | 0110 | 0010 | 0100 | 0000 |

For example to address the switch connecting IN A to  ${\rm O}_5$  the shift register must be loaded with the code:

|               | M089                                                          | M099            |

|---------------|---------------------------------------------------------------|-----------------|

|               | D Y <sub>0</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | D Y0 X2 X1 X0 R |

| to connect    | 11110                                                         | 111101          |

| to disconnect | 01110                                                         | 011101          |

# **ELECTRICAL CHARACTERISTICS** ( $T_{amb}=0$ to 70°C for M089/M099 B1; -40 to 70°C for M089/M099 F1, D1; $V_{DD}=14V$ to 16V unless otherwise specified)

| Parameter         |                                                                                   | Test conditions                     | Min.                                                                                                        | Тур. | Max. | Unit            |     |

|-------------------|-----------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|-----------------|-----|

| R <sub>ON</sub> * | ON-resistance                                                                     |                                     | T <sub>amb</sub> = 25°C<br>V <sub>i</sub> (A, B)= 3.5V<br>V <sub>DD</sub> = 14V I <sub>D(min)</sub> = 10 mA |      | 10   | 15              | Ω   |

| ΔR <sub>ON</sub>  | ON-resistance variation in any package                                            |                                     | T <sub>amb</sub> = 25°C<br>V <sub>i</sub> = 3.5V<br>V <sub>DD</sub> = 14V<br>I <sub>D</sub> = 10 mA         |      |      | ± 2             | %   |

| I <sub>DD</sub>   | Supply current                                                                    |                                     |                                                                                                             |      | 7    | mA              |     |

| LI                | Input leakage                                                                     | pins 4, 5<br>12, 13                 | V <sub>i</sub> = 5V                                                                                         |      |      | 1               | μА  |

|                   |                                                                                   | pins 1, 9                           | V <sub>iA</sub> , V <sub>iB</sub> = 4.5V<br>V <sub>O1</sub> , V <sub>O8</sub> = 1.5V                        |      |      | 0.2             | μА  |

|                   |                                                                                   | pins 1, 5                           | V <sub>iA</sub> , V <sub>iB</sub> = 6V<br>V <sub>O1</sub> , V <sub>O8</sub> = 1.5V                          |      |      | 1               | μА  |

| ILO               | Output leakage                                                                    | pins 2, 6, 7<br>8, 10, 14<br>15, 16 | V <sub>O1</sub> , V <sub>O8</sub> = 4.5V<br>V <sub>iA</sub> , V <sub>iB</sub> = 1.5V                        |      |      | 0.2             | μА  |

|                   |                                                                                   |                                     | V <sub>O1</sub> , V <sub>O8</sub> = 6V<br>V <sub>iA</sub> , V <sub>iB</sub> = 1.5V                          |      |      | 1               | μА  |

| V <sub>low</sub>  | Logic 0 input level                                                               |                                     | All inputs                                                                                                  | -0.3 |      | 0.8             | V   |

| $V_{high}$        | Logic 1 input level                                                               |                                     | All inputs                                                                                                  | 4.5  |      | V <sub>DD</sub> | V   |

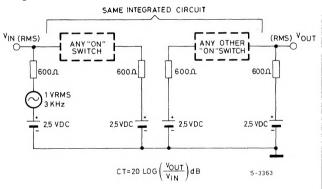

| СТ                | Cross-talk attenuation                                                            |                                     | See fig. 4                                                                                                  | 90   | 95   |                 | dB  |

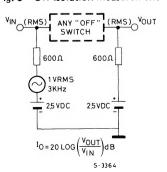

| l <sub>O</sub>    | Off isolation                                                                     |                                     | See fig. 5                                                                                                  | 90   | 95   |                 | dB  |

| f <sub>CL</sub>   | Maximum clock input frequency  Lag time  Lead time  Write time  Clock pulse width |                                     | See fig. 6 for M089<br>See fig. 7 for M099                                                                  |      |      | 1               | MHz |

| T <sub>LG</sub>   |                                                                                   |                                     |                                                                                                             | 100  |      |                 | ns  |

| T <sub>LD1</sub>  |                                                                                   |                                     |                                                                                                             | 400  |      |                 |     |

| T <sub>LD2</sub>  |                                                                                   |                                     |                                                                                                             | 150  |      |                 | ns  |

| T <sub>WR</sub>   |                                                                                   |                                     |                                                                                                             |      |      | 3               | μs  |

| tw                |                                                                                   |                                     |                                                                                                             | 0.4  |      | 100             | μs  |

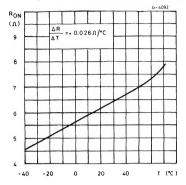

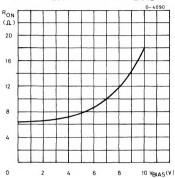

$<sup>^{*}</sup>$  See fig. 1 and 2 for R<sub>ON</sub> variation with temperature and V<sub>BIAS</sub>.

Fig. 1 - R<sub>ON</sub> derating vs. temperature typ.

Fig. 2 - R<sub>ON</sub> derating vs. V<sub>BIAS</sub>.

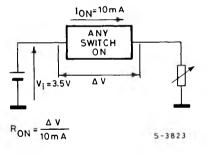

#### **TEST CIRCUITS**

Fig. 3 - R<sub>ON</sub> measurement

Fig. 4 - Crosstalk measurements

Fig. 5 - Off isolation measurement

## TIMING DIAGRAMS

Fig. 6 - M089 timing diagram

Fig. 7 - M099 timing diagram