# REMOTE CONTROL ENCODER/DECODER CIRCUITS

- M145026 ENCODER

- M145027/M145028 DECODERS

- MAY BE ADDRESSED IN EITHER BINARY OR TRINARY

- TRINARY ADDRESSING MAXIMIZES NUMBER OF CODES

- INTERFACES WITH RF, ULTRASONIC, OR INFRARED TRANSMISSION MEDIAS

- DOUBLE TRANSMISSIONS FOR ERROR CHECKING

- 4.5V TO 18V OPERATION

- ON-CHIP R/C OSCILLATOR, NO CRYSTAL REQUIRED

- HIGH EXTERNAL COMPONENT TOLER-ANCE, CAN USE 5% COMPONENTS

- STANDARD CMOS B-SERIES INPUT AND OUTPUT CHARACTERISTICS

- APPLICATIONS INCLUDE GARAGE DOOR OPENERS, REMOTE CONTROLLED TOYS, SECURITY MONITORING, ANTITHEFT SYSTEMS, LOW END DATA TRANSMIS-SIONS, WIRE LESS TELEPHONES

The M145026 encodes nine bits of information and serially transmits this information upon receipt of a transmit enable, TE, (active low) signal. Nine inputs may be encoded with trinary

data (0, 1, open) to allow  $3^9$  (19,683) different codes.

Two decoders are presently available. Both use the same transmitter – the M145026. The decoders will receive the 9-bit word and will interpret some of the bits as address codes and some as data. The M145028 treats all nine bits as address. If no errors are received, the M145027 outputs the four data bits when the transmitter sends address codes that match that of the receiver. A valid transmission output goes high on both decoders when they recognize an address that matches that of the decoder. Other receivers can be produced with different address/data ratios.

All the devices are available in 16 lead plastic package.

M145027 B1 M145028 B1

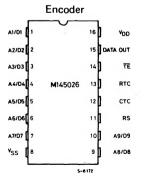

## CONNECTION DIAGRAMS

# ABSOLUTE MAXIMUM RATINGS

| V <sub>DD</sub> DC Supply Voltage          | -0.5 to +18                  | ٧  |

|--------------------------------------------|------------------------------|----|

| V <sub>I</sub> Input Voltage, All Inputs   | -0.5 to V <sub>DD</sub> +0.5 | V  |

| I <sub>I</sub> DC Current Drain Per Pin    | 10                           | mΑ |

| T <sub>stg</sub> Storage Temperature Range | -65 to +150                  | °C |

| Top Operating Temperature Range            | -40 to +85                   | °C |

Stresses above those listed under "Absolute Maximum Ratings" may causes permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# SWITCHING CHARACTERISTICS (C<sub>L</sub> = 50 pF, T<sub>amb</sub> = 25°C)

|                 | Parameter                                                                                                              | VDD           | Min            | Тур             | Max               | Unit            |

|-----------------|------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-----------------|-------------------|-----------------|

| tTLH<br>tTHL    | Output Rise and Fall Time                                                                                              | 5<br>10<br>15 | -<br>-<br>-    | 100<br>50<br>40 | 200<br>100<br>80  | ns              |

| tTLH<br>tTHL    | Data In Rise and Fall Time (M145027, M145028)                                                                          | 5<br>10<br>15 | -<br>-         | -               | 15<br>15<br>15    | μς              |

| fCL             | Encoder Clock Frequency                                                                                                | 5<br>10<br>15 | 0<br>0<br>0    | -<br>-<br>-     | 2<br>5<br>5       | MHz             |

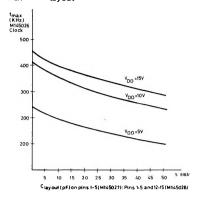

| fCL             | Maximum Decoder Frequency<br>(Referenced to Encoder Clock) (See Figure 9)                                              | 5<br>10<br>15 | -<br>-<br>-    | -<br>-<br>-     | 240<br>410<br>450 | kHz             |

| <sup>t</sup> WL | TE Pulse Width                                                                                                         | 5<br>10<br>15 | 65<br>30<br>20 | -<br>-<br>-     | -<br>-<br>-       | ns              |

|                 | System Propagation Delay (TE to Valid Transmission)                                                                    | -             | _              | 182             | _                 | Clock<br>Cycles |

|                 | Tolerance on Timing Components ( $\Delta$ RTC + $\Delta$ CTC + $\Delta$ R1 + $\Delta$ C1) ( $\Delta$ R2 + $\Delta$ C2) | _             | _<br>_         | <u>-</u>        | ±25<br>±25        | %               |

# **ELECTRICAL CHARACTERISTICS**

|                 | D                                                                                                                            |                    | -40                           | 0°C                  | 25° C                       |                                |                      | +85° C                        |                      |        |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|----------------------|-----------------------------|--------------------------------|----------------------|-------------------------------|----------------------|--------|

|                 | Parameter                                                                                                                    | V <sub>DD</sub>    | Min                           | Max                  | Min                         | Тур                            | Max                  | Min                           | Max                  | Unit   |

| VOL             | Output Voltage VI = VDD or 0 "0" Level                                                                                       | 5<br>10<br>15      | -<br>-<br>-                   | 0.05<br>0.05<br>0.05 | -<br>-<br>-                 | 0<br>0<br>0                    | 0.05<br>0.05<br>0.05 |                               | 0.05<br>0.05<br>0.05 | >      |

| ∨он             | V <sub>I</sub> = 0 or V <sub>DD</sub> "1" Level                                                                              | 5<br>10<br>15      | 4.95<br>9.95<br>14.95         | 9                    | 4.95<br>9.95<br>14.95       | 5<br>10<br>15                  | 13                   | 4.95<br>9.95<br>14.95         | 111                  | \<br>V |

| VIL             | Input Voltage<br>(V <sub>O</sub> = 4.5 or 0.5V)<br>(V <sub>O</sub> = 0.9 or 1V)<br>(V <sub>O</sub> = 13.5 or 1.5V) "0" Level | 5<br>10<br>15      | -11                           | 1.5<br>3<br>4        |                             | 2.25<br>4.50<br>6.25           | 1.5<br>3<br>4        | j i i                         | 1.5<br>3<br>4        | >      |

| ViH             | (V <sub>O</sub> = 0.5 or 4.5V)<br>(V <sub>O</sub> = 1.0 or 9V)<br>(V <sub>O</sub> = 1.5 or 13.5V) "1" Level                  | 5<br>10<br>15      | 3.5<br>7<br>11                | 811                  | 3.5<br>7<br>11              | 2.75<br>5.50<br>8.25           | ¥11                  | 3.5<br>7<br>11                | T. I I               | >      |

| Гон             | Output Drive Current (VOH = 2.5V) (VOH = 4.6V) (VOH = 9.5V) (VOH = 13.5V)                                                    | 5<br>5<br>10<br>15 | -2.5<br>-0.52<br>-1.3<br>-3.6 | 1 -                  | -2.1<br>-0.44<br>-1.1<br>-3 | -4.2<br>-0.88<br>-2.25<br>-8.8 | 3111                 | -1.7<br>-0.36<br>-0.9<br>-2.4 | 3111                 | mA     |

| IOL             | $(V_{OL} = 0.4V)$<br>$(V_{OL} = 0.5V)$ Sink<br>$(V_{OL} = 1.5V)$                                                             | 5<br>10<br>15      | 0.52<br>1.3<br>3.6            | 1 <del>- 1</del>     | 0.44<br>1.1<br>3            | 0.88<br>2.25<br>8.8            | =                    | 0.36<br>0.9<br>2.4            | =                    | mA     |

| 11              | Input Current<br>TE (M145026, Pullup Device)                                                                                 | 5<br>10<br>15      | -<br>-<br>-                   | -<br>-<br>-          | 3<br>16<br>35               | 4<br>20<br>45                  | 7<br>26<br>55        | -                             |                      | μА     |

| l <sub>i</sub>  | Input Current<br>RS (M145026)<br>Data In (M145027, M145028)                                                                  | 15                 | -                             | ±0.3                 | -                           | ±0.00001                       | ±0.3                 | _                             | ±1.0                 | μА     |

| Ч               | Input Current<br>A1/D1-A9/D9 (M145026)<br>A1-A5 (M145027)<br>A1-A9 (M145028)                                                 | 5<br>10<br>15      | -                             | =                    | -2"                         | ±55<br>±300<br>±650            | ±80<br>±340<br>±725  | 2                             | 110                  | μА     |

| CI              | Input Capacitance (V <sub>I</sub> = 0)                                                                                       | _                  | -                             | -                    | _                           | 5                              | 7.5                  | _                             | -                    | pF     |

| <sup>1</sup> DD | Quiescent Current - M145026                                                                                                  | 5<br>10<br>15      | 111                           | -<br>-               | -<br>-                      | 0.0050<br>0.0100<br>0.0150     | 0.10<br>0.20<br>0.30 | 1 1 1                         | 1 1 1                | μΑ     |

| IDD             | Quiescent Current<br>M145027, M145028                                                                                        | 5<br>10<br>15      | 1 1 1                         | 1                    | -<br>-<br>-                 | 30<br>60<br>90                 | 50<br>100<br>150     | 111                           | 1 1 1                | μА     |

| IT.             | Total Supply Current<br>M145026 (f <sub>CL</sub> = 20 kHz)                                                                   | 5<br>10<br>15      | 111                           | 111                  | 111                         | 100<br>200<br>300              | 200<br>400<br>600    | 1 1                           | 111                  | μА     |

| ۱ <sub>T</sub>  | Total Supply Current<br>M145027, M145028 (f <sub>CL</sub> = 20 kHz)                                                          | 5<br>10<br>15      | 1 1 1                         | -<br>-<br>-          | -<br>-<br>-                 | 200<br>400<br>600              | 400<br>800<br>1200   |                               |                      | μА     |

# **OPERATING CHARACTERISTICS**

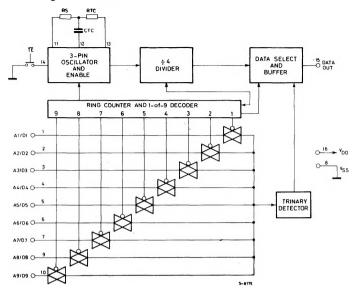

## M145026

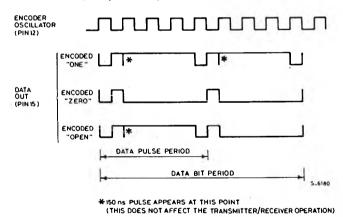

The encoder will serially transmit nine bits of trinary data as defined by the state of the A1/D1-A9/D9 input pins. These pins can be in either of three states (0,1,open) allowing  $3^9=19683$  possible codes. The transmit sequence will be initiated by a low level of the  $\overline{TE}$  input pin. Each time the  $\overline{TE}$  input is forced low the encoder will output two identical data words. This redundant information is used by the receiver to reduce errors. If the  $\overline{TE}$  input is kept low, the encoder will continuously transmit the data words. The transmitted words are self-completing (two words will be transmitted for each  $\overline{TE}$  pulse). Each transmitted data bit is encoded into two data pulses. A logic zero will be encoded as two consecu-

Each transmitted data bit is encoded into two data pulses. A logic zero will be encoded as two consecutive short pulses, a logic one by two consecutive long pulses, and an open as a long pulse followed by a short pulse. The input state is determined by using a weak output device to try to force each input first low, then high. If only a high state results from the two tests, the input is assumed to be hard wired to  $V_{DD}$ . If only a low state is obtained, the input is assumed to be hard wired to  $V_{SS}$ . If both a high and a low can be forced at an input, it is assumed to be open and is encoded as such.

The transmit sequence is enabled by a logic zero on the TE input. This input has an internal pullup device so that a simple switch may be used to force the input low. While TE is high the encoder is completely disabled, the oscillator is inhibited and the current drain is reduced to quiescent current. When TE is brought low, the oscillator is started, and an internal reset is generated to initialize the transmit sequence. Each input is then sequentially selected and a determination is made as to input logic state. This information is serially transmitted via the Data Out output pin.

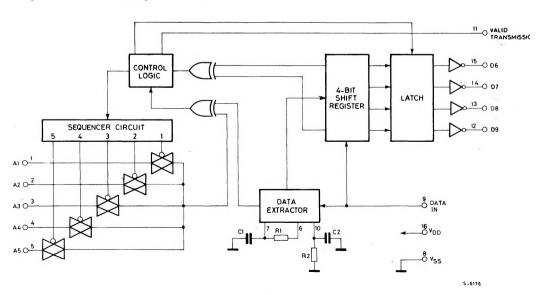

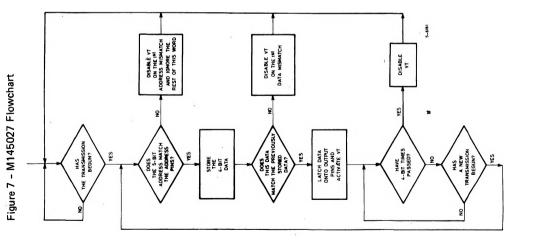

#### M145027

The decoder will receive the serial data from the encoder, check it for errors and output data if valid. The transmitted data consisting of two identical data words is examined bit by bit as it is received. The first five bits are assumed to be address bits and must be encoded to match the address inputs at the receiver. If the address bits match, the next four (data) bits are stored and compared to the last valid data stored. If this data matches, the VT pin will go high on the 2nd rising edge of the 9th bit of the first word. Between the two data words no signal is sent for three data bit times. As the second encoded word is received, the address must again match, and if it does, the data bits are checked against the previously stored data bits. If the two words of data (four bits each) match, the data is transferred to the output data latches and will remain until new data replaces it. At the same time, the Valid Transmission output pin is brought high and will remain high until an error is received or until no input signal is received for four data bit times.

Although the address information is encoded in trinary fashion, the data information must be either a one or a zero. A trinary (open) will be decoded as a logic one.

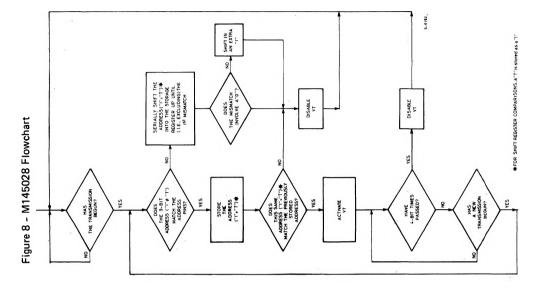

#### M145028

This receiver operates in the same manner as the M145027 except that nine address bits are used and no data output is available. The Valid Transmission output is used to indicate that a valid signal has been received.

Although address information normally is encoded in trinary, the designer should be aware that, for the M145028, the ninth address bit (A9) must be either a one or a zero. This part, therefore, can accept only  $2 \times 3^8 = 13,122$  different codes. A trinary (open) A9 will be interpreted as a logic 1. However if the transmitter sends a trinary (or logic 1) and the receiver address is a logic 1 (or trinary) respectively, the valid transmission output will be shortened to the R1 x C1 time constant.

#### DOUBLE TRANSMISSION DECODING

Although the encoder sends two words for error checking, a decoder does not necessarily wait for two transmitted words to be received before issuing a valid transmission output. Refer to the flowcharts in Figure 7 and 8.

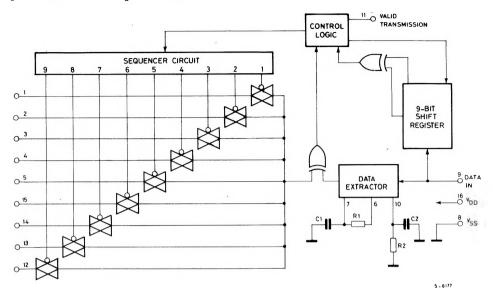

Fig. 1 - Encoder block diagram M145026

Fig. 2 - Decoder block diagram M145027

Fig. 3 - Decoder block diagram M145028

## PIN DESCRIPTION

## M145026 ENCODER

#### A1/D1-A9/D9

These inputs will be encoded and the data serially output from the encoder.

# $V_{SS}$

The most negative supply (usually ground).

### RS, CTC, RTC

These pins are part of the oscillator section of the encoder. If an external signal source is used instead of the internal oscillator it should be connected to the RS input and the RTC and CTC pins should be left open.

# TE

This Transmit-Enable (active low) input will initiate transmission when forced low. A pullup device will keep this input high normally.

## **Data Out**

This is the output of the encoder that will present the serially encoded signals.

#### $V_{DD}$

The most positive supply.

#### M145027/M145028 DECODERS

### A1-A5 (M145027) / A1-A9 (M145028)

These are the address inputs that must match the encoder inputs A1/D1-A5/D5 in the case of M145027 or A1/D1-A0/D9 in the case of M145028, in order for the decoder to output data.

### D6-D9 (M145027)

These outputs will give the information that is presented to the encoder inputs A6/D6-A9/D9.

Note: Only binary data will be acknowledged, a trinary open will be decoded as logic one.

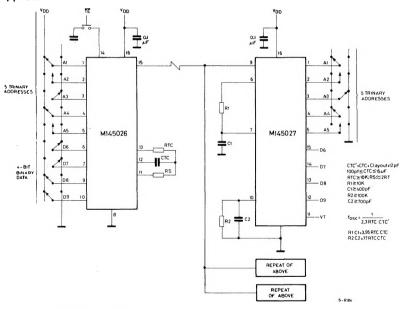

## R1. C1

These pins accept a resistor and capacitor that are used to determine whether a narrow pulse or a wide pulse has been encoded. The time constant  $R1 \times C1$  should be set to 1.72 transmit clock periods.  $R1C1 = 3.95 \ RTC \times CTC$ .

#### R2/C2

This pin accepts a resistor to  $V_{SS}$  and a capacitor to  $V_{SS}$  that are used to detect both the end of an encoded word and the end of transmission. The time constant  $R2 \times C2$  should be 33.5 transmit clock periods (four data bit periods). This time constant is used to determine that the Data In input has remained low for four data bit times (end of transmission). A separate comparator looks at a voltage equivalent two data bit times (0.4 R2C2) to detect the dead time between transmitted words. R2C2 = 77 x RTC x CTC.

## Valid Transmission, VT

This output will go high when the following conditions are satisfied:

- 1. the transmitted address matches the receiver address, and

- 2. the transmitted data matches the last valid data received (M145028 only).

VT will remain high until either a mismatch is received, or no input signal is received for four data data bit times.

## $V_{DD}$

The most positive supply

## VSS

The most negative supply (usually ground).

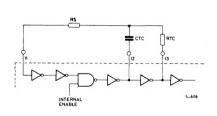

Figure 4 - Encoder Oscillator Information

This oscillator will operate at a frequency determined by the external RC network; i.e.,

for 1 kHz  $\leq$  f  $\leq$  400 kHz

where: CTC = CTC + C layout + 12 pF

RS ≈ 2 RTC

RS ≥ 20 k

RTC ≥ 10 k

$400 \text{ pF} < \text{CTC} < \mu\text{F}$

The value for RS should be chosen to be about 2 times RTC. This range will ensure that current through RS is insignificant compared to current through RTC. The upper limit for RS must ensure that RS  $\times$  5 pF (input capacitance) is small compared to RTC  $\times$  CTC.

For frequencies outside the indicated range, the formula will be less accurate. The actual oscillation range of this circuit is from less than 1 Hz to over 1 MHz.

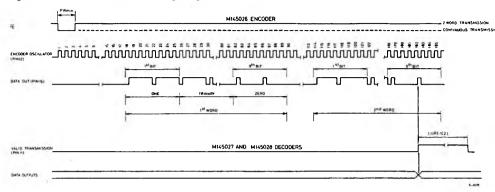

Figure 5 - Encoder/Decoder Timing Diagram

Figure 6 - Encoder Data Waveforms (M145026)

Figure 9 - M145027/M145028 ( $f_{max}$  vs.  $C_{layout}$ )

Figure 10 - Typical Application

Example R/C Values (All Resistors and Capacitors are ± 5%)

| f <sub>osc</sub> (kHz) | RTC  | CTC'    | RS    | R1   | C1      | R2    | C2       |

|------------------------|------|---------|-------|------|---------|-------|----------|

| 362                    | 10 k | 120 pF  | 20 k  | 10 k | 470 pF  | 100 k | 910 pF   |

| 181                    | 10 k | 240 pF  | 20 k  | 10 k | 910 pF  | 100 k | 1800 pF  |

| . 88.7                 | 10 k | 490 pF  | 20 k  | 10 k | 2000 pF | 100 k | 3900 pF  |

| 42.6                   | 10 k | 1020 pF | 20 k  | 10 k | 3900 pF | 100 k | 7500 pF  |

| 21.5                   | 10 k | 2020 pF | 20 k  | 10 k | 8200 pF | 100 k | 0.015 µF |

| 8.53                   | 10 k | 5100 pF | 20 k  | 10 k | 0.02 μF | 200 k | 0.02 μF  |

| 1.71                   | 50 k | 5100 pF | 100 k | 50 k | 0.02 μF | 200 k | 0.1 µF   |

(CTC' = CTC + 20 pF)