# 8 STAGE PRESETTABLE SYNCHRONOUS DOWN COUNTERS

- HIGH SPEED f<sub>MAX</sub> = 34 MHz (Typ) at V<sub>CC</sub> = 5V

- LOW POWER DISSIPATION  $I_{CC} = 4 \mu A \text{ (MAX.)}$  at  $T_A = 25 ^{\circ}\text{C}$

- HIGH NOISE IMMUNITY V<sub>NIH</sub> = V<sub>NIL</sub> = 28% V<sub>CC</sub> (MIN.)

- OUTPUT DRIVE CAPABILITY 10 LSTTL LOADS

- SYMMETRICAL OUTPUT IMPEDANCE |I<sub>OH</sub>| = I<sub>OL</sub> = 4 mA (MIN.)

- BALANCED PROPAGATION DELAYS

tpi H = tphl

- WIDE OPERATING VOLTAGE RANGE Vcc (OPR) = 2V to 6V

- PIN AND FUNCTION COMPATIBLE WITH 40102B/40103B

#### DESCRIPTION

The M54/74HC40102/40103 are high speed CMOS 8-STAGE PRESETTABLE SYNCHRONOUS DOWN COUNTERS fabricated with silicon gate C<sup>2</sup>MOS technology. They achieve the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation.

The HC40102, and HC40103 consist of an 8-stage synchronous down counter with a single output which is active when the internal count is zero. The HC40102 is configured as two cascaded 4-bit BCD counters, and the HC40103 contains a single 8-bit binary counter. Each type has control inputs for enabling or disabling the clock, for clearing the counter to its maximum count, and for presetting the counter either synchronously or asynchronously. All control inputs and the CARRY-OUT/ZERO-DETECT output are active-low logic. In normal operation, the counter is decremented by one count on each positive transition of the CLOCK, Counting is inhibited when the CARRY-IN/COUNTER ENABLE (CI/CE) input is high. The CARRY-OUT/ZERO-DETECT (CO/ZD) output goes low when the count reaches zero if the CI/CE input is low, and remains low for one full clock period. When the SYNCHRONOUS PRESET-ENABLE (SPE) input is low, data at the J input is clocked into the counter on the next positive clock transition regardless of the state of the CI/CE input.

#### **DESCRIPTION** (Continued)

When the ASYNCHRONOUS PRESET-ENABLE (APE) input is low, data at the J inputs is asynchronously forced into the counter regardless of the state of the SPE, CI/CE, or CLOCK inputs. J Inputs J0-J7 represent two 4-bit BCD words for the HC40102 and a single 8-bit binary word for the HC40103. When the CLEAR (CLR input is low, the counter is asynchronously cleared to its maximum count (99<sub>10</sub>for the HC40102 and 255<sub>10</sub> for the HC40103 regardless of the state of any other input.

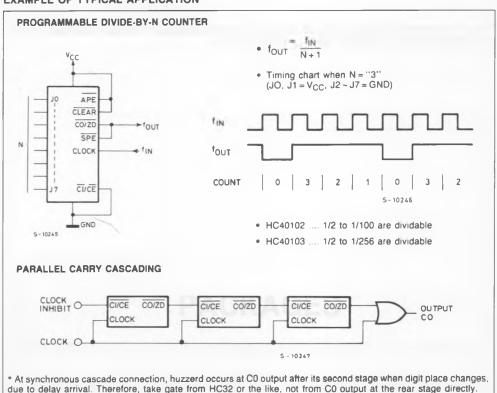

The precedence relationship between control input is indicated in the truth table. If all control inputs are high at the time of zero count, the counters will jump to the maximum count, giving a counting sequence of 100 or 256 clock pulses long. The HC40102 and HC40103 may be cascaded using the CI/CE input and the CO/ZD output, in either a synchronous or ripple mode. All inputs are equipped with protection circuits against static discharge and transient excess voltage.

#### TRUTH TABLE

| CC    | NTROL | . INPUT | S     | MODE                | FUNCTIONAL DESCRIPTION                                |  |  |  |  |  |  |  |

|-------|-------|---------|-------|---------------------|-------------------------------------------------------|--|--|--|--|--|--|--|

| CLEAR | APE   | SPE     | CI/CE | MODE                | TOTAL DESCRIPTION                                     |  |  |  |  |  |  |  |

| Н     | Н     | Н       | Н     | COUNT INHIBIT       | EVEN IF CLOCK IS GIVEN, NO COUNT IS MADE.             |  |  |  |  |  |  |  |

| Н     | Н     | Н       | L     | REGULAR COUNT       | DOWN COUNT AT RISING EDGE OF CLOCK.                   |  |  |  |  |  |  |  |

| Н     | Н     | L       | Х     | SYNCHRONOUS PRESET  | DATA OF PI TERMINAL IS PRESET AT RISING EDGE OF CLOCK |  |  |  |  |  |  |  |

| Н     | L     | Х       | Х     | ASYNCHRONOUS PRESET | DATA OF PI TERMINAL IS ASYNCHRONOUSLY PRESET TO CLOCK |  |  |  |  |  |  |  |

| L     | Х     | Х       | Х     | CLEAR               | COUNTER IS SET TO MAXIMUM COUNT.                      |  |  |  |  |  |  |  |

X. DON'T CARE - MAXIMUM COUNT: "99" FOR HC40102 AND "255" FOR HC40103

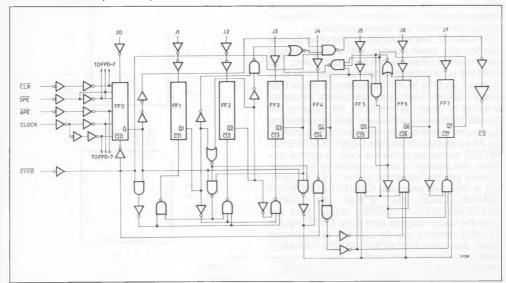

#### **LOGIC DIAGRAM (HC40102)**

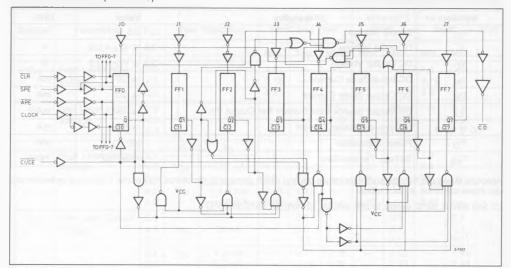

#### LOGIC DIAGRAM (HC40103)

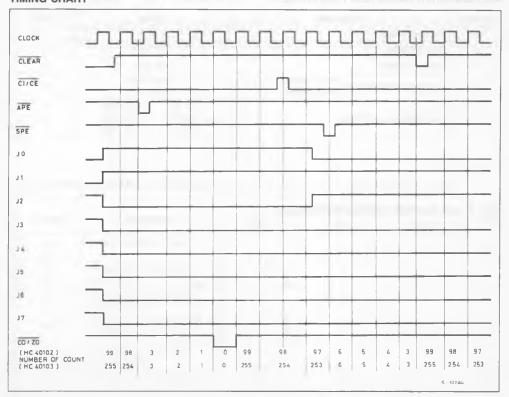

### **TIMING CHART**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                    | Value                          | Unit |

|------------------|----------------------------------------------|--------------------------------|------|

| Vcc              | Supply Voltage                               | - 0.5 to 7                     | V    |

| VI               | DC Input Voltage                             | -0.5 to V <sub>CC</sub> +0.5   | V    |

| Vo               | DC Output Voltage                            | - 0.5 to V <sub>CC</sub> + 0.5 | V    |

| I <sub>IK</sub>  | DC Input Diode Current                       | ± 20                           | mA   |

| lok              | DC Output Diode Current                      | ± 20                           | mA   |

| 10               | DC Output Source Sink Current Per Output Pin | ± 25                           | mA   |

| ICC or IGND      | DC V <sub>CC</sub> or Ground Current         | ± 50                           | mA   |

| PD               | Power Dissipation                            | 500 (*)                        | mW   |

| T <sub>stg</sub> | Storage Temperature                          | - 65 to 150                    | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

(°) 500 mW: = 65°C derate to 300 mW by 10 mW/°C: 65°C to 85°C

#### RECOMMENDED OPERATING CONDITIONS

| Symbol                          | Parameter                                     | V                                   | Value                             |    |  |  |  |

|---------------------------------|-----------------------------------------------|-------------------------------------|-----------------------------------|----|--|--|--|

| Vcc                             | Supply Voltage                                | to 6                                | V                                 |    |  |  |  |

| VI                              | Input Voltage                                 | 0 1                                 | o V <sub>CC</sub>                 | V  |  |  |  |

| Vo                              | Output Voltage                                | 0 t                                 | o V <sub>CC</sub>                 | ٧  |  |  |  |

| TA                              | Operating Temperature 74HC Series 54HC Series |                                     | ) to 85<br>5 to 125               | °C |  |  |  |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise and Fall Time                      | V <sub>CC</sub> (2 V<br>4.5V<br>6 V | 0 to 1000<br>0 to 500<br>0 to 400 | ns |  |  |  |

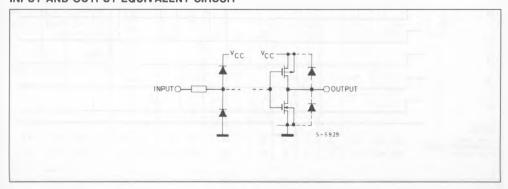

#### INPUT AND OUTPUT EQUIVALENT CIRCUIT

#### DC ELECTRICAL CHARACTERISTICS

| Symbol          | Parameter                    | Vcc                             | Test                                                       | Condition                                | T <sub>A</sub> = 25°C<br>54HC and 74HC |                                   | - 40 to 85°C<br>74HC              |                                   | - 55 to 125°C<br>54HC             |                                   | Unit                              |    |

|-----------------|------------------------------|---------------------------------|------------------------------------------------------------|------------------------------------------|----------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|----|

|                 |                              |                                 |                                                            |                                          | Min.                                   | Тур.                              | Max.                              | Min.                              | Max.                              | Min.                              | Max.                              |    |

| V <sub>IH</sub> | High Level Input<br>Voltage  | 2.0<br>4.5<br>6.0               |                                                            |                                          | 1.5<br>3.15<br>4.2                     |                                   |                                   | 1.5<br>3.15<br>4.2                |                                   | 1.5<br>3.15<br>4.2                |                                   | ٧  |

| V <sub>IL</sub> | Low Level Input<br>Voltage   | 2.0<br>4.5<br>6.0               |                                                            |                                          |                                        |                                   | 0.5<br>1.35<br>1.8                | _                                 | 0.5<br>1.35<br>1.8                |                                   | 0.5<br>1.35<br>1.8                | ٧  |

| V <sub>OH</sub> | High Level Output<br>Voltage | 2.0<br>4.5<br>6.0<br>4.5<br>6.0 | V <sub>I</sub><br>V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> - 20 μA - 4.0 mA - 5.2 mA | 1.9<br>4.4<br>5.9<br>4.18<br>5.68      | 2.0<br>4.5<br>6.0<br>4.31<br>5.8  |                                   | 1.9<br>4.4<br>5.9<br>4.13<br>5.63 |                                   | 1.9<br>4.4<br>5.9<br>4.10<br>5.60 |                                   | V  |

| V <sub>OL</sub> | Low Level Output<br>Voltage  | 2.0<br>4.5<br>6.0<br>4.5<br>6.0 | V <sub>IH</sub><br>or<br>V <sub>IL</sub>                   | 20 μA<br>4.0 mA<br>5.2 mA                |                                        | 0.0<br>0.0<br>0.0<br>0.17<br>0.18 | 0.1<br>0.1<br>0.1<br>0.26<br>0.26 |                                   | 0.1<br>0.1<br>0.1<br>0.33<br>0.33 |                                   | 0.1<br>0.1<br>0.1<br>0.40<br>0.40 | V  |

| It              | Input Leakage<br>Current     | 6.0                             | V <sub>1</sub> = V                                         | CC or GND                                | -                                      | -                                 | ±0.1                              | _                                 | ± 1.0                             | _                                 | ±1.0                              | μА |

| lcc             | Quiescent Supply<br>Current  | 6.0                             | $V_{\parallel} = V$                                        | CC or GND                                | -                                      | _                                 | 4                                 | _                                 | 40                                | _                                 | 80                                | μА |

## AC ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5V$ , $T_A = 25$ °C, $C_L = 15pF$ , Input $t_f = t_f = 6ns$ )

| Symbol                               |                                         | 54HC and 74HC |      |      |      |  |  |  |

|--------------------------------------|-----------------------------------------|---------------|------|------|------|--|--|--|

|                                      | Parameter                               | Min.          | Тур. | Max. | Unit |  |  |  |

| t <sub>TLH</sub>                     | Output Transition Time                  |               | 4    | 8    |      |  |  |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay Time<br>CK-CO/ZO      |               | 27   | 42   | ns   |  |  |  |

| t <sub>PHL</sub>                     | Propagation Delay Time<br>(APE-CO/ZD)   |               | 34   | 53   | ns   |  |  |  |

| tpHL                                 | Propagation Delay Time<br>(CL-CO/ZD)    |               | 27   | 42   | ns   |  |  |  |

| tpHL                                 | Propagation Delay Time<br>(CI/CE-CO/ZO) |               | 11   | 19   | ns   |  |  |  |

| fMAX                                 | Maximum Clock Frequency                 | 22            | 34   |      | MH:  |  |  |  |

## AC ELECTRICAL CHARACTERISTICS ( $C_L = 50pF$ , Input $t_f = t_f = 6ns$ )

| Symbol                               | Parameter                                    | v <sub>cc</sub>   | V <sub>CC</sub> Test Condition |               | T <sub>A</sub> = 25°C<br>54HC and 74HC |                 |                 | o 85°C<br>HC    | - 55 to 125°C<br>54HC |                 | Unit |

|--------------------------------------|----------------------------------------------|-------------------|--------------------------------|---------------|----------------------------------------|-----------------|-----------------|-----------------|-----------------------|-----------------|------|

|                                      |                                              |                   |                                | Min.          | Тур.                                   | Max.            | Min.            | Max.            | Min.                  | Max.            |      |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Output Transition<br>Time                    | 2.0<br>4.5<br>6.0 |                                |               | 30<br>8<br>7                           | 75<br>15<br>13  |                 | 95<br>19<br>16  |                       | 110<br>22<br>19 | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>Time<br>(CLOCK - CO/ZD) | 2.0<br>4.5<br>6.0 |                                |               | 128<br>32<br>27                        | 245<br>49<br>42 | _               | 305<br>61<br>52 |                       | 370<br>74<br>63 | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>Time<br>(APE - CO/ZD)   | 2.0<br>4.5<br>6.0 |                                | _             | 156<br>39<br>33                        | 300<br>60<br>52 | _               | 380<br>76<br>66 |                       | 450<br>90<br>76 | ns   |

| <sup>†</sup> PLH                     | Propagation Delay<br>Time<br>(CL - CO/ZD)    | 2.0<br>4.5<br>6.0 |                                |               | 124<br>31<br>27                        | 240<br>48<br>41 |                 | 300<br>60<br>51 |                       | 360<br>72<br>61 | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>Time<br>(CI/CE - CO/ZO) | 2.0<br>4.5<br>6.0 |                                |               | 56<br>14<br>12                         | 115<br>23<br>20 |                 | 145<br>29<br>25 |                       | 175<br>35<br>30 | ns   |

| fMAX                                 | Maximum Clock<br>Frequency                   | 2.0<br>4.5<br>6.0 |                                | 4<br>20<br>24 | 8<br>31<br>36                          | _               | 3.2<br>16<br>18 | _               | 2.6<br>13<br>15       | _               | MHz  |

| t <sub>W(H)</sub>                    | Minimum Pulse<br>Width<br>(CLOCK)            | 2.0<br>4.5<br>6.0 |                                |               | 30<br>8<br>7                           | 75<br>15<br>13  |                 | 95<br>19<br>16  |                       | 110<br>22<br>19 | ns   |

| t <sub>W(L)</sub>                    | Minimum Pulse<br>Width<br>(CL, APE)          | 2.0<br>4.5<br>6.0 |                                | -             | 30<br>8<br>7                           | 75<br>15<br>13  | _               | 95<br>19<br>16  |                       | 110<br>22<br>19 | ns   |

| ts                                   | Minimum<br>Set-up Time<br>(SPE - CK)         | 2.0<br>4.5<br>6.0 |                                | _             | 30<br>7<br>6                           | 75<br>15<br>13  | =               | 95<br>19<br>16  |                       | 110<br>22<br>19 | ns   |

| ts                                   | Minimum<br>Set-up Time<br>(CI/CE - CK)       | 2.0<br>4.5<br>6.0 |                                | _             | 56<br>14<br>12                         | 125<br>25<br>21 | _               | 155<br>31<br>26 | _                     | 190<br>38<br>32 | ns   |

| ts                                   | Minimum<br>Set up Time<br>(Jn-CK)            | 2.0<br>4.5<br>6.0 |                                | _             | 30<br>8<br>7                           | 75<br>15<br>13  | _               | 95<br>19<br>16  |                       | 110<br>22<br>19 | ns   |

| t <sub>h</sub>                       | Minimum Hold<br>Time<br>(All inputs)         | 2.0<br>4.5<br>6.0 |                                | _             | _                                      | 5<br>5<br>5     | _               | 5<br>5<br>5     |                       | 5<br>5<br>5     | ns   |

| <sup>t</sup> REM                     | Minimum Removal<br>Time<br>(CL - APE)        | 2.0<br>4.5<br>6.0 |                                | _             | 20<br>5<br>4                           | 75<br>15<br>13  | _               | 95<br>19<br>16  |                       | 110<br>22<br>19 | ns   |

| ts                                   | Minimum Set-up<br>Time<br>(Jn APE)           | 2.0<br>4.5<br>6.0 |                                | _             | 30<br>8<br>7                           | 75<br>15<br>13  | =               | 95<br>19<br>16  |                       | 110<br>22<br>19 | ns   |

| C <sub>IN</sub>                      | Input Capacitance                            |                   | _                              | _             | 5                                      | 10              | _               | 10              |                       | 10              | pF   |

| C <sub>PD</sub> (*)                  | Power Dissipation<br>Capacitance             |                   | M54/74HC40102<br>M54/74HC40103 | _             | 110<br>128                             | _               | _               | =               |                       |                 | pF   |

Note (\*) C<sub>PD</sub> is defined as the value of the IC's internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained by the following equation. I<sub>CC</sub> (Opr.)•C<sub>PD</sub>•V<sub>CC</sub>•f<sub>IN</sub> + I<sub>CC</sub>

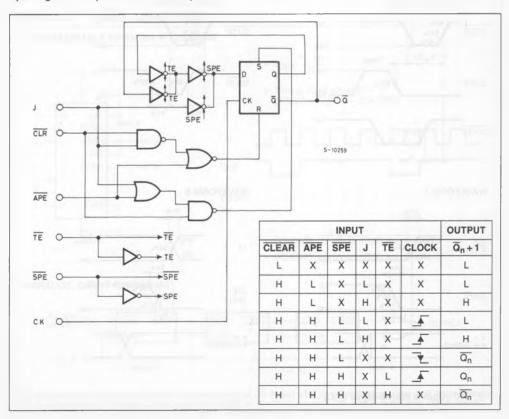

#### **FUNCTIONAL DESCRIPTION**

The HC40102 and HC40103 are 8-stage presettable synchronous down counters. Carry Out/Zero Detect (CO/ZD) is output at the "L" level for the period of 1 bit when the readout becomes "0". The HC40102 adopts binary coded decimal notation, making setting up to 99 counts possible. While the HC40103 adopts 8-bit binary counter and can set up to 255 counts.

#### Count operation

At the "H" level of control input of CLEAR, SPE and APE, the counter carriers out down count operation one by one at the rise of pulse given to CLOCK input. Count operation can be inhibited by setting Carry Input/Clock Enable CI/CE to the "H" level.

CO/ZD is output at the "L" level when the readout becomes "0", but is not output even if the readout becomes "0" when CI/CE is at the "H" level, thus maintaining the "H" level.

Synchronous cascade operation can be carried out by using CI/CE input and CO/ZD output.

The contents of count jump to maximum count (99 for the HC40102 and 225 for the HC40103) if clock is given when the readout is "0". Therefore, operation of 100-frequency division and that of 256-frequency division are carried out for the HC40102 and HC40103, respectively, when clock input alone is given without various kinds of preset operation.

#### Preset operation and reset operation

When Clear (CLEAR) input is set to the "L" level, the readout is set to the maximum count independetly of other inputs. When Asynchronous Preset Enable (APE) input is set to the "L" level, readouts given on J0 to J7 can be preset asynchronously to counter independently of inputs other than CLEAR input. When Synchronous Preset Enable (SPE) is set to the "L" level, the readouts given on J0 to J7 can be preset to counter synchronously with the rise of clock.

As to these operation modes, refer to the truth table.

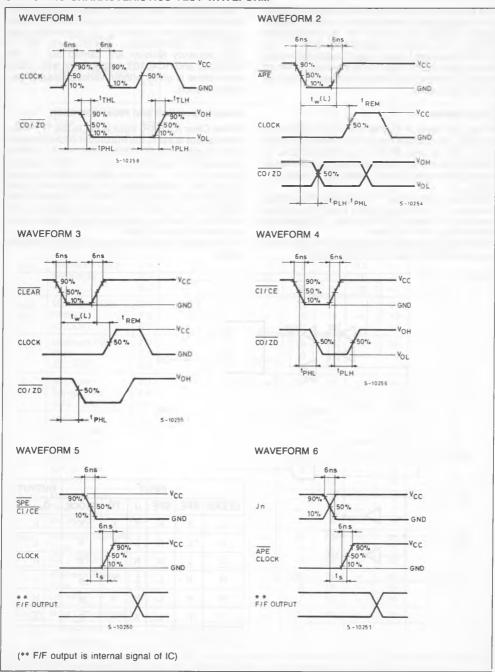

#### SWITCHING CHARACTERISTICS TEST WAVEFORM

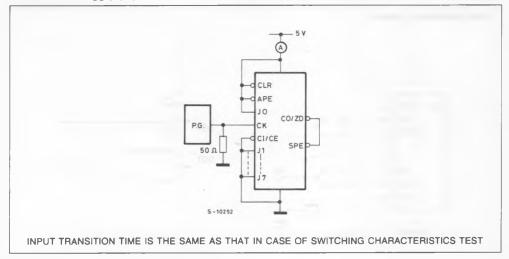

#### TEST CIRCUIT ICC (Opr.)

#### **EXAMPLE OF TYPICAL APPLICATION**

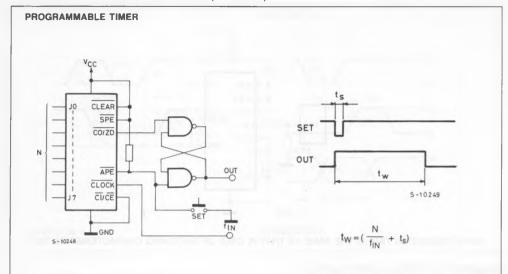

## **EXAMPLE OF TYPICAL APPLICATION (Continued)**

Note: The above formula does not take into account the phase of clock input. Therefore, the real pulse width is the distance between the above formula- $1/f_{\rm IN}$  ~ the above formula.