# intel

# M8251 PROGRAMMABLE COMMUNICATION INTERFACE

#### Synchronous and Asynchronous Operation

- Synchronous: 5-8 Bit Characters Internal or External Character Synchronization Automatic Sync Insertion

- Asynchronous: 5-8 Bit Characters Clock Rate — 1,16 or 64 Times Baud Rate Break Character Generation 1, 1<sup>1</sup>/<sub>2</sub>, or 2 Stop Bits False Start Bit Detection

- Baud Rate DC to 56k Baud (Sync Mode) DC to 8.1k Baud (Async Mode)

- Full Duplex, Double Buffered, Transmitter and Receiver

- Error Detection Parity, Overrun, and Framing

- Fully Compatible with 8080 CPU

- All Inputs and Outputs Are TTL Compatible

- Full Military Temperature Range -55°C to +125°C

- ±10% Power Supply Tolerance

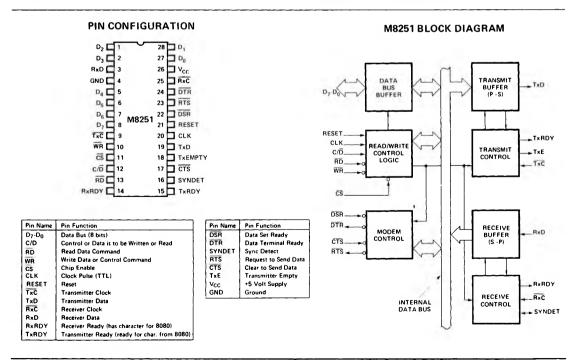

The M8251 is a Universal Synchronous/Asynchronous Receiver/Transmitter (USART) Chip designed for data communications in microcomputer systems. The USART is used as a peripheral device and is programmed by the CPU to operate using virtually any serial data transmission technique presently in use (including IBM Bi-Sync). The USART accepts data characters from the CPU in parallel format and then converts them into a continuous serial data stream for transmission. Simultaneously it can receive serial data streams and convert them into parallel data characters for the CPU. The USART will signal the CPU whenever it can accept a new character for transmission or whenever it has received a character for the CPU. The CPU can read the complete status of the USART at any time. These include data transmission errors and control signals such as SYNDET, TxEMPT. The chip is constructed using N-channel silicon gate technology.

### **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias55°C to +125°C |

|----------------------------------------------|

| Storage Temperature                          |

| Voltage On Any Pin                           |

| With Respect to GND0.5V to +7V               |

| Power Dissipation                            |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **D.C. CHARACTERISTICS**

$T_A = -55^{\circ}C$  to  $+125^{\circ}C$ ;  $V_{CC} = 5.0V \pm 10\%$ ; GND = 0V

| Symbol          | Parameter            | Min. | Тур. | Max.            | Unit     | Test Conditions                        |

|-----------------|----------------------|------|------|-----------------|----------|----------------------------------------|

| VIL             | Input Low Voltage    | 5    |      | 0.8             | v        |                                        |

| VIH             | Input High Voltage   | 2.0  |      | V <sub>CC</sub> | V        |                                        |

| VOL             | Output Low Voltage   |      |      | 0.45            | v        | I <sub>OL</sub> = 1.6mA                |

| Voн             | Output High Voltage  | 2.4  |      |                 | V        | I <sub>OH</sub> = -100μA               |

| I <sub>DL</sub> | Data Bus Leakage     |      |      | -50<br>10       | μΑ<br>μΑ | $V_{OUT} = .45V$<br>$V_{OUT} = V_{CC}$ |

| I <sub>LI</sub> | Input Load Current   |      |      | 10              | μΑ       | V <sub>IN</sub> = 5.5V                 |

| Icc             | Power Supply Current |      | 45   | 80              |          |                                        |

## CAPACITANCE

$T_A \approx 25^{\circ}C; V_{CC} = GND = 0V$

| Symbol           | Parameter         | Min. | Тур. | Max. | Unit | Test Conditions                  |

|------------------|-------------------|------|------|------|------|----------------------------------|

| GN               | Input Capacitance |      |      | 10   | рF   | fc = 1MHz                        |

| C <sub>I/O</sub> | I/O Capacitance   |      |      | 20   | pF   | Unmeasured pins returned to GND. |

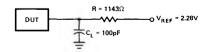

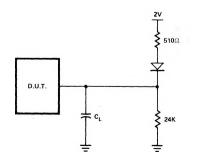

#### **TEST LOAD CIRCUIT:**

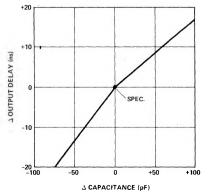

TYPICAL & OUTPUT DELAY VS. & CAPACITANCE (dB)

# A.C. CHARACTERISTICS [2]

| TA | = -55°C to | +125°C; ' | V <sub>CC</sub> = 5.0V | ±10% ; | GND = 0V |

|----|------------|-----------|------------------------|--------|----------|

|----|------------|-----------|------------------------|--------|----------|

| Symbol                         | Parameter                                                            | Min.     | Тур. | Max.      | Unit       | Test Conditions              |

|--------------------------------|----------------------------------------------------------------------|----------|------|-----------|------------|------------------------------|

| t <sub>CY</sub>                | Clock Period                                                         | .420     |      | 1.35      | μs         |                              |

| t <sub>φW</sub>                | Clock Pulse Width                                                    | 220      |      |           | ns         |                              |

| t <sub>R</sub> ,t <sub>F</sub> | Clock Rise and Fall Time                                             | 0        |      | 50        | ns         |                              |

| twR                            | WRITE Pulse Width                                                    | 400      |      |           | ns         |                              |

| t <sub>DS</sub>                | Data Set-Up Time for WRITE                                           | 200      |      |           | ns         |                              |

| t <sub>DH</sub>                | Data Hold Time for WRITE                                             | 40       |      |           | ns         |                              |

| t <sub>AW</sub>                | Address Stable before WRITE                                          | 20       |      |           | ns         |                              |

| twA                            | Address Hold Time for WRITE                                          | 20       |      |           | ns         |                              |

| t <sub>RD</sub>                | READ Pulse Width                                                     | 430      |      |           | ns         |                              |

| t <sub>DD</sub>                | Data Delay from READ                                                 |          |      | 350       | ns         |                              |

| t <sub>DF</sub>                | READ to Data Floating [3]                                            | 25       |      | 200       | ns         | C <sub>L</sub> =15pF to 100p |

| t <sub>AR</sub>                | Address (CE, C/D) Stable before READ                                 | 50       |      |           | ns         |                              |

| t <sub>RA</sub>                | Address (CE, C/D) Hold Time for READ                                 | 5        |      |           | ns         |                              |

| t <sub>DTx</sub>               | TxD Delay from Falling Edge of TxC                                   |          |      | 1         | μs         |                              |

| t <sub>SRx</sub>               | Rx Data Set-Up Time to Sampling Pulse                                | 2        |      |           | μs         |                              |

| t <sub>HRx</sub>               | Rx Data Hold Time to Sampling Pulse                                  | 2        |      |           | μs         |                              |

| f <sub>Tx</sub> [1]            | Transmitter Clock Frequency<br>1X Baud Rate<br>16X and 64X Baud Rate | DC<br>DC |      | 56<br>529 | KHz<br>KHz |                              |

| f <sub>Rx</sub> [1]            | Receiver Clock Frequency<br>1X Baud Rate<br>16X and 64X Baud Rate    | DC<br>DC |      | 56<br>529 | KHz<br>KHz |                              |

| t <sub>Tx</sub>                | TxRDY Delay from Center of Data Bit                                  |          |      | 16        | CLK Period |                              |

| t <sub>Rx</sub>                | RxRDY Delay from Center of Data Bit                                  | 15       |      | 20        | CLK Period |                              |

| t <sub>IS</sub>                | Internal Syndet Delay from Center of Data Bit                        | 20       |      | 25        | CLK Period |                              |

| t <sub>ES</sub>                | External Syndet Set-Up Time before Falling<br>Edge of RxC            |          |      | 16        | CLK Period |                              |

Note 1: The TxC and RxC frequencies have the following limitation with respect to CLK.

For ASYNC Mode,  $t_{T_X}$  or  $t_{R_X} \ge 4.5 t_{CY}$

For SYNC Mode,  $t_{Tx}$  or  $t_{Rx} \ge 30 t_{CY}$

2. AC timings are measured at V<sub>OH</sub> = 2.0V, V<sub>OL</sub> = 0.8V, and load circuit of Figure 1. 3. Float timings are measured at V<sub>OH</sub> = 2.48V, V<sub>OL</sub> = 2.08V

Figure 1. Test Load Circuit.