# M8255A PROGRAMMABLE PERIPHERAL INTERFACE

- 24 Programmable I/O Pins

- Completely TTL Compatible

- Fully Compatible with MCS<sup>™</sup>-80 Microprocessor Family

- Full Military Temperature Range -55°C to +125°C

- Direct Bit Set/Reset Capability Easing Control Application Interface

- 40 Pin Dual In-Line Package

- Reduces System Package Count

- ±10% Power Supply Tolerance

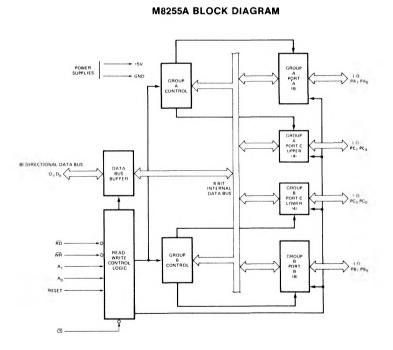

The M8255A is a general purpose programmable I/O device designed for use with microprocessors. It has 24 I/O pins which may be individually programmed in two groups of twelve and used in three major modes of operation. In the first mode (Mode 0), each group of twelve I/O pins may be programmed in sets of 4 to be input or output. In Mode 1, the second mode, each group may be programmed to have 8 lines of input or output. Of the remaining four pins three are used for handshaking and interrupt control signals. The third mode of operation (Mode 2) is a Bi-directional Bus mode which uses 8 lines for a bi-directional bus, and five lines, borrowing one from the other group, for handshaking.

Other features of the M8255A include bit set and reset capability and the ability to source 1 mA of current at 1.5 volts. This allows darlington transistors to be directly driven for applications such as printers and high voltage displays.

## PIN CONFIGURATION

| PA3    | 1  | $\mathbf{O}$ | 40 | PA4               |

|--------|----|--------------|----|-------------------|

| PA2    | 2  |              | 39 | PA5               |

| PAI    | 3  |              | 38 | PA6               |

| PAO    | 4  |              | 37 | PA7               |

| RD     | 5  |              | 36 |                   |

| CS [   | 6  |              | 35 | RESET             |

| GND    | 7  |              | 34 | D Do              |

| A1 [   | 8  |              | 33 | D 01              |

| A0 🗌   | 9  |              | 32 | D2                |

| PC7    | 10 |              | 31 | D D3              |

| PC6    | 11 | M8255A       | 30 | D D4              |

| PC5 [  | 12 |              | 29 | DD5               |

| PC4    | 13 |              | 28 | Do                |

| PC0    | 14 |              | 27 | D Dy              |

| PC1    | 15 |              | 26 | □ <sup>v</sup> cc |

| PC2    | 16 |              | 25 | PB7               |

| PC3    | 17 |              | 24 | PB6               |

| PB0 [. | 18 |              | 23 | PB5               |

| PB1 [  | 19 |              | 22 | ☐ PB4             |

| PB2    | 20 |              | 21 | РВЗ               |

|        |    |              |    |                   |

#### **PIN NAMES**

| D7-D0   | DATA BUS (BI-DIRECTIONAL) |

|---------|---------------------------|

| RESET   | RESET INPUT               |

| CS      | CHIP SELECT               |

| RD      | READ INPUT                |

| WR      | WRITE INPUT               |

| A0, A1  | PORT ADDRESS              |

| PA7-PA0 | PORT A (BIT)              |

| PB7-P80 | PORT B (BIT)              |

| PC7-PC0 | PORT C (BIT)              |

| Vcc     | +5 VOLTS                  |

| GND     | Ø VOLTS                   |

parametric limits are subject to change.

### **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias55°C to +125°C |

|----------------------------------------------|

| Storage Temperature                          |

| Voltage On Any Pin                           |

| With Respect to GND0.5V to +7V               |

| Power Dissipation                            |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **D.C. CHARACTERISTICS** $T_A = -55^{\circ}C$ to $+125^{\circ}C;V_{CC} = +5V \pm 10\%$ ; GND = 0V

| Symbol          | Parameter                | Min. | Тур. | Max. | Unit | Test Conditions                                 |

|-----------------|--------------------------|------|------|------|------|-------------------------------------------------|

| VIL             | Input Low Voltage        | 5    | 1    | .8   | V    |                                                 |

| VIH             | Input High Voltage       | 2.0  |      | Vcc  | v    |                                                 |

| VOL             | Output Low Voltage       |      |      | .45  | v    | I <sub>OL</sub> = 1.7mA                         |

| V <sub>OH</sub> | Output High Voltage      | 2.4  |      | 1    | v    | I <sub>OH</sub> = -50μA (-100μA for D.B. Port)  |

| юн[1]           | Darlington Drive Current | 1.0  |      | 4.0  | mA   | V <sub>OH</sub> = 1.5V, R <sub>EXT</sub> = 750Ω |

| lcc             | Power Supply Current     |      |      | 120  | mA   | (A)                                             |

| հե              | Input Leakage            |      | 1    | 10   | μA   | $V_{IN} = V_{CC}$                               |

| OFL             | Output Float Leakage     |      |      | 10   | μΑ   | $V_{OUT} = 0.45 V/V_{CC}$                       |

NOTE:

1. Available on 8 pins only.

## A.C. CHARACTERISTICS $T_A = -55^{\circ}C$ to $+125^{\circ}C$ , $V_{CC} = +5V \pm 10\%$ ; GND = 0V

| Symbol          | Parameter                                             | Min. | Тур. | Max. | Unit | Test Condition              |

|-----------------|-------------------------------------------------------|------|------|------|------|-----------------------------|

| twp             | Pulse Width of WR                                     |      |      | 400  | ns   |                             |

| tow             | Time D.B. Stable Before WR                            | 50   |      |      | ns   |                             |

| twD             | Time D.B. Stable After WR                             | 35   | ļ    |      | ns   |                             |

| tAW             | Time Address Stable Before WR                         | 20   |      |      | ns   |                             |

| twA             | Time Address Stable After WR                          | 20   |      |      | ns   |                             |

| t <sub>CW</sub> | Time $\overline{CS}$ Stable Before $\overline{WR}$    | 20   |      |      | ns   |                             |

| twc             | Time CS Stable After WR                               | 35   |      |      | ns   |                             |

| t <sub>WB</sub> | Delay From WR To Output                               |      |      | 500  | ns   | C <sub>L</sub> = 50pF       |

| tRP             | Pulse Width of RD                                     | 405  |      |      | ns   |                             |

| t <sub>IR</sub> | RD Set-Up Time                                        | 0    | [    |      | ns   |                             |

| tHR             | Input Hold Time                                       | 0    |      |      | ns   |                             |

| t <sub>RD</sub> | Delay From RD = 0 To System Bus                       |      |      | 295  | ns   | C <sub>L</sub> = 100pF      |

| t <sub>OD</sub> | Delay From $\overline{RD}$ = 1 To System Bus          | 10   |      | 150  | ns   | C <sub>L</sub> = 15pF/100pF |

| t <sub>AR</sub> | Time Address Stable Before RD                         | 50   |      |      | ns   |                             |

| t <sub>CR</sub> | Time CS Stable Before RD                              | 50   |      |      | ns   |                             |

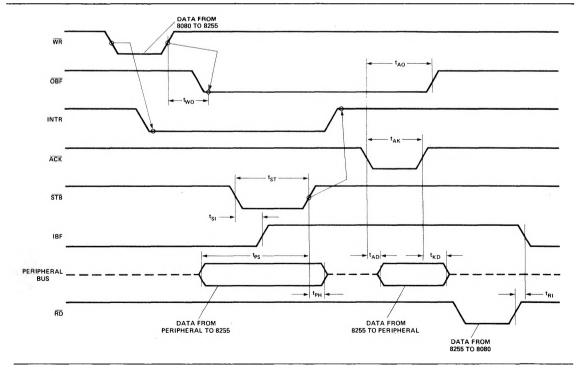

| <sup>t</sup> AK | Width Of ACK Pulse                                    | 500  |      |      | ns   |                             |

| t <sub>ST</sub> | Width Of STB Pulse                                    | 500  |      |      | ns   |                             |

| t <sub>PS</sub> | Set-Up Time For Peripheral                            | 60   |      |      | ns   |                             |

| t <sub>РН</sub> | Hold Time For Peripheral                              | 180  |      |      | ns   |                             |

| t <sub>RA</sub> | Hold Time for $A_1$ , $A_0$ After $\overline{RD}$ = 1 | 0    |      |      | ns   |                             |

|                 | N                                    |    | Nor BA |    |                              |  |

|-----------------|--------------------------------------|----|--------|----|------------------------------|--|

| C. CH           | ARACTERISTICS (Continued)            |    |        |    | Parametric Inis is not a fin |  |

| <sup>t</sup> RC | Hold Time For CS After RD = 1        | 0  |        | ns | subject subjecting           |  |

| t <sub>AD</sub> | Time From ACK = 0 To Output (Mode 2) |    | 400    | ns | CL = 50pF                    |  |

| t <sub>KD</sub> | Time From ACK = 1 To Output Floating | 20 | 300    | ns | C <sub>L</sub> = 15pF/50pF   |  |

| two             | Time From WR = 1 To OBF = 0          |    | 700    | ns | 1                            |  |

| t <sub>AO</sub> | Time From ACK = 0 To OBF = 1         |    | 450    | ns |                              |  |

| t <sub>SI</sub> | Time From STB = 0 To IBF = 1         |    | 450    | ns | - C <sub>L</sub> = 50pF      |  |

| tRI             | Time From RD = 1 To IBF = 0          |    | 360    | ns |                              |  |

۵.

## **CAPACITANCE** $T_A = 25^{\circ}C$ , $V_{CC} = GND = 0V$

| Symbol           | Parameter         | Min. | Тур. | Max. | Unit | Test Conditions                 |

|------------------|-------------------|------|------|------|------|---------------------------------|

| CIN              | Input Capacitance |      |      | 10   | pF   | f <sub>C</sub> = 1MHz           |

| C <sub>I/O</sub> | I/O Capacitance   |      |      | 20   | pF   | Unmeasured pins returned to GND |

#### TEST LOAD CIRCUIT: