8-BIT PARITY TREE

# MC4308F,L\* MC4008F,L,P\*

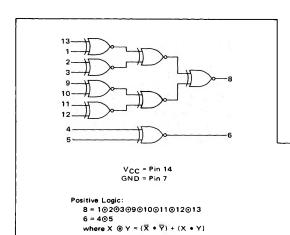

This device consists of seven Exclusive NOR gates connected to check even parity. The output will be in the logic "1" state as long as the "1" state is present on an even number of inputs. The additional Exclusive NOR gate can be used to connect two 8-bit parity trees to form a 16-bit parity tree, or it can be used to convert the parity tree to check odd parity by connecting one gate input to the output of the parity tree and grounding the other input. This conversion can also be accomplished by connecting a simple inverter to the output of the parity tree.

Input Loading Factor = 2

Output Loading Factor = 10

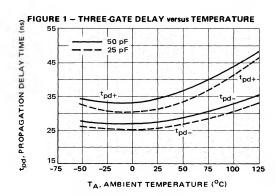

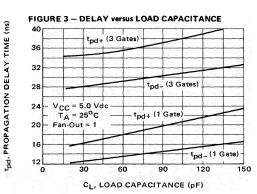

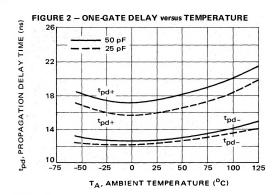

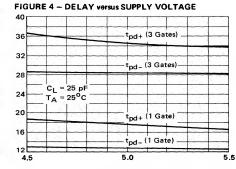

Total Power Dissipation = 150 mW typ/pkg Propagation Delay Time = 15-30 ns typ

### TYPICAL PROPAGATION DELAY TIMES

pd, PROPAGATION DELAY TIME (ns)

VCC, SUPPLY VOLTAGE (VOLTS)

<sup>\*</sup>F suffix = TO-86 ceramic flat package (Case 607).

L suffix = TO-116 ceramic dual in-line package (Case 632).

P suffix = TO-116 plastic dual in-line package (Case 605).

# MC4308F,L, MC4008F,L,P (continued)

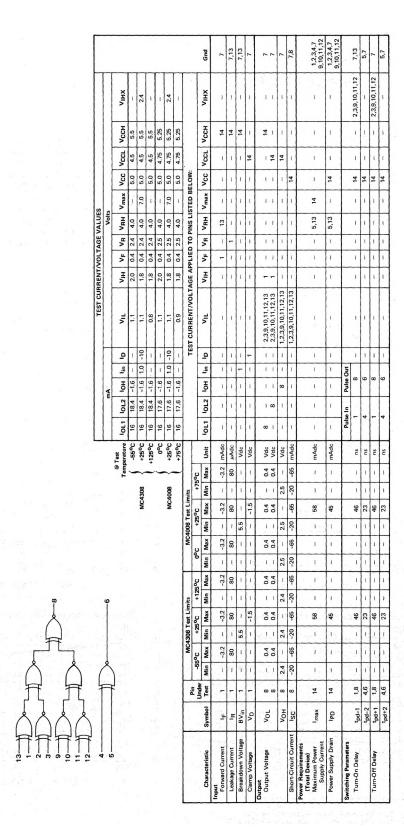

# ELECTRICAL CHARACTERISTICS

Test procedures are shown for only one input and one output. Test other inputs and output in the same manner. To complete testing, test all input-output combinations according to the logic equation.

# INPUT AND OUTPUT LOADING FACTORS with respect to MTTL and MDTL families

|        | MC4308  | MC4308  |

|--------|---------|---------|

|        | INPUT   | OUTPUT  |

|        | LOADING | LOADING |

| FAMILY | FACTOR  | FACTOR  |

| MC4300 | 1.0     | 10      |

| MC500  | 1.2     | 12      |

| MC2100 | 0.8     | 8       |

| MC3100 | 0.8     | 8       |

| MC5400 | 1.0     | 10      |

| MC930  | 1.0*    | 10      |

|        |         |         |

|        | MC4008  | MC4008  |

|--------|---------|---------|

|        | INPUT   | OUTPUT  |

|        | LOADING | LOADING |

| FAMILY | FACTOR  | FACTOR  |

| MC4000 | 1.0     | 10      |

| MC400  | 1.0     | 10      |

| MC2000 | 0.67    | 6       |

| MC3000 | 0.7     | 8       |

| MC7400 | 1.0     | 10      |

| MC830  | 1.15 *  | 12      |

<sup>\*</sup>Applies only when input is being driven by MDTL gate with 2.0 kilohm pullup resistor. Logic "1" state drive limitations of gates with 6.0 kilohm pullup resistors reduce drive capability to fan-out of 3.

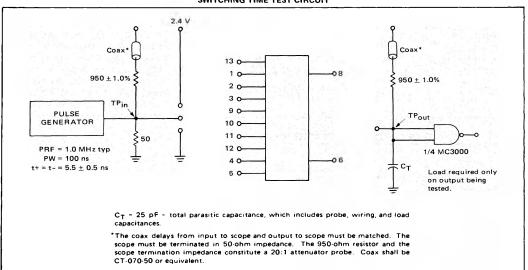

## SWITCHING TIME TEST CIRCUIT

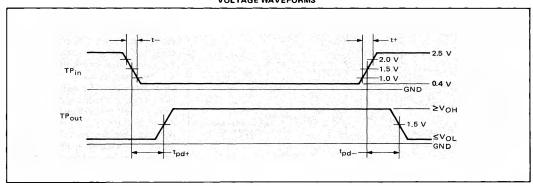

## VOLTAGE WAVEFORMS

APPLICATIONS INFORMATION

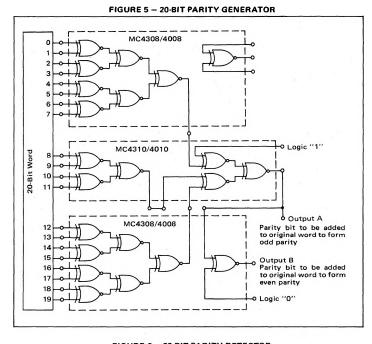

A parity generation tree (simple parity) for a 20-bit word is shown in Figure 5. It uses two MC4308/4008 8-bit parity trees and one MC4310/4010 dual 4-bit parity tree. If a parity word containing odd parity is required (i.e., the 20-bit word plus the parity bit are to contain an odd number of "1's"), the direct output from the parity tree (output A) is used as the parity bit. If even parity is required, the extra Exclusive-NOR gate in one MC4308/4008 provides the inversion when connected as indicated for output B.

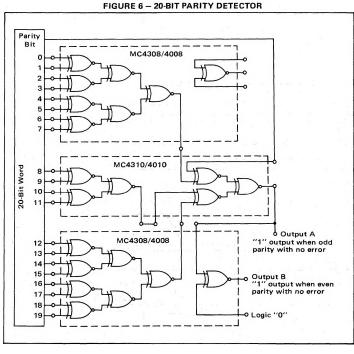

A parity detection circuit for a 20bit word is shown in Figure 6. The 20-bit word is connected to a two-stage parity tree identical to that used for the 20-bit parity generator; however, for the detection circuit the output of the tree must be compared with the input parity bit. The parity bit serves as an input to the second stage of the tree. For odd parity detection, output A will be a logic "1" if no error has occurred. For even parity detection, a logic "1" will appear at output B if no error has been introduced. Longer word lengths can be examined in a similar manner.