#### Freescale Semiconductor

## An Introduction to the MC68331 and MC68332

By Sharon Darley, Mark Maiolani, and Charles Melear

#### 1 INTRODUCTION

Use of microcontrollers (MCUs) presents new challenges as clock speeds increase and bus structures become more complex. In particular, designing a system with Freescale's 32-bit MC68331 or MC68332 can be challenging for those used to the 8-bit world.

The MC68331 and MC68332 are members of the Freescale modular microcontroller family, a series of 16-bit and 32-bit devices constructed from standard on-chip peripheral modules that communicate by means of a standard intermodule bus. The MC68331 is a sophisticated single-chip control system that incorporates a 32-bit CPU module (CPU32), a system integration module (SIM), a queued serial module (QSM), and a general-purpose timer (GPT). The MC68332 is identical except that it has a time processor unit (TPU) instead of a GPT, and it has one additional module: a 2-Kbyte standby RAM (SRAM) with TPU emulation capability. Thus, both the MC68331 and the MC68332 provide a designer with many options, ranging from reset configuration to interrupt generation, that must be considered during the design phase.

This tutorial is intended to assist development and reduce debug time for first-time designers of MC68331 or MC68332 systems. It covers four major topics: designing the hardware, establishing communication, initializing the MCU, and troubleshooting. Each topic is discussed in a separate section that includes practical examples.

The tutorial provides a "hands-on" supplement to the *MC68331 User's Manual* (MC68331UM/AD) and *MC68332 User's Manual* (MC68332UM/AD) which present comprehensive overviews of these MCUs. For more information on device operation, electrical characteristics, registers, and control bit definition, refer to the appropriate sections of the manual. For more detailed information, refer to the reference manual for each of the on-chip peripheral modules. Refer to **6 SOURCES OF INFORMATION** for a complete list of MC68331 and MC68332 technical literature.

The software examples included in the tutorial and a sample system schematic are available through Freeware Data Systems. The files are in the mcu332 directory in an archived file called 331\_2ini.zip. See **6.2**Freeware Data Systems for the phone number for modem access and addresses for internet access.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

## Freesable Semionneways, Inc.

| Sect | ion | Pa                                          | age |

|------|-----|---------------------------------------------|-----|

| 1    |     | INTRODUCTION                                | 1   |

| 2    |     | DESIGNING THE HARDWARE                      | 3   |

| 2.   | 1   | Using Data Bus Pins to Configure the MCU    | 3   |

| 2.   | 2   | Choosing Memory Width                       |     |

| 2.   | 3   | Pins that Need Pull-Up Resistors            |     |

| 2.   | -   | Using Sockets                               | 6   |

| 2.   | 5   | Clock Circuitry                             |     |

| 2.   | -   | Getting Out of Reset                        |     |

| 2.   | -   | Power Supply                                |     |

| 2.   | -   | Designing for Electromagnetic Compatibility |     |

| 2.   | -   | Connecting Memory and Peripherals           |     |

|      | 10  | Using External Interrupts                   |     |

| 3    |     | ESTABLISHING COMMUNICATION                  | 26  |

| 3.   | -   | Communicating with the Target Board         |     |

| 3.   | 2   | Communicating with Freescale Boards         | 28  |

| 4    |     | SYSTEM INITIALIZATION                       | 31  |

| 4.   | 1   | Configuring the Central Processing Unit     | 31  |

| 4.   | 2   | Configuring the System Integration Module   | 33  |

| 4.   | -   | Configuring Internal RAM                    |     |

| 4.   | -   | Configuring The Queued Serial Module        | 37  |

| 4.   | -   | Configuring the General-Purpose Timer       | 40  |

| 4.   | 6   | Configuring the Time Processor Unit         | 43  |

| 5    |     | TROUBLESHOOTING                             | 48  |

| 5.   | •   | Critical Signals to Check                   |     |

| 5.   | 2   | Common Problems and Solutions               | 48  |

| 6    |     | SOURCES OF INFORMATION                      | 52  |

| 6.   | 1   | Technical Literature                        | 52  |

| 6.   | 2   | Freeware Data Systems                       | 54  |

| 6.   | 3   | Other Sources                               | 54  |

# **Freescale Semiconductor, Inc.**2 DESIGNING THE HARDWARE

### 2.1 Using Data Bus Pins to Configure the MCU

The logic level of the data bus pins during reset determines many important operating characteristics of the MCU. Ensuring that the data bus is in a known condition during reset is vital to proper operation because the state of each data bus pin is sampled on the rising edge of the  $\overline{RESET}$  signal. The data bus pins have weak internal pull-up circuitry that should cause them to default to a logic one if left floating (the pull-up current is 15 to 120  $\mu$ A). However, since it is possible for external bus loading to overcome these internal pull-ups, it is a good idea to drive data bus pins that are critical to successful operation of the application to a known condition during reset and for at least five ns afterwards (there is a five ns hold time requirement after the release of  $\overline{RESET}$  for a data bus pin to be recognized at a particular logic level). **Table 1** shows how each data bus pin affects the system configuration.

**Table 1 Reset Mode Selection**

| Mode Select Pin    | Default Function (Pin Left High)   | Alternate Function (Pin Pulled Low) |

|--------------------|------------------------------------|-------------------------------------|

| DATA0              | CSBOOT is 16-bit port              | CSBOOT is 8-bit port                |

|                    | <del>CS0</del>                     | BR                                  |

| DATA1              | CS1                                | BG                                  |

|                    | CS2                                | BGACK                               |

|                    | CS3                                | FC0                                 |

| DATA2              | CS4                                | FC1                                 |

|                    | CS5                                | FC2                                 |

| DATA3 <sup>1</sup> | CS6                                | ADDR19                              |

| DATA4              | <u>CS[7:6]</u>                     | ADDR[20:19]                         |

| DATA5              | <u>CS[8:6]</u>                     | ADDR[21:19]                         |

| DATA6              | <u>CS[9:6]</u>                     | ADDR[22:19]                         |

| DATA7              | CS[10:6]                           | ADDR[23:19]                         |

| DATA8              | DSACKO, DSACK1, AVEC, DS, AS, SIZE | PORTE I/O pins                      |

| DATA9              | ĪRQ[7:1], MODCLK                   | PORTF I/O pins                      |

| DATA11             | Slave Mode Disabled <sup>2</sup>   | Slave Mode Enabled <sup>2</sup>     |

| MODCLK             | VCO = System Clock                 | EXTAL = System Clock                |

| BKPT               | Background Mode Disabled           | Background Mode Enabled             |

#### Notes:

- 1. Only one data bus pin in this group needs to be driven low to select the alternate function for any of the affected pins. For example, to select ADDR[21:19] instead of CS[7:6], drive DATA5 low at the release of reset, and pull DATA3, DATA4, DATA6, and DATA7 high.

- 2. Slave mode is not a supported mode; it is used for factory testing. The slave mode must not be used in a customer application.

As an example, **Table 1** shows that the state of data bus pin 0 (DATA0) during reset determines whether  $\overline{\text{CSBOOT}}$  operates as a 16-bit chip-select or as an 8-bit chip-select. Likewise, data bus pin 1 (DATA1) determines whether the  $\overline{\text{CS0/BR}}$ ,  $\overline{\text{CS1/BG}}$ , and  $\overline{\text{CS2/BGACK}}$  pins function as chip-select lines or as bus control signals. After reset, software can make other selections for these pins by writing to a pin assignment register.

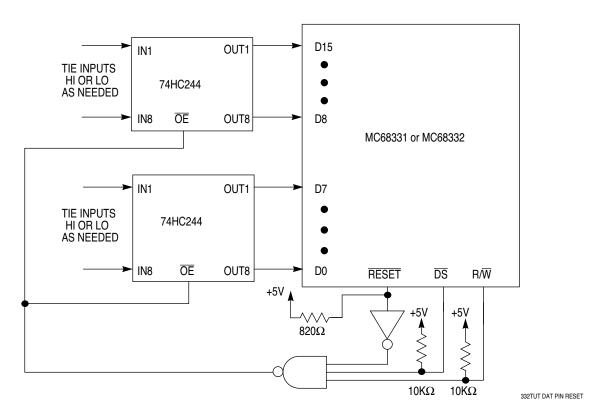

A simple method of pulling a data bus pin high is to connect a 10 K $\Omega$  resistor between it and the five volt supply. Although putting a resistor on a data bus pin degrades performance at higher frequencies, many designers use resistive pull-ups without significant side effects. The preferred method of driving data bus pins during reset is by means of an active driver. A circuit to perform this function is shown in **Figure 1**. This circuit uses a 3-state buffer, such as a 74HC244 non-inverting octal driver, and meets the five ns hold time requirement. While this method does require external circuitry, it is recommended when high levels of noise may be encountered or when high reliability of operation is an overriding concern.

Fie 74HC244 inputs high or low, respectively, so that the desired logical values will be driven to the individual data bus pins when the output enable  $(\overline{OE})$  pin is driven low. The  $\overline{OE}$  will be driven low when the following three conditions are met:  $\overline{RESET}$  is low, data strobe  $(\overline{DS})$  is high, and read/write  $(R/\overline{W})$  is high. Conditioning  $\overline{RESET}$  with  $R/\overline{W}$  and  $\overline{DS}$  ensures that writes to external memory will be completed before the 74HC244s are enabled. Otherwise, if an external  $\overline{RESET}$  signal was applied during a write to external memory and was not conditioned with  $R/\overline{W}$  and  $\overline{DS}$ , the 74HC244s would turn on during the write and cause data bus contention.

Figure 1 Circuitry to Drive Data Bus Pins During RESET Assertion

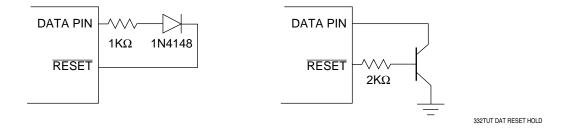

There are several alternative methods of driving data bus pins low during reset. The easiest methods are to connect a resistor in series with a diode from the data bus pin to the RESET line or to connect a transistor, as shown in **Figure 2**. When using a bipolar transistor, a base current limiting resistor is required. When using field effect transistor, a base limiting resistor is not needed. However, the best method is to use the configuration shown in **Figure 1**.

Figure 2 Alternate Methods of Conditioning Data Bus Pins

#### 2.2 Choosing Memory Width

One decision that must be made early in the design is the width of memory to be used. Systems with 8-bit wide memory, 16-bit wide memory or a combination of the two can be implemented using only the onboard chip-select lines.

Using 8-bit memory simplifies the design and reduces cost, but with a significant performance penalty. This penalty is not fixed, but depends on the amount of time that the processor spends accessing the 8-bit memory as opposed to accessing other external memory or performing internal accesses or operations. Moving from 16-bit to 8-bit program memory may reduce CPU performance by 40% when executing simple CPU instructions that only take a few clock cycles to execute. The impact is less in systems that make intensive use of CPU registers and complex instructions.

#### As a general guide:

- Use fast/word memory for the CPU stack, especially when programming in high level languages.

- Use fast/word memory for frequently accessed variables.

- Use fast/word memory for time critical routines, perhaps by copying them from slow main ROM into fast external or internal RAM.

- Use slow/byte memory for rarely executed, non-critical routines, such as initialization routines.

#### 2.3 Pins that Need Pull-Up Resistors

Many of the input pins need pull-up resistors to prevent unexpected conditions. The pins discussed below must be conditioned in all applications. An incorrect voltage on one or more of them can cause general system failure. Other input pins, such as GPT or TPU inputs, can be left floating without adverse effect in certain applications. The designer must determine which pins can cause system failure in a particular application and deal with them appropriately. In general, it is best to condition all input pins so that they are in a known state, whether they are used or not.

Never connect a pin directly to five volts if it is possible to configure the pin as an output. Attempting to drive an output low when it is connected to voltage source can damage the output drivers. Many of the pins have dual functions and can be configured as I/O pins by holding specific data bus lines low during reset. When a pin is configured for I/O during reset and will never be reconfigured for the alternate function, a pull-up resistor may not be needed. **Table 1** shows which signals are affected by data bus pin state during reset.

**BR/CS0** — Use a 10 K $\Omega$  pull-up to prevent an unexpected bus request. This pin is configured as a chip-select pin when DATA1 is held high at the release of reset. Conditioning DATA1 as described in **2.1 Using Data Bus Pins to Configure the MCU** precludes use of a pull-up.

**BERR** — This is an input signal that is asserted in the absence of  $\overline{DSACK}$  to indicate a bus error condition. Using a 10 K $\Omega$  pull-up resistor prevents the unexpected assertion of bus error.

$\overline{\text{HALT}}$  — This is an active-low bidirectional signal that can be used to halt the external bus, among other things. Using a 10 KΩ pull-up resistor will prevent an erroneous bus halt. Since  $\overline{\text{HALT}}$  is a bidirectional signal, do not connect it directly to  $\overline{\text{BERR}}$ ,  $\overline{\text{RESET}}$  or five volts.

**IRQ[7:1]** — Although the interrupt lines have internal pull-up circuitry, the circuitry is weak and can be overcome by noise and capacitive coupling. Make certain that pins configured for use as interrupt-request inputs rather than for use as general-purpose I/O are pulled up to five volts.

There are two ways to lessen the chances for erroneous interrupt service requests:

1. Hold DATA9 low during reset as described in 2.1 Using Data Bus Pins to Configure the MCU to assign these pins to general-purpose I/O port F. Pull up lines that are to be used for interrupt service to five volts via 10 KΩ resistors, hold DATA9 low during reset, reassign the pins to be used for interrupt requests by writing to the port F pin assignment register, then change the IPL mask value to enable maskable interrupts.

2. Hold DATA9 high during reset as described in **2.1 Using Data Bus Pins to Configure the MCU** to assign all these pins to use as interrupt-request inputs. Pull up all lines that are to be used for interrupt service, including  $\overline{IRQ7}$ , to five volts via 10 K $\Omega$  resistors, hold DATA9 high during reset, reassign the pins that are not used for interrupt requests by writing to the port F pin assignment register, then change the IPL mask value to enable maskable interrupts.

Remember that the level seven interrupt is non-maskable — when configured as an interrupt line,  $\overline{IRQ7}$  is always enabled. The only way to disable external  $\overline{IRQ7}$  interrupts is to assign the  $\overline{IRQ7}$  pin to I/O function via the port F pin assignment register.

**DSACK[1:0]** — During bus transfers, external devices can drive these signals to indicate port width. These signals are active even if the bus transfer is to or from a peripheral that is using one of the chipselects to terminate the bus cycle. Putting 10 KΩ pull-ups on these two pins prevents accidental assertion of  $\overline{DSACK[1:0]}$ , which can occur if the pins are left floating.

$\overline{\text{AVEC}}$  — If this signal is asserted during an interrupt acknowledge cycle, an autovector will be used for the external interrupt being serviced. If the  $\overline{\text{AVEC}}$  pin is connected permanently to ground, all external interrupts will autovector. Using a 10 K $\Omega$  pull-up resistor will prevent unexpected assertion of the  $\overline{\text{AVEC}}$  pin.

**TSTME/TSC** — The inactive state of this pin is five volts. Pulling it low enables special test mode, but the MCU cannot enter test mode unless the state of a bit in one of the test mode registers is changed by the software. Although this should happen only if the software is corrupted, to prevent entering special test mode, put a 10 KΩ pull-up resistor on this pin. Special test mode is generally used only for factory testing, although there are certain circumstances, such as debugging TPU microcode, in which a limited subset of test mode capabilities are available to users. Driving this pin to approximately 1.6 times  $V_{DD}$  causes the MCU to place all output drivers in a high-impedance state, isolating the MCU from the rest of the system.

**BKPT/DSCLK** — Background debug mode (BDM) operation is enabled when  $\overline{\text{BKPT}}$  is asserted at the rising edge of the  $\overline{\text{RESET}}$  signal. BDM remains enabled until the next system reset. If  $\overline{\text{BKPT}}$  is at a logic level one on the trailing edge of  $\overline{\text{RESET}}$ , BDM is disabled.  $\overline{\text{BKPT}}$  is re-latched on each rising transition of  $\overline{\text{RESET}}$ . A 4.7 KΩ pull-up resistor will ensure that BDM is not unexpectedly enabled upon reset.

$R/\overline{W}$  — Putting a 10 K $\Omega$  pull-up resistor on this pin will prevent accidental writes to memory while the device is being powered up. Normally,  $R/\overline{W}$  is always defined. However, when power is first applied to the device,  $R/\overline{W}$  can be undefined for a few cycles. This may cause a problem for EEPROM or battery backed up RAM.

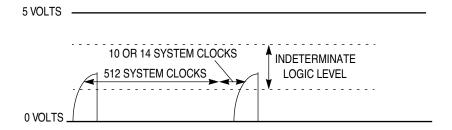

**RESET** — An 820  $\Omega$  pull-up resistor is required for this pin. Do not put capacitors on the  $\overline{\text{RESET}}$  pin. The reason for such a strong pull-up and no extra capacitance is that the  $\overline{\text{RESET}}$  line must rise to a logic one within approximately ten system clocks after the MCU has driven  $\overline{\text{RESET}}$  low for 512 clocks, or else the MCU must re-assert the  $\overline{\text{RESET}}$  line for an additional 512 clock cycles.

**MODCLK** — If using the internal PLL to generate the system clock, this pin must be pulled up with a 10  $K\Omega$  resistor or driven high during reset. If using an external clock source and bypassing the PLL, connect this pin to ground or drive it low during reset.

### 2.4 Using Sockets

Because of the high pin count the MCU package has a very narrow lead pitch, which makes it nearly impossible to hand-solder onto a board. This is not a problem for design activities that can manufacture PC boards, but designers who are assembling a limited number of prototypes or who cannot manufacture PC boards will probably need to use a socket to hold the chip. The wider spacing of socket pins makes it possible to connect the socket to a board.

Sockets are not a place to economize. Use a good quality socket that firmly holds the MCU in place so that all pins maintain contact. If the MCU is likely to be removed and replaced, consider using a zero insertion force socket.

Three socket manufacturers are:

**3M** — (800) 328-0411, **AMP** — (800) 522-6752, and **Yamaichi** — (408) 452-0797.

#### 2.5 Clock Circuitry

The designer must decide whether to use the internal frequency synthesizer circuit or an external clock to produce the system clock signal. Both options are discussed in the following paragraphs.

#### 2.5.1 Using the Internal Frequency Synthesizer Circuit

The MCU uses a voltage-controlled oscillator (VCO) and a phase-locked loop (PLL) to generate an internal high speed clock. This arrangement permits low power operation using only the low frequency oscillator. Low frequency in CMOS technology translates into low power because power consumption is proportional to frequency.

The internal frequency synthesizer circuit is enabled when the MODLCK pin is pulled high during reset. The synthesizer requires a reference frequency in order to operate. There are two reference frequency options: a crystal oscillator circuit or an external clock reference, such as a canned oscillator circuit (a single package which contains the crystal and buffer circuit) as the input.

#### 2.5.2 Using a Crystal Oscillator Circuit

#### 2.5.2.1 Oscillator Components

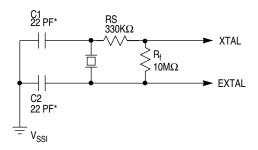

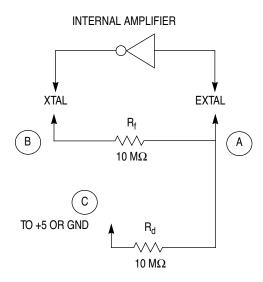

The crystal oscillator used is a Pierce oscillator, also known as a parallel resonant crystal oscillator. It is shown in **Figure 3**. Its components consist of a series resistor, a feedback resistor, a crystal, an inverter, and two capacitors:

Rs — Series resistor Rs must be large enough to appropriately limit current to the crystal and yet small enough to provide enough current to start oscillation quickly. The smaller Rs, the faster the oscillator will start. However, if Rs is too small, the crystal will start up in unpredictable modes or dissipate too much power. This can cause heating problems. In extreme cases, the crystal may even be damaged and not work properly again. If Rs is too large, the oscillator will start very slowly or not at all. The best way to minimize start-up time is to minimize the size of Rs within the guidelines of the maximum power dissipation.

The crystal manufacturer generally recommends a range of values to use. To ensure that Rs is large enough to prevent the crystal from being overdriven, observe the output frequency as a function of  $V_{DD}$  on the CLKOUT pin. If the crystal is overdriven at start-up, i.e., the first 500 ms or so after the power is turned on, the frequency will be very unstable.

**Rf** — Feedback resistor Rf is used to bias the inverter between EXTAL and XTAL inside the MCU. Rf affects the loop gain; lower values reduce gain, while higher values increase gain.

C1 and C2 — The series combination of C1 and C2 provides the parallel load for the crystal. Their values may be varied to trim frequency. In high frequency applications, C1 and C2 are usually equal. However, in low frequency applications, C1 can be smaller than C2 (about 5 pF) to provide a higher voltage at the EXTAL input. A wider voltage swing at this input will result in lower power-supply current. Usually, the actual capacitances will be smaller than the intended capacitances since circuit and layout capacitances add to the values of C1 and C2.

**Inverter** — The inverter is inside the MCU. It provides the 180 degree phase shift necessary for oscillation.

**Crystal** — The crystal is made of piezoelectric quartz. It must be a good quality crystal that is capable of suppressing harmonics and overtones and quickly locking onto the fundamental frequency. If a particular crystal type or brand is prone to starting with overtones or harmonics, don't use it. No amount of circuit design can compensate for a bad or poor quality crystal.

The MCU is designed to use a 32.768 kHz AT-cut crystal to produce an 8.389 MHz CLKOUT signal. The frequency of the internal clock can be increased or decreased by writing to the SYNCR register. **Figure 3** shows clock circuitry for a Daishinku DMX-38 32.768 kHz crystal, but the circuit will work for most other 32.768 kHz crystals also. To use other crystal values (the allowable range is 20 kHz–50 kHz), consult the crystal vendor for analysis of the crystal components needed.

#### NOTE

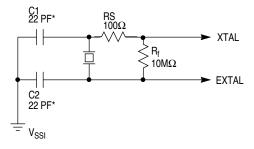

Some older versions of the MC68331 and MC68332 require different components. The MC68331 mask set that requires different components is OC47T. The MC68332 mask sets that require different components are 1C17P, 1C32J, OC53T, and 1C53T. See **Figure 4** for an illustration.

<sup>\*</sup> RESISTANCE AND CAPACITANCE BASED ON A TEST CIRCUIT CONSTRUCTED WITH A DAISHINKU DMX-38 32.768-KHZ CRYSTAL. SPECIFIC COMPONENTS MUST BE BASED ON CRYSTAL TYPE. CONTACT CRYSTAL VENDOR FOR EXACT CIRCUIT.

332TUT XTAL CONN 1

Figure 3 System Clock with a 32.768 kHz Reference Crystal

<sup>\*</sup> RESISTANCE AND CAPACITANCE BASED ON A TEST CIRCUIT CONSTRUCTED WITH A DAISHINKU DMX-38 32.768-KHZ CRYSTAL. SPECIFIC COMPONENTS MUST BE BASED ON CRYSTAL TYPE. CONTACT CRYSTAL VENDOR FOR EXACT CIRCUIT.

Figure 4 Oscillator Circuit for Some Older Mask Sets

For the most accurate oscillator frequency, use the Pierce version of the crystal (rather than the series resonant version) with C1 and C2 values to match the specified load capacitance of the crystal. As a side note, start-up time is inversely proportional to frequency. A 32 kHz crystal may take several hundred milliseconds to start up. Be aware: all crystals are not created equal nor are they close. In fact, there are several different types of tuning elements that can be used for low frequency oscillators in the range of 32.768 kHz. While there are many characteristics of the various tuning elements that can be precisely measured, there are other characteristics that are extremely difficult to measure and express in a useful way.

Maximum power dissipation of a crystal is generally specified by the manufacturer of the device. Crystal power dissipation is a function of the reactance of the combined input and output capacitance of the internal amplifier of the microcontroller and of the external circuit components including the crystal itself. The manufacturer specifies this value and also specifies a circuit, usually one like that of **Figure 3**, along with the

circuit values. The crystal manufacturer makes a tacit assumption that the amplifier has enough drive capability to handle the required load, so that the output voltage levels of the amplifier are not affected.

Parameters related to suppression of harmonics and overtones are generally not specified by the crystal manufacturer. Harmonics are integer multiples of the fundamental frequency. The first overtone is approximately 1.7 times the fundamental frequency. Since a typical oscillator circuit forms a low pass filter, the three db roll-off point should be set at about 1.5 times the fundamental frequency of the crystal. This should cause no attenuation at the fundamental but should cause significant attenuation at the first overtone and even greater attenuation at the first harmonic. When figuring the reactance of the entire circuit, it is most important to use the typical parameters of the crystal, the input and output capacitance of the amplifier and the remainder of the external components in the calculation.

Many companies make crystals. Most re-sell their products through electronics distributors that are listed in the *EITD Electronic Industry Telephone Directory*. Refer to **6 SOURCES OF INFORMATION** for ordering information.

Four crystal manufacturers are:

ECS — (800) 237-1041

The part number for a surface mount 32.768 kHz crystal with a temperature range of –40 to +85 degrees Celsius is ECX205. This crystal also comes in other packages.

Fox — (813) 693-0099

The part number for a surface mount 32.768 kHz crystal with a temperature range of –40 to +85 degrees Celsius is FSM327. This crystal also comes in other packages.

**KDS (Daishinku)** — (913) 491-6825

The part number for a surface mount 32.768 kHz crystal with a temperature range of –40 to +85 degrees Celsius is DMX-38. This crystal comes in other packages.

Statek — (714) 639-7810

The part number for a surface mount 32.768 kHz crystal that can be used at 25 degrees Celsius is CX-1VS-SMI 32.768 kHz. For a temperature range of –40 to 85 degrees Celsius, the part number is CX-1VS-SMI 32.768 kHz A/I.

#### 2.5.2.2 Grit and Grime

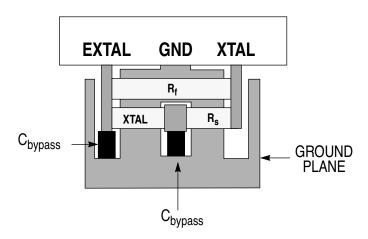

Oscillators are quite sensitive to dirt, solder flux, grease, condensation due to high humidity, and other conducting materials on the circuit board. These materials can allow a very high resistance leakage path from one of the amplifier pins to either ground or the positive terminal of the power supply. When the oscillator has power applied but has not started, the crystal and bypass capacitors appear as DC open circuits. An oscillator in a DC condition would appear as shown in **Figure 5**.

The resistor, Rd, represents a high resistance leakage path, somewhere in the range of five to  $20~M\Omega$ . The feedback resistor, Rf, is also in this range. Assuming that Rd and Rf are both  $10~M\Omega$ , the voltage at point A is half the voltage difference between points B and C. Thus, if the XTAL pin is at a logic one (4.5 volts) and point C is at ground, the voltage at point A (EXTAL pin) will be 2.25 volts. If point B is at a logic zero (0.5 volts) and point C is at ground, the voltage at point A is 0.25 volts. Thus, the voltage at point A may be interpreted as a logic zero regardless of whether the XTAL pin is a logic one or a logic zero. This depends on the threshold of the inverter whose input is connected to point A. Likewise, if point C is connected to five volts, point A may be interpreted as a logic one regardless of the state of the XTAL pin. A circuit with this problem will not oscillate.

The only way to diagnose this problem is to remove the external circuit components as well as the MCU from the board and use an Ohm meter to check the resistance from points A and B to ground and five volts. Anything other than a completely open circuit is a sign of trouble. The obvious solution is to clean the printed

circuit board. If the dirt or grime that form the high resistance path is on an inner layer of the printed circuit board, the board is unusable. If the leakage is due to condensation on the board, then spray the oscillator circuit with a protective epoxy.

332TUT XTAL RF/RD CONN

Figure 5 DC Model of Oscillator Circuit

#### 2.5.2.3 Layout and Strange Behavior

Oscillator layout is just as important as a good quality crystal and cleanliness in manufacturing the printed circuit board. The best possible solution is to use a multi-layer board with a separate ground plane. The rules for oscillator layout are quite simple. First, locate the crystal and all associated external components as close to the oscillator pins as possible. Second, do not under any circumstance run a high frequency trace under either the feedback or series resistor or the crystal. Third, if there is no separate ground plane, make sure that the ground for the bypass capacitors is connected to a solid ground trace. **Figure 6** shows typical one-layer oscillator layout.

Figure 6 Typical One-Layer Oscillator Layout

332TUT XTAL PCB LAYOUT

Do not run high frequency conductors near, and particularly underneath, the crystal, the feedback resistor or the series resistor. In **Figure 6**, only a ground trace runs underneath these components. Also note that, in **Figure 6**, the ground trace is tied to the ground pin nearest to the oscillator pins. This helps prevent large loop currents in the vicinity of the crystal. It is also very important to tie the ground pin to the most solid ground in the system. The trace that connects the oscillator and the ground plane should not connect to any other circuit element as the injection of current into this trace tends to make the oscillator unstable.

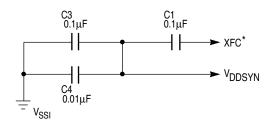

#### 2.5.2.4 XFC and V<sub>DDSYN</sub>

Noise on the XFC,  $V_{DDSYN}$ , and  $V_{SSI}$  pins causes frequency shifts in CLKOUT. The XFC filter capacitor and the  $V_{DDSYN}$  bypass capacitors should be kept as close to the XFC and  $V_{DDSYN}$  pins as possible with no digital logic coupling to either XFC or  $V_{DDSYN}$ . The ground for the  $V_{DDSYN}$  bypass capacitors should be tied directly to the  $V_{SSI}$  ground plane. If possible, route  $V_{DDSYN}$  and  $V_{SSI}$  as separate supply runs or planes.  $V_{DDSYN}$  may require an inductive or resistive filter to control supply noise.

A  $V_{DDSYN}$  resistive filter would consist of a 100 to 500  $\Omega$  resistor from  $V_{DD}$  to  $V_{DDSYN}$  and a 0.1- $\mu$ F bypass capacitor from  $V_{DDSYN}$  to  $V_{SSI}$ . The proper values for the resistor and capacitor can be determined by examining the frequency of the  $V_{DDSYN}$  noise. The RC time constant needs to be large enough to filter the supply noise. An inductive filter would replace the resistor with an inductor.

The low-pass filter requires an external low-leakage capacitor, typically 0.1  $\mu$ F with an insulation resistance specification as high as practical. The main criterion is that the capacitor be low-leakage because leakage affects frequency stability and accuracy. Do not use a tantalum capacitor. Although the *SIM Reference Manual* (SIMRM/AD) recommends an insulation resistance of 30,000 M $\Omega$ , this value may not be necessary in all applications. For most consumer (room temperature) applications, polystyrene capacitors are recommended. See **Figure 7** for a recommended circuit.

#### **NOTE**

Some published errata sheets and user's manuals recommend a filter circuit that includes an 18  $k\Omega$  resistor for a high stability operating environment. Subsequent investigation has shown that, when this circuit is used, if there is leakage (about 50  $k\Omega$ ) between the XFC pin and the power supply, the MCU may not come out of reset because the internal VCO lock detect circuitry does not operate properly. Use the circuit shown in **Figure 7** instead.

<sup>\*</sup> MAINTAIN LOW LEAKAGE ON THE XFC NODE

332TUT XFC CONN

Figure 7 Conditioning the XFC and V<sub>DDSYN</sub> Pins

#### 2.5.2.5 Evaluating Oscillator Performance

Once an entire oscillator circuit is built, it is very important to evaluate circuit characteristics. Of particular interest is how the oscillator starts. If the oscillator starts in a metastable state that persists for several hundred milliseconds, it is quite possible that this state will persist until the MCU releases reset and tries to start fetching instructions. When this happens, the PLL may well be operating at a frequency far greater than the

naximum specified for the MCU. Any variation in the input frequency of the PLL is multiplied by the feed-back ratio of the PLL. If the MCU starts operating, i.e., reset is released and the internal clocks are gated to the internal buses, while the oscillator is operating at an overtone or first harmonic, the MCU will probably enter an inoperative state in which it cannot be restarted by a hardware reset. In this case, the only option is to turn the system power off and then attempt a power-on reset.

Because oscillators are very sensitive circuits, malfunctions are difficult to diagnose by conventional means such as probing the input and output with an oscilloscope. The capacitance of a scope probe can be large compared to the effective capacitance of the particular node of the oscillator that is probed. This added capacitance can cause an errant oscillator to move to a more stable region where it appears to work correctly or, on the other hand, a working oscillator could be moved into a region of no oscillation at all. Therefore, it is important to measure oscillator performance indirectly. This can be done through the CLKOUT pin, which is a buffered form of the internal system clock. Monitoring the CLKOUT pin with an oscilloscope does not affect the oscillator and provides an accurate representation of oscillator problems. If the MCU is running off the internal PLL and a 32.768 kHz crystal, the CLKOUT frequency should be 8.389 MHz at the release of reset.

The CLKOUT signal is likely to do one of three things when power is turned on. It will either remain at a constant DC level, jump quickly to the proper frequency, or, first jump to the desired frequency, then enter a very high frequency metastable state and then jump back to the fundamental frequency. With a small amount of practice, these metastable states, which last for approximately 100 to 500 ms, can be easily detected on an oscilloscope. In the third case, the MCU generally takes almost a second to reach steady state, which provides plenty of time for it to attempt operation while the clock is in a metastable state.

#### 2.5.2.6 Using a Canned Oscillator

A second option when using the internal frequency synthesizer circuit is to hold MODCLK high during reset and connect an external clock reference or canned oscillator (a single package that includes the oscillator and required external components) to the EXTAL pin. Leave the XTAL pin floating, but connect the filter circuit shown in **Figure 7** to  $V_{DDSYN}$  and XFC. The allowable frequency range is 20-50 kHz.

One manufacturer of canned oscillators is:

Oak Frequency Control Group — (717) 486-3411

#### 2.5.3 Using an External Clock

To use an external clock, connect a clock signal to the EXTAL pin and hold MODCLK low during reset. Leave the XTAL and XFC pins floating, but connect  $V_{DDSYN}$  to power. The frequency control bits in the SYNCR register have no effect; the signal applied to the EXTAL pin should appear unchanged on the CLK-OUT line. The external clock must comply with the following expression.

$\label{eq:minimum} \mbox{Minimum external clock period} = \frac{\mbox{Minimum external clock high/low time}}{50\% - \mbox{percentage variation of external clock input duty cycle}}$

Minimum external clock high/low time is a specification given in the device electrical characteristics.

#### 2.6 Getting Out of Reset

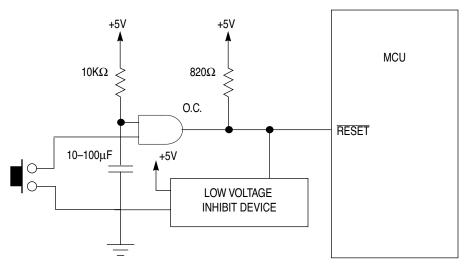

Asserting and releasing the  $\overline{\text{RESET}}$  line was once a relatively simple task. However, as microcontrollers have become more complex, bidirectional reset pins have become standard. Bidirectional reset lines allow an external device to reset the MCU and also allow the MCU to assert reset for associated peripherals. Bidirectional pins must be driven with open collector devices. A typical circuit for driving the MCU  $\overline{\text{RESET}}$  pin is shown in **Figure 8**. The  $\overline{\text{RESET}}$  pin is driven by an open collector device, and it is pulled to a logic one by an 820  $\Omega$  resistor.

332TUT LVI/RESET CONN

**Figure 8 Typical Reset Circuit**

When the internal PLL is used to generate the internal system clock, the RESET pin works as follows. At power-up, the MCU drives RESET low. When the PLL locks, the MCU releases RESET for two system clock cycles. If the external pull-up resistor can pull RESET to a logic one during the two cycles, the MCU assumes that the reset is a power-on reset rather than an external reset. However, if RESET does not rise to a logic one during the two cycles, the MCU assumes that the reset is an external reset and drives RESET to a logic zero for 512 clock cycles. After 512 cycles have elapsed, the MCU releases RESET for ten clock cycles. If RESET is a logic one at the end of the ten cycles, the MCU begins program execution. If RESET is a logic zero at the end of the ten cycles, the MCU once again actively drives RESET low for 512 clock cycles. This cycle repeats until RESET is finally perceived to be at a logic one. Figure 9 shows the waveform that is produced on the RESET line when the pull-up resistor is too large and pull-up current is inadequate.

332TUT RESET LEVEL TIM

Figure 9 RESET Waveform Caused by Weak Pull-Up

If the PLL circuit is not used, and an external clock at the desired frequency of the system clock is applied to EXTAL prior to start-up, the start up sequence is the same except that the MCU recognizes the clock immediately instead of waiting for the PLL to lock.

#### 2.7 Power Supply

Always connect all power and ground pins to power sources. Internal power buses only serve about eight to ten pins each. The power and ground pins are usually not connected together within the device. If any power pin is left floating, the pins served by the floating power pin can receive power from internal circuitry such as internal protection diodes. However, the current path will usually have several diode drops resulting in a low output high voltage (about three volts) on associated output pins.

#### 2.7.1 Low Voltage Inhibit Devices

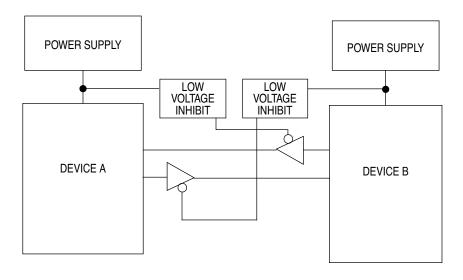

A low voltage inhibit (LVI) device (also referred to as a reset supervisor circuit) protects the MCU by keeping it in reset until full voltage is applied and by forcing an external reset as soon as power starts to fall. This prevents the MCU from going into an indeterminate state due to a power supply failure or slow power supply ramp-up time.

A number of manufacturers make LVI devices that can be used with the MCU. Some are listed below.

**Analog Devices** — (617) 461-3392

LVI part numbers are ADM698 and ADM699. These devices require pull-up resistors.

Dallas Semiconductor — (214) 450-0448

Various reset supervisor circuits. Part numbers DS1233A, D, and M do not require pull-up resistors.

**Linear Technologies** — (408) 432-1900

LVI part numbers are LTC692 and LTC693. These devices require a pull-up resistor.

Maxim — (800) 998-8800 or (408) 737-7600

Various reset supervisor circuits. MAX 690 and MAX 700 series devices require pull-up resistors, but MAX 809 devices do not.

Freescale, **Inc.** — (408) 432-1900

One reset supervisor circuit part number is MC34064. It requires an external pull-up resistor.

#### 2.7.1.1 Using LVI Devices with External Oscillators

An LVI device provides an extra degree of protection when an external oscillator that has an independent power supply is used to generate the system clock. In this case, the LVI device ensures that the oscillator does not power up before the MCU.

#### 2.7.1.2 Using LVI Devices with Multiple Power Supplies

Take special precautions when system components that are connected to each other have separate power supplies. Generally, one power supply will reach operating voltage more quickly than another. A device connected to this fast supply can begin to operate before devices connected to a slower supply have reached operating voltage. If a device connected to a fast supply drives logic one levels to a device connected to a slow supply, the input protection diodes of the slow-starting device can be momentarily forward biased, and significant current can be injected into the device substrate. In the case of an MCU, the injected current can cause internal nodes to be improperly charged or discharged. Since this action is random, it is impossible to predict what will happen when injection occurs. Usually, the processor will fail to fetch opcodes. **Figure 10** shows how to use LVI devices to prevent this problem. Each power supply is monitored by a separate LVI device. Signals from other boards are inhibited until correct operating voltage is applied.

332TUT DUAL RESET CONN

Figure 10 Using LVI Devices with Multiple Power Supplies

#### 2.8 Designing for Electromagnetic Compatibility

Because of the fast clock speed and relatively short rise and fall times of MCU signals, the designer must consider electromagnetic compatibility (EMC) issues. All high-speed digital devices radiate noise, and if FCC compliance is required, the designer must do everything possible to limit emissions from the MCU. Use of a four-layer board is probably the best single option the designer has. Although a two-layer board will work, a multilayer PCB is much more effective at both protecting the MCU from emissions, and reducing emissions from the MCU. EMC compatibility is a complex topic, and this tutorial can present only a brief overview of EMC design techniques.

#### 2.8.1 Reducing Power Supply Noise

The MCU is very susceptible to noise created by large or rapid fluctuations in current through a particular power supply pin. The power supply pins are divided up into  $V_{DDE}/V_{SSE}$  and  $V_{DDI}/V_{SSI}$ . The  $V_{DDE}/V_{SSE}$  pins power the external drivers and pins, while the  $V_{DDI}/V_{SSI}$  pins power the internal peripherals and core of the MCU. It is very important to keep the  $V_{DDI}/V_{SSI}$  pins free of noise, as the CPU is generally more sensitive to power supply noise than the port drivers. When designing a multilayer board, simply route the power and ground pins directly to the power and ground planes; when designing a two-layer board, however, it is best to isolate the power bus that serves the core of the chip from the power bus that serves the port drivers.

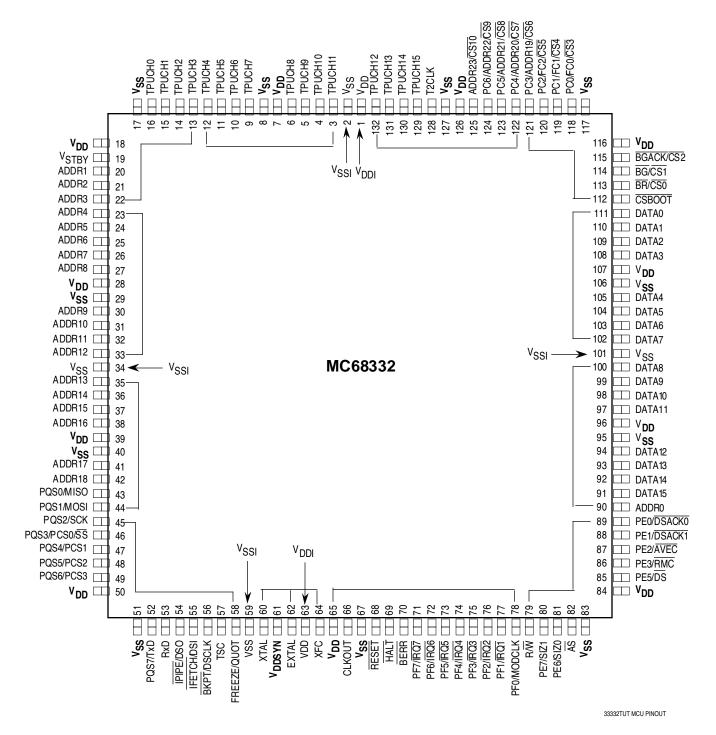

**Figure 11** shows groups of pins on the MC68331/MC68332 that are powered by the same supply pins. Although only the 132-pin plastic surface mount package for the MC68332 is shown, the groups for the 144-pin package are the same. Also, the pinout for the MC68331 is the same as for the MC68332, except that the GPT pins take the place of the TPU pins. In each group, the  $V_{DDE}$  and  $V_{SSE}$  pins that power a particular group are shown in bold face type. The  $V_{DDI}$  and  $V_{SSI}$  pins are labeled as such. EXTAL, XTAL, and XFC are powered only by  $V_{DDSYN}$ .

When control of noise on the power buses is important, it is possible to isolate sections of the chip that are particularly noisy. The data and address buses are particularly noisy because they continually change state, and the same can be true of serial ports and timer pins. The amount of noise generated by a particular pin is dependent upon the load being driven and the switching frequency. A designer who knows which power and ground connections serve particular pins can shield other signal conductors from these noisy lines.

Figure 11 Pinout of MC68332 132-Pin Package

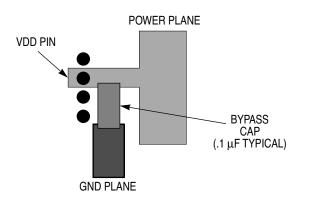

To control power supply/ground noise, use dedicated ground and supply planes. When designing a two-layer board, make the power and ground traces on the PCB as large as practical and connect a bypass capacitor to each power supply pin. The  $V_{DDI}/V_{SSI}$  and  $V_{DDE}/V_{SSE}$  supply pins should all have dedicated filter capacitors, and, ideally, all supply pins should be connected to the supply at a single location. A recommended layout technique is shown in **Figure 12**. Essentially, the bypass capacitor should be positioned so that it serves the power pin itself rather than the surrounding metal trace. This is accomplished by running a specific conductor to the power pin and then locating the bypass capacitor as close to the power pin as possible.

Another way to control power supply noise created by the MCU is to put a small inductor in series with the power supply lines for the port drivers. This method can help control noise on the power traces of the PCB. However, it should be used only as a last resort, because it can introduce other noise problems. Also, a series inductor in the power supply line will probably have little effect on radiated noise, which is generally a result of the port driver switching speed. Limiting instantaneous current change by putting an inductor in series with the power supply pin for the port will not appreciably affect the current through a particular driver because the integrated circuit generally has enough internal capacitance to support an instantaneous current surge while the driver switches.

Figure 12 Proper Placement of a Bypass Capacitor

The  $V_{DDSYN}$  and  $V_{STBY}$  supply pins should be separated and isolated from  $V_{DD}$  with a low pass filter. Any supply noise present on  $V_{DDSYN}$  will translate into shifts in the system clock generated from the PLL. Always supply power to  $V_{DDSYN}$ , even when using an external oscillator and bypassing the internal PLL.

#### 2.8.2 A Few Suggestions for Reducing Emissions

In general, follow standard design practices for EMC. A list of techniques that are often used in board design follows. These techniques are guidelines for good design, not strict rules, and are not specific to designs that incorporate the MC68331 or MC68332.

- Minimize the number of devices on the board. Capacitive coupling tends to occur around the holes that connect a particular layer of the board to the power and ground planes.

- Use a canned oscillator instead of a crystal, to reduce emissions from the oscillator. If a crystal circuit must be used, locate it as centrally as possible.

- Use a four layer PCB. As a general rule, a multilayer board is at least ten times better than a two layer board for both emissions and immunity. To reduce emissions even further, enclose the signal traces between the power and ground planes because the added capacitance between the signal trace and ground results in a lower characteristic impedance.

- Plot thick layout lines with the layout program, then cut the actual traces on the board thin.

- If a trace that conducts a high frequency signal must be routed on the surface of the PCB, route ground traces parallel to it to reduce radiation and crosstalk. Connect the ground traces to ground planes at varied intervals not to exceed the wavelength/4 at the highest frequency or harmonic expected.

- Round off PCB trace corners as much as possible to reduce the amount of excess capacitance that is introduced to the trace at corners.

- Make spacing between adjacent active traces greater than the trace width to minimize crosstalk.

- Put a chassis ground ring on the periphery of each layer of the PCB, to intercept the field coming off the board. Interconnect these rings with small ceramic capacitors.

- Use ferrite chokes when troubleshooting. Placing a choke around a signal line and the return conductor carrying a differential signal causes fields developed in the ferrite core by the opposing currents to cancel. Ferrite chokes can also be used on input/output lines. Because board-mounted chokes increase the number of holes connecting to the supply planes, they should be used only as a last resort.

332TUT VDD LAYOUT

- Localize any high frequency circuits, such as the clock and address or data buses. Decouple locally using high frequency filters such as ferrite chokes or damping resistors. Be sure to separate the high speed and low speed circuits.

- Turn off any output signals (such as ECLK) that are not used.

- Shield the board externally.

- Reduce power supply noise as much as possible.

#### 2.8.3 Other Sources of Information

**Freescale** publishes two application notes on related subjects:

Designing for Electromagnetic Compatibility with HCMOS Microcontrollers (AN1050/D)

Transmission Line Effects in PCB Applications (AN1051/D).

EDN Magazine offers a reprint of the "Designer's Guide to Electromagnetic Compatibility."

Refer to 6 **SOURCES OF INFORMATION** for ordering information.

EMC consultants are probably the best source of information on this topic, since they specialize in EMC and RFI problems. Consultants can help troubleshoot real problems, conduct seminars and provide tutorials, books and software on the subject.

#### 2.9 Connecting Memory and Peripherals

The MCU offers many different ways to configure memory and peripherals. The user can decode the external bus interface externally or use chip-selects. Since it is usually more efficient to use the chip-selects, this tutorial does not cover signal decoding. However, the *SIM Reference Manual* (SIMRM/AD) gives detailed explanations and examples of how to decode signals for both 8- and 16-bit memory devices on pages 5-31 through 5-34. These examples also show how to use function code pins to determine which address space is being accessed.

The MC68332 can generate 12 chip-select signals. These signals can be used to expand the system. A chip-select signal selects and enables a particular peripheral device or memory chip for data <u>transfer</u>. The chip-select circuits can also be programmed to <u>generate</u> data transfer and size acknowledge (DSACK), interrupt acknowledge (IACK), and autovector (AVEC) signals.

## 2.9.1 Using Chip-Selects to Generate DSACK

<u>Chip-select circuits can</u> be configured to wait for external data and size acknowledge signals on the <u>DSACK1</u> and <u>DSACK0</u> lines or to generate internal <u>DSACK</u> signals. A circuit can generate an internal <u>DSACK</u> signal even if the pin is configured for discrete output or alternate function.

The chip-select logic can wait for a certain number of clock states before generating DSACK. These states are called wait states. Wait states are inserted after state three of a read or write bus cycle. A normal bus cycle lasts three clock cycles plus the number of wait clock cycles. The chip-select logic can insert a maximum of 13 wait states.

#### 2.9.1.1 The Relationship Between Wait States And Memory Speed

Memory speed and the number of wait states necessary are related by the following equations:

Address access time = (2.5 + WS) X  $t_{CYC(min)} - t_{CHAV(max)} - t_{DICL(min)}$

$Chip-select\ access\ time\ (MCU\ read\ cycle) = (2+WS)\ X\ t_{CYC(min)} - t_{CLSA(max)} - t_{DICL(min)}$

Chip-select access time (MCU write cycle) =  $(2 + WS) \times t_{CYC(min)} - t_{CLSA(max)} + t_{CLSN(min)}$

In the equations, WS is the number of wait states programmed in the  $\overline{DSACK}$  field. For fast termination mode, WS = -1, for zero wait states, WS = 0, for one wait state, WS = 1, etc. Also, it is assumed that chip-select assertion is based on address strobe. If it is based on data strobe, add  $2(t_{CYC})$  to  $t_{CLSA}$  for the write cycle chip-select access time. The other known parameters are shown in **Table 2**.

**Table 2 Parameters Needed for Calculating Memory Access Times**

| Parameter                                                                            |         | 16.78 MHz |         | 20.97 MHz |         | MHz   |

|--------------------------------------------------------------------------------------|---------|-----------|---------|-----------|---------|-------|

| Farameter                                                                            | Min     | Max       | Min     | Max       | Min     | Max   |

| Clock Period (t <sub>CYC</sub> )                                                     | 59.6 ns | _         | 47.7 ns | _         | 39.7 ns | _     |

| Clock Low to AS, DS, CS Asserted (t <sub>CLSA</sub> )                                | 2 ns    | 25 ns     | 0       | 23 ns     | 2       | 19 ns |

| Data In Valid to Clock Low (Data Setup) (t <sub>DICL</sub> )                         | 5 ns    | _         | 5 ns    | _         | 5 ns    | _     |

| Clock High to Address, FC, SIZE, $\overline{\text{RMC}}$ Valid ( $t_{\text{CHAV}}$ ) | 0       | 29 ns     | 0       | 23 ns     | 0       | 19 ns |

| Clock Low to AS, DS, CS Negated (t <sub>CLSN</sub> )                                 | 2 ns    | 29 ns     | 2 ns    | 23 ns     | 2 ns    | 19 ns |

MCU read cycle access time is used to determine the number of wait states needed for a given memory speed, because it is longer than write cycle access time, and is thus the limiting factor.

As an example, the equations below are solved for zero wait states, assuming 16.78 MHz timing:

Address access time =  $2.5 \times 59.6 \text{ ns} - 29 \text{ ns} - 5 \text{ ns} = 115 \text{ ns}$

Chip-select access time (MCU read cycle) =  $2 \times 59.6 \text{ ns} - 25 \text{ ns} - 5 \text{ ns} = 89.2 \text{ ns}$

Chip-select access time (MCU write cycle) =  $2 \times 59.6 \text{ ns} - 25 \text{ ns} + 2 \text{ ns} = 96.2 \text{ ns}$

The equations can also be solved for the number of wait states needed, given the memory speed. Use **Table 3** to find the number of wait states required for a particular memory speed. For example, with a 16.78 MHz clock, a memory with a write cycle time of 130 ns requires one wait state, since 130 ns is between 89.2 ns and 148.8 ns.

**Table 3 Memory Access Times in Nanoseconds**

|        | ,                   |         |                     |         |                            |         |  |

|--------|---------------------|---------|---------------------|---------|----------------------------|---------|--|

| Wait   | 16.78 MHz           |         | 20.97 MHz           |         | 25.17 MHz                  |         |  |

| States | CS Read Access/     | Address | CS Read Access/     | Address | CS Read Access/            | Address |  |

| Otates | Memory Write Access | Access  | Memory Write Access | Access  | <b>Memory Write Access</b> | Access  |  |

| F.T.   | 29.6                | 55.4    | 19.7                | 43.55   | 15.7                       | 35.55   |  |

| 0      | 89.2                | 115.0   | 67.4                | 91.25   | 55.4                       | 75.25   |  |

| 1      | 148.8               | 174.6   | 115.1               | 138.95  | 95.1                       | 114.95  |  |

| 2      | 208.4               | 234.2   | 162.8               | 186.65  | 134.8                      | 154.65  |  |

| 3      | 268.0               | 293.8   | 210.5               | 234.35  | 174.5                      | 194.35  |  |

| 4      | 327.6               | 353.4   | 258.2               | 282.05  | 214.2                      | 234.05  |  |

| 5      | 387.2               | 413     | 305.9               | 329.75  | 253.9                      | 273.75  |  |

| 6      | 446.8               | 472.6   | 353.6               | 377.45  | 293.6                      | 313.45  |  |

| 7      | 506.4               | 532.2   | 401.3               | 425.15  | 333.3                      | 353.15  |  |

| 8      | 566.0               | 591.8   | 449.0               | 472.85  | 373.0                      | 392.85  |  |

| 9      | 625.6               | 651.4   | 496.7               | 520.55  | 412.7                      | 432.55  |  |

| 10     | 685.2               | 711     | 544.4               | 568.25  | 452.4                      | 472.25  |  |

| 11     | 744.8               | 770.6   | 592.1               | 615.95  | 492.1                      | 511.95  |  |

| 12     | 804.4               | 830.2   | 639.8               | 663.65  | 531.8                      | 551.65  |  |

| 13     | 864.0               | 889.8   | 687.5               | 711.35  | 571.5                      | 591.35  |  |

## 2.9.2 Using Chip-Select Signals to Enable Boot Memory

The MCU CSBOOT chip-select circuit is always enabled from reset. Because the internal SRAM module is disabled out of reset, the CSBOOT signal is generally used to select an external boot ROM. The CSBOOT chip-select circuit features hardware-controlled selection of 8-bit or 16-bit bus width. Bus width is controlled

by the state of the DATA0 line at the release of the RESET signal. The default bus width out of reset is 16 bits because the DATA0 line is pulled up to logic level one internally; however, the internal pull-up circuit is weak, so it is best to follow the recommendations in **2.1 Using Data Bus Pins to Configure the MCU**

For example, to design a system that uses 16-bit boot memory built from two 27C512 byte EPROMs, connect the chip-select and output enable lines of the EPROMs to the CSBOOT line. Also connect MCU address lines ADDR[16:1] to address lines [15:0] of the memories. Do not use ADDR0 of the MCU. This system will be word accessible only.

In general, the MCU cannot make byte writes to word memory selected by  $\overline{\text{CSBOOT}}$ . This lack of byte write capability is not much of a practical limitation since the  $\overline{\text{CSBOOT}}$  signal is generally used for read-only access, and all CPU32 instructions must be word-aligned. However, if byte-write capability is required, the SIZ and  $\overline{\text{CSBOOT}}$  signals can be used to generate "high byte" and "low byte" chip-select signals. The only other way to modify individual bytes is to use word moves, being careful to write the original data back to the unchanged byte.

#### 2.9.3 Using Chip-Select Signals to Enable External Memory

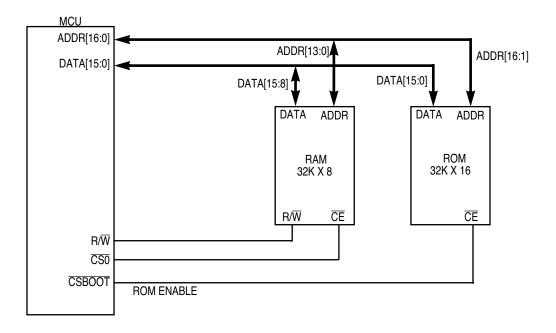

Chip-select signals can be configured for 8-bit or 16-bit ports. To use an 8-bit memory, connect the memory element's data lines to the upper half of the MCU data bus (DATA[15:8]). The MCU reads and writes an 8-bit port on the upper half of the data bus. During write cycles, data is echoed on the lower half of the data bus as well. Connect address line ADDR0 of the MCU to A0 of the memory. An example configuration is shown in **Figure 13**. To use a 16-bit memory, connect the memory data lines to MCU data bus (DATA[15:0]). Connect address line ADDR1 from the MCU to A0 of the memory.

332TUT EXT MEM CONN 1

Figure 13 Using Chip-Select Signals to Enable 8-Bit RAM

#### 2.9.3.1 How to Construct Word Memory from Two Byte Memories

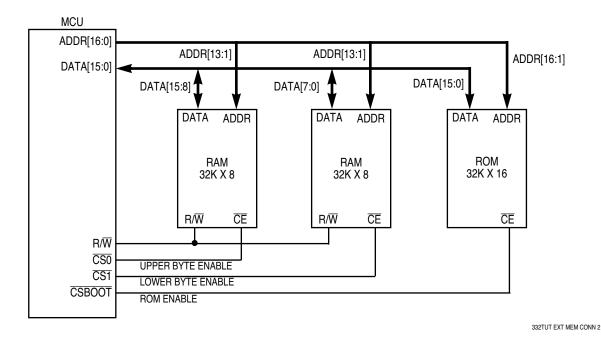

For chip-select signals other than  $\overline{\text{CSBOOT}}$ , forming word memory that is byte-accessible from two byte-wide devices is simple. Use a separate chip-select pin for each device, and configure chip-select logic to decode the upper and lower bytes, respectively. Each of the chip-select circuits must be configured as a 16-bit port, even though only eight bits of memory are being accessed. This allows both byte and word writes

—if both memories were connected to the same chip-select line, byte writes would corrupt the adjacent byte. This function can also be implemented in external logic by gating a single chip-select line with the MCU ADDR0 line to select upper and lower bytes. For ROM memory a single chip-select can be used to enable both byte-wide ROMs, as the MCU uses only the required byte on the data bus during a byte read and ignores the remaining byte.

**Figure 14** illustrates how to connect two 8-bit memories as one 16-bit port. It also shows the connections necessary for a 16-bit memory. In this example configuration,  $\overline{CSO}$  is connected to the chip enable pin ( $\overline{CE}$ ) of the first RAM chip and  $\overline{CSI}$  is connected to the chip enable pin of the second RAM chip. This effectively makes  $\overline{CSO}$  the upper byte enable and  $\overline{CSI}$  the lower byte enable. The R/W line of the MCU is connected to the R/W lines of both RAM chips.  $\overline{CSBOOT}$  is connected to the ROM enable. ADDR[13:1] of the MCU are connected to address lines [12:0] of each RAM chip, and ADDR[16:1] of the MCU are connected to address lines [15:0] of the ROM.

Figure 14 Configuring 16-Bit Memory with 8-Bit RAMs — Common R/W Input

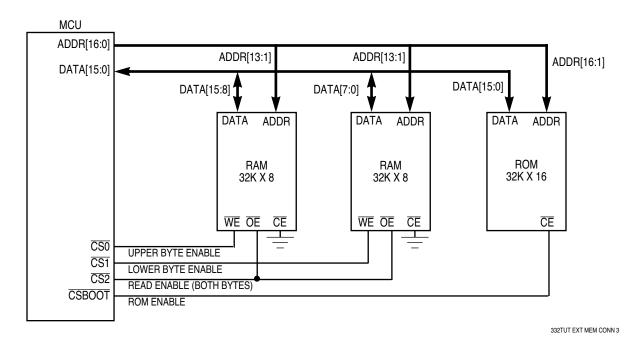

Another common configuration is shown in **Figure 15**. Here, the chip enables  $(\overline{CE})$  are always asserted, the write enable  $(\overline{WE})$  for upper byte access is connected to  $\overline{CSO}$ , the write enable for lower byte access is connected to  $\overline{CSO}$ , and the read enable  $(\overline{OE})$  for both upper and lower byte accesses are connected to  $\overline{CSO}$ . See **4.2.10 Example of SIM Initialization** for software to initialize this example system.

Figure 15 Configuring 16-Bit Memory with 8-Bit RAMs — Separate Read and Write Enables

#### 2.10 Using External Interrupts

The MCU has seven external interrupt lines,  $\overline{IRQ[7:1]}$ . These are active low signals that cause the processor to jump to a special routine and then return to the main code. The following paragraphs cover the basic elements of servicing external interrupt service requests. Refer to **4.1.1 Exceptions** for more detail. Chapter 6 of the *SIM Reference Manual* (SIMRM/AD) has an in-depth explanation of how to use external interrupts.

#### 2.10.1 Interrupt Priority Levels

An interrupt can be recognized on one of seven priority levels. These levels correspond to the numeric values of the external interrupt request lines. Level one  $(\overline{IRQ1})$  has the lowest priority; level seven  $(\overline{IRQ7})$  has the highest priority level. Levels one through six can be masked by the interrupt priority level (IPL) field contained in bits ten through eight of the CPU status register (SR). The level specified in the IPL field and all levels below it are masked and are not recognized by the CPU. Level seven is the only exception to this rule; it cannot be masked. Out of reset, the IPL field is set to level seven. Thus, levels one through six will not be recognized unless the IPL field is re-written to a lower value. The priority mask value can be changed by writing a new value into the appropriate bits of the SR.

#### **EXAMPLE:**

To allow interrupts on levels six and seven only, mask out levels five and below.

ANDI.W #\$F8FF, SR ORI.W #\$0500, SR

#### 2.10.2 Interrupt Arbitration Field

Most modules in the MCU can request interrupt service. The CPU treats external interrupts as interrupt service requests from the system integration module. The interrupt arbitration (IARB) field in the configuration register of each module determines which module's interrupt requests take precedence when the CPU receives more than one request at the same priority level. In order for interrupt requests to be acknowledged, each module must be assigned a unique IARB number between \$1 (lowest precedence) and \$F (highest precedence). Out of reset, the SIM IARB field has an initial value of \$F, while other modules have initial IARB values of \$0.

#### 2.10.3 Interrupt Vectors

Vectors are 32-bit addresses that point to the interrupt service routines (and other exception handlers). They are stored in a data structure called the exception vector table. There are 256 vector addresses in the exception vector table; of these, 199 can be used for interrupts. The base address of the exception vector table is determined by the value stored in the vector base register. A vector number is used to calculate the vector address, i.e., a displacement into the exception vector table.

#### 2.10.4 The Interrupt Acknowledge Cycle

After the CPU recognizes a valid interrupt request, the CPU begins the interrupt acknowledge (IACK) cycle. The CPU changes the IPL mask value to the level of the acknowledged interrupt to preclude lower-or-equal priority interrupt requests, then initiates a read cycle in CPU space. Since there is no dedicated IACK pin on the MCU, an external IACK signal is usually provided by a chip-select pin.

Vector numbers can be supplied by the device requesting interrupt service, or they can be generated automatically. Vector numbers supplied by the device cause the CPU to access one of 192 user vectors in the exception vector table; automatically generated vectors cause the CPU to access one of the seven autovectors in the table. Each method of vector number acquisition requires a different form of IACK cycle termination. If a vector number is supplied, either the requesting device must terminate the IACK cycle with a DSACK signal or the chip-select logic must generate the DSACK signal internally. If an autovector is used, an external device can assert the AVEC signal or an AVEC signal can be generated by the chip-select logic. Since normal bus cycles occur in user or supervisor space, but an IACK cycle occurs in CPU space, the same chip-select circuit cannot be used to terminate both an IACK cycle and a normal bus cycle.

#### 2.10.4.1 User Vectors

Once an interrupting device has placed a user vector number on the external data bus in response to an IACK signal from the MCU, either the device must terminate the IACK cycle with  $\overline{DSACK}$ , or the chip-select logic must generate  $\overline{DSACK}$  internally. When the bus cycle has been terminated, the vector number is left-shifted twice (multiplied by four), then a 32-bit vector address is formed by concatenating the upper 22 bits of the vector base register, the shifted value, and %00. The CPU then saves the current context, loads the 32-bit vector into the PC, and begins to execute the service routine at that address.

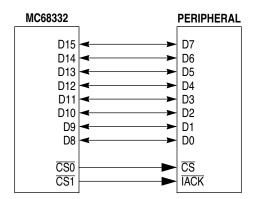

An example is shown in **Figure 16**. Chip select one is configured for interrupt acknowledge and automatic generation of the  $\overline{\text{DSACK}}$  signal. It is connected to the IACK pin of the peripheral. Because the processor drives \$FFFFFx onto the address bus and drives the function code pins to indicate CPU space during an IACK cycle, the chip-select base address register must be programmed to \$FFFX. When the CPU recognizes an interrupt and initiates an IACK cycle,  $\overline{\text{CS1}}$  is asserted. In response, the peripheral drives an 8-bit vector number onto the data bus. Chip-select logic then terminates the IACK cycle with  $\overline{\text{DSACK}}$ .

332TUT PERI CONN

Figure 16 Chip-Select Line Used for Interrupt Acknowledge

#### 2.10.4.2 Autovectors

When an external device cannot supply a vector number in response to an IACK cycle, an autovector can be used instead. The autovector number is determined by the priority of the interrupt request. For example, autovector number two corresponds to  $\overline{IRQ2}$ . In order for an autovector to be used the IACK cycle must be terminated by an  $\overline{AVEC}$  signal. There are two ways to do this: either assert the  $\overline{AVEC}$  signal externally or use the chip-select circuitry to provide the  $\overline{AVEC}$  signal. Once the bus cycle has been terminated, the CPU saves the current context, loads the 32-bit vector into the PC, and begins to execute the service routine at that address.

One way to use autovectors is to tie the AVEC pin to ground. This effectively generates an external AVEC signal only in response to all IACK cycles caused by external interrupt service requests. If it is not desirable for all external interrupts to autovector, specific external devices can assert AVEC in response to an IACK cycle. However, in this case it is usually easier to set up a chip-select circuit to provide the AVEC signal internally.

Perform the following steps to set up a chip-select circuit to generate the AVEC signal:

- 1. Configure the chip-select pin for any of its available functions in the pin assignment register.

- 2. Program the appropriate base address register to \$FFF8 or higher.

- 3. Select the following fields in the appropriate option register:

- A. MODE Bit select asynchronous mode (%0)

- B. BYTE Field select assertion for both bytes (%11)

- C. R/W Field select assertion for both reads and writes (%11)

- D. STRB Bit select synchronization with  $\overline{AS}$  (%0)

- E. DSACK Field select number of wait states (user specified)

- F. SPACE Field select CPU space assertion (%00)

- G. IPL Field select interrupt priority level (user specified)

- H. AVEC Bit enable AVEC generation (%1).

See **4.2 Configuring the System Integration Module** for a more detailed description of the fields in chip-select option registers.

#### 2.10.5 Level-Sensitive versus Edge-Sensitive Interrupt Pins

Interrupt pins [RQ[6:1]] are level sensitive. Assertion of an active-low signal connected to one of these pins is recognized as a valid interrupt request if the interrupt priority level of the pin is greater than the value of the IPL field in the CPU status register (SR). Once an interrupt service request is recognized, the SR is copied onto the stack, then the IPL value is changed to match the priority level of the interrupt being serviced. This prevents interrupts of the same or lower priority while the service routine executes. For instance, if the IPL value is \$3, and a level five service request is recognized, the SR is stacked, then the IPL value is changed to \$5. An RTE instruction at the end of the service routine normally terminates interrupt service. RTE pops the stacked SR, and thus restores the original IPL value. The IPL field can also be changed by writing to the SR. If an interrupt service routine writes a lower value to the IPL field while the request signal is still asserted, the CPU recognizes a second service request. Avoid changing the IPL value during execution of the interrupt service routine.

IRQ7 is both edge and level sensitive. Level seven interrupts cannot be masked by the IPL field. When a level seven interrupt service request is recognized, the current value of the status register is pushed onto the stack, and the IPL value is changed to \$7.

It is very important to make certain that the IRQ7 signal be negated before the level seven interrupt service routine ends. A new level seven interrupt will be recognized in the following cases:

If the IRQ7 signal negates and is then re-asserted while the interrupt service routine is executing.

If the IRQ7 signal remains asserted through the RTE instruction that ends the service routine is executed.

If the IRQ7 signal is asserted and the IPL field is written during execution of the interrupt service routine. This is true even when the mask is re-written to \$7.

Provide for negation of the signal within the service routine, and avoid writing to the SR during execution of the level seven interrupt service routine.

#### 2.10.6 Checklist for External Interrupt Acknowledge

Is the desired pin configured as an interrupt pin instead of an I/O pin?

The interrupt pins are dual-function pins. Their initial configuration is determined by the state of data bus pin nine at the release of reset. After reset, their configuration is determined by the port F pin assignment register.

Was the starting address of the interrupt routine written to the vector offset address?

The CPU must be told where the interrupt service routine begins. See **4.1.1 Exceptions** for a more detailed explanation.

Is the IARB field in the SIMCR a unique, non-zero value between \$1 and \$F?

All interrupting modules must have a unique, non-zero value in the IARB field

• Is the IPL field in the CPU status register set to a value lower than the desired interrupt level?

The CPU will not recognize an interrupt that is at the same level or lower than the value in the IPL field. Level seven is the only exception to this rule; it is always recognized.

• Is the IACK cycle terminated with AVEC or DSACK?

The IACK cycle must be terminated by assertion of the AVEC or DSACK signals, or a chip-select circuit must be configured to assert AVEC or DSACK internally.

• Does the interrupt request signal negate inside the exception handler?

It is a good idea to control negation of the interrupt in software. The interrupt should be negated before the RTE instruction.

# Freescale Semiconductor, Inc. 3 ESTABLISHING COMMUNICATION

#### 3.1 Communicating with the Target Board

After a target board has been built, it is generally necessary to communicate with it for debugging purposes. Although a designer can write a ROM monitor or modify CPU32Bug to communicate with the MCU via the serial port, it is simpler and often more effective to use an emulator or the CPU32 background debug mode (BDM) for communication.

#### 3.1.1 Using an Emulator

An emulator is a direct replacement for the chip that is used to evaluate both software and signals on the target board. Emulators can be very sophisticated and costly, but are very useful in tracking down design problems because they allow the designer to see exactly what the MCU is doing at every step of operation. When both the board and code are fully debugged, the emulator is removed and the MCU is placed on the board.

#### 3.1.2 Using Background Debug Mode

Background debug mode is a special CPU operating mode that allows an external host to take control of the MCU. BDM is a very useful tool for debugging. During BDM operation, normal instruction execution is suspended, and microcode executes built-in debugging instructions under external control. Since BDM suspends processor execution, an external host can examine and change memory and registers. BDM instructions and the protocol required to use them are described in detail in the *CPU32 Reference Manual* (CPU32RM/AD). *A BDM Driver Package for Modular Microcontrollers* (AN1230/D), shows how to implement a BDM communication interface using C-language drivers.

While a BDM interface is relatively easy to implement, ready-made BDM interfaces are inexpensive and reliable. Freescale sells the M68ICD32 BDM debugger made by P&E Microcomputer Systems. The M68ICD32 consists of the necessary cable and software to implement BDM debugging on an IBM-compatible PC. All the discussions in this section assume that M68ICD32 is being used.

#### 3.1.2.1 BDM Signals

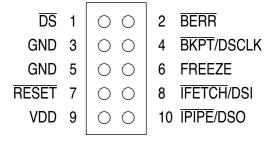

To use BDM, simply connect ten MCU lines to pins on the development board that are spaced so that a female Berg connector can plug into them. **Figure 17** shows the pinouts for the recommended 10-pin BDM connector. **Table 4** describes the BDM signals. Refer to **3.2.1.2 Using the EVK in Background Debug Mode** for a discussion of the older, 8-pin connector.

332TUT BERG10

Figure 17 10-Pin BDM Connector

#### **Table 4 BDM Connections**

| 10-Pin Connector | 8-Pin Connector | Signal          | Use                                                                                                                                                 |

|------------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | _               | DS              | Data Strobe                                                                                                                                         |

| 2                | _               | BERR            | Output from ICD to BERR input                                                                                                                       |

| 3                | 1               | GND             | Ground Reference                                                                                                                                    |

| 4                | 2               | BKPT/DSCLK      | Output from ICD to BKPT input; assertion causes MCU to first enable and then enter background mode. Once in BDM, this pin becomes the serial clock. |

| 5                | 3               | GND             | Ground Reference                                                                                                                                    |

| 6                | 4               | FREEZE          | Output from MCU indicating whether it is operating normally or is in BDM                                                                            |