Order this document by MC68L11D3/D

# SEMICONDUCTOR TECHNICAL DATA

MOTOROLA

# MC68L11D3

# Supplement to Technical Data Low Voltage Devices

The MC68L11D3 is an extended-voltage version of the MC68HC11D3 microcontroller that can operate in applications that require supply voltages as low as 3.0 Volts. Operation of the MC68L11D3 is identical to that of the MC68HC11D3 in all aspects other than electrical parameters.

This document provides MC68L11D3 electrical characteristics. It is a supplement to Appendix A of the *MC68HC11D3 Technical Data* (MC68HC11D3/D). Refer to the data book for technical information regarding use and operation of the microcontroller. The extended-range electrical characteristics in this supplement will be incorporated into the data book in a subsequent revision.

#### Features

- Suitable for Battery-Powered Portable and Hand-Held Applications

- Excellent for use in Devices such as Remote Sensors and Actuators

- Reduced RF Noise

- Operating Performance is Same at 5V and 3V

| Package     | Temperature   | Frequency | Features   | MC Order Number |

|-------------|---------------|-----------|------------|-----------------|

| 44-Pin PLCC | 0° to + 70° C | 2 MHz     | Custom ROM | MC68L11D3FN2    |

|             |               |           | No ROM     | MC68L11D0FN2    |

| 44-Pin QFP  | 0° to + 70° C | 2 MHz     | Custom ROM | MC68L11D3FB2    |

|             |               |           | No ROM     | MC68L11D0FB2    |

#### **Ordering Information**

## SUPPLEMENT TO APPENDIX A ELECTRICAL CHARACTERISTICS: LOW VOLTAGE DEVICES

| Rating                                                                                                                           | Symbol           | Value                                            | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------|------|

| Supply Voltage                                                                                                                   | V <sub>DD</sub>  | 0.3 to + 7.0                                     | V    |

| Input Voltage                                                                                                                    | Vin              | - 0.3 to + 7.0                                   | v    |

| Operating Temperature Range<br>MC68L11D3                                                                                         | T <sub>A</sub>   | T <sub>L</sub> to T <sub>H</sub><br>- 20 to + 70 | °C   |

| Storage Temperature Range                                                                                                        | T <sub>stg</sub> | - 55 to + 150                                    | °C   |

| Current Drain per Pin*<br>Excluding V <sub>DD</sub> , V <sub>SS</sub> , AV <sub>DD</sub> , V <sub>RH</sub> , and V <sub>RL</sub> | ID.              | 25                                               | mA   |

#### Table A-1a. Maximum Ratings

\*One pin at a time, observing maximum power dissipation limits.

Internal circuitry protects the inputs against damage caused by high static voltages or electric fields; however, normal precautions are necessary to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. Extended operation at the maximum ratings can adversely affect device reliability. Tying unused inputs to an appropriate logic voltage level (either GND or  $V_{DD}$ ) enhances reliability of operation.

| Characteristic<br>Average Junction Temperature                                                                                                     |          | Symbol           | Value                                                                | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------------------------------------------------------------------|------|

|                                                                                                                                                    |          | Тј               | $T_A + (P_D \times \Theta_{JA})$                                     | °C   |

| Ambient Temperature                                                                                                                                |          | TA               | User-determined                                                      | ∞    |

| Package Thermal Resistance (Junction-to-Ambient)<br>40-Pin Plastic DIP<br>44-Pin Plastic Leaded Chip Carrier (PLCC)<br>44-Pin Quad Flat Pack (QFP) |          | θ <sub>JA</sub>  | 50<br>50<br>85                                                       | °C/W |

| Total Power Dissipation (Note 1)                                                                                                                   |          | PD               | P <sub>INT</sub> + P <sub>I/O</sub><br>K/ (T <sub>J</sub> + 273°C)   | W    |

| Device Internal Power Dissipation                                                                                                                  |          | PINT             | I <sub>DD</sub> × V <sub>DD</sub>                                    | w    |

| I/O Pin Power Dissipation                                                                                                                          | (Note 2) | P <sub>I/O</sub> | User-determined                                                      | w    |

| A Constant                                                                                                                                         | (Note 3) | к                | $P_{D} \times (T_{A} + 273^{\circ}C) + \Theta_{JA} \times P_{D}^{2}$ | W∙∘C |

Table A-2a. Thermal Characteristics

NOTES:

1. This is an approximate value, neglecting  $P_{I/O}$ .

- 2. For most applications  $\mathsf{P}_{I/O}$  «  $\mathsf{P}_{INT}$  and can be neglected.

- 3. K is a constant pertaining to the device. Solve for K with a known  $T_A$  and a measured  $P_D$  (at equilibrium). Use this value of K to solve for  $P_D$  and  $T_J$  iteratively for any value of  $T_A$ .

| MC68L11D3      | SUPPLEMENT TO APPENDIX A   | MOTOROLA |

|----------------|----------------------------|----------|

| TECHNICAL DATA | ELECTRICAL CHARACTERISTICS | A–1      |

### Table A-3a. DC Electrical Characteristics

| $V_{DD}$ = 3.0 Vdc to 5.5 Vdc, $V_{SS}$ = 0 Vdc, T                                                                                       | $A = T_L$ to $T_H$ , unless                                      | s otherwise n                      | oted                                           |                                                |                  |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------|------------------------------------------------|------------------------------------------------|------------------|

| Characteristic                                                                                                                           |                                                                  | Symbol                             | Min                                            | Мах                                            | Unit             |

| All Outputs Except XTAL, RE                                                                                                              | outs_except XTAL<br>SET, and MODA                                | V <sub>OL</sub><br>V <sub>OH</sub> | <br>V <sub>DD</sub> – 0.1                      | 0.1                                            | V<br>V           |

| $I_{Load} = \pm 10.0 \ \mu A$                                                                                                            |                                                                  |                                    |                                                |                                                |                  |

| RE<br>I <sub>Load</sub> = – 0.5mA, V <sub>DD</sub> = 3.0 V                                                                               | <u>uts E</u> xcept XTAL,<br>SET, and MODA                        | V <sub>OH</sub>                    | V <sub>DD</sub> – 0.8                          |                                                | V                |

| $\frac{I_{Load} = -0.8 \text{ mA, } V_{DD} = 4.5 \text{ V}}{\text{Output Low Voltage}}$ All Outp                                         | outs Except XTAL                                                 |                                    |                                                |                                                | V                |

| $I_{Load} = 1.6 \text{ mA}, V_{DD} = 5.0 \text{ V}$<br>$I_{Load} = 1.0 \text{ mA}, V_{DD} = 3.0 \text{ V}$                               |                                                                  | V <sub>OL</sub>                    |                                                | 0.4                                            | v                |

| Input High Voltage All Input                                                                                                             | ts Except <u>RESET</u><br>RESET                                  | VIH                                | 0.7 x V <sub>DD</sub><br>0.8 x V <sub>DD</sub> | V <sub>DD</sub> + 0.3<br>V <sub>DD</sub> + 0.3 | V<br>V           |

| Input Low Voltage                                                                                                                        | All Inputs                                                       | VIL                                | V <sub>SS</sub> – 0.3                          | 0.2 x V <sub>DD</sub>                          | V                |

|                                                                                                                                          | PA7, PA3,<br>PC[7 <u>:0],</u> P <u>D[7:0],</u><br>ODA/LIR, RESET | ŀoz                                | _                                              | ±10                                            | μΑ               |

| Input Leakage Current<br>V <sub>in</sub> = V <sub>DD</sub> or V <sub>SS</sub> PA<br>V <sub>in</sub> = V <sub>DD</sub> or V <sub>SS</sub> | A[2:0], IRQ, XIRQ<br>MODB/V <sub>STBY</sub>                      | lin                                | _                                              | ±1<br>±10                                      | μ <b>Α</b><br>μΑ |

| RAM Standby Voltage                                                                                                                      | Power down                                                       | V <sub>SB</sub>                    | 2.0                                            | V <sub>DD</sub>                                | V                |

| RAM Standby Current                                                                                                                      | Power down                                                       | ISB                                |                                                | 10                                             | μA               |

| Input Capacitance PA[2:0], IR<br>PA7, PA3, PB[7:0], PC[7:0], PD[7:0], M                                                                  | RQ, XIRQ, <u>EXTAL</u><br>ODA/LIR, RESET                         | C <sub>in</sub>                    |                                                | 8<br>12                                        | pF<br>pF         |

| Output Load Capacitance All Output                                                                                                       | s Except PD[4:1]<br>PD[4:1]                                      | બ                                  | _                                              | 90<br>100                                      | pF<br>pF         |

| Characteristic                                                                                                                           |                                                                  | Symbol                             | 1 MHz                                          | 2 MHz                                          | Unit             |

| Maximum Total Supply Current (Note 2)                                                                                                    |                                                                  |                                    |                                                |                                                | 1.1.81-          |

| RUN:                                                                                                                                     |                                                                  | IDD                                |                                                | 1-                                             |                  |

| Single-Chip Mode                                                                                                                         | V <sub>DD</sub> = 5.5 V<br>V <sub>DD</sub> = 3.0 V               |                                    | 8<br>4                                         | 15<br>8                                        | mA<br>mA         |

| Expanded Multiplexed Mode                                                                                                                | $V_{DD} = 5.5 V$                                                 |                                    | 14                                             | 27                                             | mA               |

|                                                                                                                                          | $V_{DD} = 3.0 V$                                                 |                                    | 7                                              | 14                                             | mA               |

| WAIT: (All Peripheral Functions Shu                                                                                                      | t Down)                                                          | WIDD                               |                                                |                                                |                  |

| Single-Chip Mode                                                                                                                         | V <sub>DD</sub> = 5.5 V<br>V <sub>DD</sub> = 3.0 V               |                                    | 3<br>1.5                                       | 6<br>3                                         | mA<br>mA         |

| Expanded Multiplexed Mode                                                                                                                | $V_{DD} = 5.5 V$<br>$V_{DD} = 5.5 V$                             |                                    | 5                                              | 10                                             | mA               |

|                                                                                                                                          | $V_{DD} = 3.0 V$                                                 |                                    | 2.5                                            | 5                                              | mA               |

| STOP:                                                                                                                                    |                                                                  | SIDD                               | 50                                             | 50                                             | 🔺                |

| Single-Chip Mode, No Clocks                                                                                                              | V <sub>DD</sub> = 5.5 V<br>V <sub>DD</sub> = 3.0 V               |                                    | 50<br>25                                       | 50<br>25                                       | μΑ<br>μΑ         |

| Maximum Power Dissipation                                                                                                                |                                                                  | PD                                 |                                                |                                                | - ~ ·            |

| Single-Chip Mode                                                                                                                         | V <sub>DD</sub> = 5.5 V                                          |                                    | 44                                             | 85                                             | mW               |

|                                                                                                                                          | $V_{DD} = 3.0 V$                                                 |                                    | 12                                             | 24                                             | mW               |

| Expanded Multiplexed Mode                                                                                                                | $V_{DD} = 5.5 V$                                                 |                                    | 77<br>21                                       | 150                                            | m W<br>m W       |

|                                                                                                                                          | V <sub>DD</sub> = 3.0 V                                          |                                    | 21                                             | 42                                             | mW               |

$V_{DD} = 3.0$  Vdc to 5.5 Vdc,  $V_{SS} = 0$  Vdc,  $T_{A} = T_{I}$  to  $T_{H}$ , unless otherwise noted

NOTES:

1. V<sub>OH</sub> specification for RESET and MODA is not applicable because they are open-drain pins. V<sub>OH</sub> specification not applicable to ports C and D in wired-OR mode.

2. EXTAL is driven with a square wave, and  $t_{cyc} = 1000$  ns for 1 MHz rating;  $t_{cyc} = 500$  ns for 2 MHz rating;  $V_{IL} \le 0.2$  V;  $V_{IH} \ge V_{DD} - 0.2$  V; No dc loads.

| MOTOROLA | SUPPLEMENT TO APPENDIX A   | MC68L11D3             |

|----------|----------------------------|-----------------------|

| A-2      | ELECTRICAL CHARACTERISTICS | <b>TECHNICAL DATA</b> |

#### NOTES:

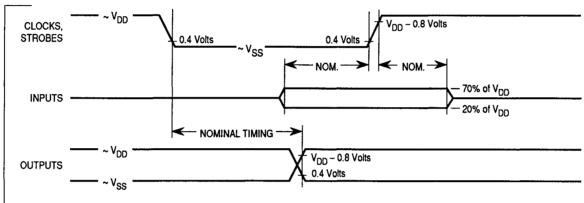

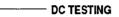

Full test loads are applied during all DC electrical tests and AC timing measurements.

During AC timing measurements, inputs are driven to 0.4 volts and V<sub>DD</sub> – 0.8 volts while timing measurements are taken at the 20% and 70% of  $\rm V_{\rm DD}\,$  points.

| MC68L11D3      | SUPPLEMENT TO APPENDIX A   | MOTOROLA |

|----------------|----------------------------|----------|

| TECHNICAL DATA | ELECTRICAL CHARACTERISTICS | A–3      |

| Characteristic                                                                                                           | Symbol             | 1.0    | MHz | 2.0    | MHz | Unit                                 |

|--------------------------------------------------------------------------------------------------------------------------|--------------------|--------|-----|--------|-----|--------------------------------------|

|                                                                                                                          |                    | Min    | Max | Min    | Max |                                      |

| Frequency of Operation                                                                                                   | fo                 | dc     | 1.0 | dc     | 2.0 | MHz                                  |

| E-Clock Period                                                                                                           | t <sub>cyc</sub>   | 1000   | —   | 500    | _   | ns                                   |

| Crystal Frequency                                                                                                        | <sup>f</sup> XTAL  | —      | 4.0 | 1      | 8.0 | MHz                                  |

| External Oscillator Frequency                                                                                            | 4 f <sub>o</sub>   | dc     | 4.0 | dc     | 8.0 | MHz                                  |

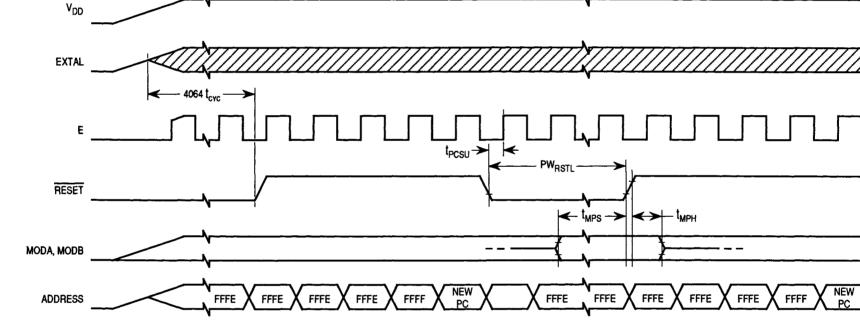

| Processor Control SetupTime<br>t <sub>PCSU</sub> = 1/4 t <sub>cyc</sub> + 75 ns                                          | <sup>t</sup> PCSU  | 325    | —   | 200    | -   | ns                                   |

| Reset Input Pulse Width<br>To Guarantee External Reset Vector<br>Minimum Input Time (Can Be Preempted by Internal Reset) | PW <sub>RSTL</sub> | 8<br>1 | _   | 8<br>1 |     | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| Mode Programming Setup Time                                                                                              | tMPS               | 2      |     | 2      | —   | t <sub>cyc</sub>                     |

| Mode Programming Hold Time                                                                                               | t <sub>MPH</sub>   | 10     |     | 10     | _   | ns                                   |

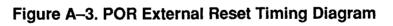

| Interrupt Pulse Width, IRQ Edge-Sensitive Mode<br>PW <sub>IRQ</sub> = t <sub>cyc</sub> + 20 ns                           | PWirq              | 1020   | —   | 520    | -   | ns                                   |

| Wait Recovery Startup Time                                                                                               | twrs               |        | 4   |        | 4   | t <sub>cyc</sub>                     |

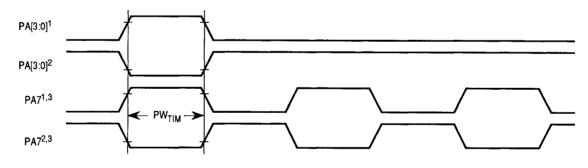

| Timer Pulse Width, Input Capture Pulse Accumulator Input $PW_{TIM} = t_{Cyc} + 20 \text{ ns}$                            | PW <sub>TIM</sub>  | 1020   |     | 520    | —   | ns                                   |

# Table A-4a. Control Timing

NOTES:

1. RESET is recognized during the first clock cycle it is held low. Internal circuitry then drives the pin low for four clock cycles, releases the pin, and samples the pin level two cycles later to determine the source of the interrupt. Refer to SECTION 5 RESETS AND INTERRUPTS for further detail.

2. All timing is shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD},$  unless otherwise noted.

NOTES:

1. Rising edge sensitive input

$V_{DD}$  = 3.0 Vdc to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_{A}$  =  $T_{L}$  to  $T_{H}$

Falling edge sensitive input

Maximum pulse accumulator clocking rate is E-clock frequency divided by 2.

| MOTOROLA | SUPPLEMENT TO APPENDIX A   | MC68L11D3      |

|----------|----------------------------|----------------|

| A-4      | ELECTRICAL CHARACTERISTICS | TECHNICAL DATA |

MOTOROLA A-5

Figure A-4. STOP Recovery Timing Diagram

| MOTOROLA | SUPPLEMENT TO APPENDIX A   | MC68L11D3      |

|----------|----------------------------|----------------|

| A-6      | ELECTRICAL CHARACTERISTICS | TECHNICAL DATA |

MC68L11D3 TECHNICAL DATA

SUPPLEMENT TO APPENDIX A ELECTRICAL CHARACTERISTICS

NOTE: RESET also causes recovery from WAIT.

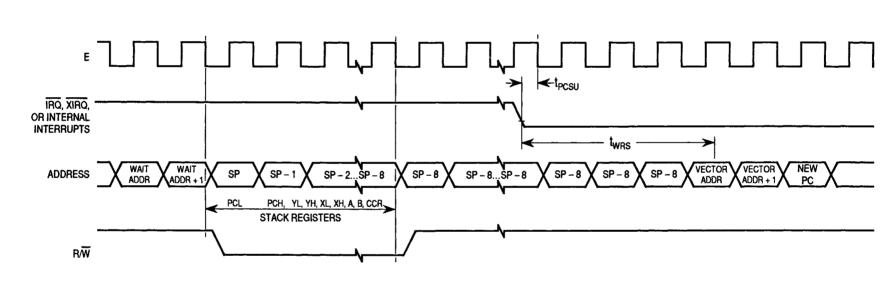

# Figure A-5. WAIT Recovery from Interrupt Timing Diagram

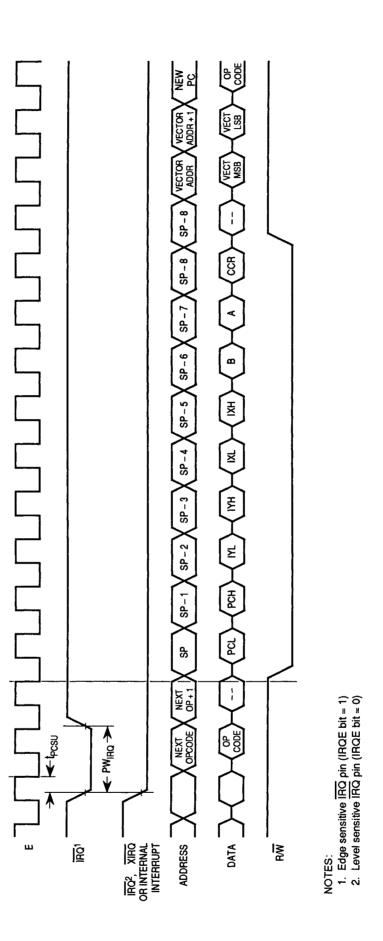

Figure A-6. Interrupt Timing Diagram

ŝ

| MOTOROLA | SUPPLEMENT TO APPENDIX A   | MC68L11D3      |

|----------|----------------------------|----------------|

| A-8      | ELECTRICAL CHARACTERISTICS | TECHNICAL DATA |

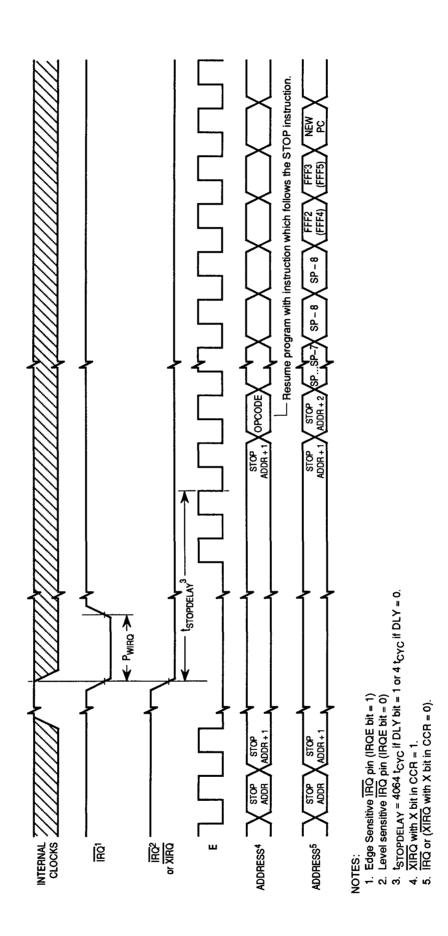

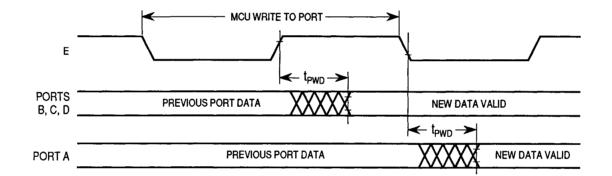

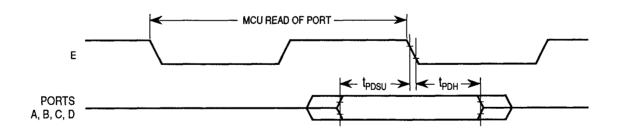

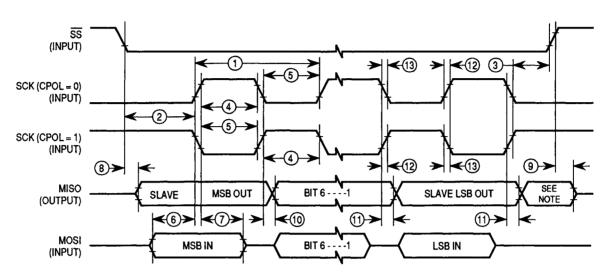

# Table A-5a. Peripheral Port Timing

$V_{DD}$  = 3.0 Vdc to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_{A}$  =  $T_{L}$  to  $T_{H}$

| Characteristic                                                                                     |                   | 1.0 MHz |            | 2.0 MHz |            | Unit     |

|----------------------------------------------------------------------------------------------------|-------------------|---------|------------|---------|------------|----------|

|                                                                                                    |                   | Min     | Max        | Min     | Max        | 1        |

| Frequency of Operation (E-Clock Frequency)                                                         | fo                | dc      | 1.0        | dc      | 2.0        | MHz      |

| E-Clock Period                                                                                     | t <sub>cyc</sub>  | 1000    | -          | 500     | _          | ns       |

| Peripheral Data Setup Time<br>MCU Read of Ports A, B, C, and D                                     | <sup>t</sup> PDSU | 100     | _          | 100     |            | ns       |

| Peripheral Data Hold Time<br>MCU Read of Ports A, B, C, and D                                      | <sup>t</sup> PDH  | 50      | _          | 50      | —          | ns       |

| Delay Time, Peripheral Data Write                                                                  | tpwD              |         |            |         |            |          |

| MCU Write to Port A<br>MCU Writes to Ports B, C, and D<br>$t_{PWD} = 1/4 t_{cyc} + 150 \text{ ns}$ |                   | _       | 250<br>400 |         | 250<br>275 | ns<br>ns |

NOTES:

1. Port C and D timing is valid for active drive (CWOM and DWOM bits not set in PIOC and SPCR registers respectively).

2. All timing is shown with respect to 20%  $V_{\text{DD}}$  and 70%  $V_{\text{DD}}$ , unless otherwise noted.

# Figure A–7. Port Write Timing Diagram

#### Figure A–8. Port Read Timing Diagram

| MC68L11D3      | SUPPLEMENT TO APPENDIX A   | MOTOROLA |

|----------------|----------------------------|----------|

| TECHNICAL DATA | ELECTRICAL CHARACTERISTICS | A-9      |

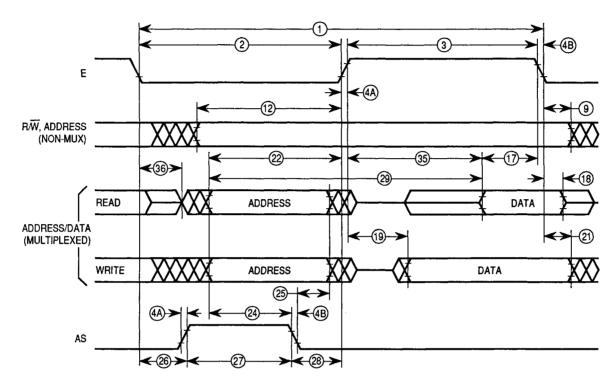

# Table A-6a. Expansion Bus Timing

$V_{DD}$  = 3.0 Vdc to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_{A}$  =  $T_{L}$  to  $T_{H}$

| Num      | Characteristic                                                                                                                  |           | Symbol              | 1.0 MHz |          | 2.0 MHz |          | Unit     |

|----------|---------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------|---------|----------|---------|----------|----------|

|          |                                                                                                                                 |           |                     | Min     | Max      | Min     | Max      |          |

|          | Frequency of Operation (E-Clock Frequency                                                                                       | ()        | fo                  | dc      | 1.0      | dc      | 2.0      | MHz      |

| 1        | Cycle Time                                                                                                                      |           | t <sub>cyc</sub>    | 1000    | _        | 500     | _        | ns       |

| 2        | Pulse Width, E Low<br>PW <sub>EL</sub> = 1/2 t <sub>cyc</sub> – 25 ns                                                           |           | PWEL                | 475     |          | 225     | -        | ns       |

| 3        | Pulse Width, E High<br>PW <sub>EH</sub> = 1/2 t <sub>cyc</sub> – 30 ns                                                          |           | PW <sub>EH</sub>    | 470     |          | 220     |          | ns       |

| 4A<br>4B | E and AS Rise Time<br>E and AS Fall Time                                                                                        |           | ኑ<br>t <sub>f</sub> |         | 25<br>25 | _       | 25<br>25 | ns<br>ns |

| 9        | Address Hold Time<br>t <sub>AH</sub> = 1/8 t <sub>cyc</sub> – 30 ns                                                             | (Note 1a) | <sup>t</sup> AH     | 95      |          | 33      |          | ns       |

| 12       | Non-Muxed Address Valid Time to E Rise<br>t <sub>AV</sub> = PW <sub>EL</sub> - (t <sub>ASD</sub> + 80 ns)                       | (Note 1a) | t <sub>AV</sub>     | 275     | —        | 88      | -        | ns       |

| 17       | Read Data Setup Time                                                                                                            |           | t <sub>DSR</sub>    | 30      |          | 30      |          | ns       |

| 18       | Read Data Hold Time (Max = t <sub>MAD</sub> )                                                                                   |           | <sup>t</sup> DHR    | 0       | 150      | 0       | 88       | ns       |

| 19       | Write Data Delay Time<br>t <sub>DDW</sub> = 1/8 t <sub>cyc</sub> + 70 ns                                                        | (Note 1a) | tDDW                | —       | 195      | _       | 133      | ns       |

| 21       | Write Data Hold Time<br>t <sub>DHW</sub> = 1/8 t <sub>cyc</sub> - 30 ns                                                         | (Note 1a) | <sup>t</sup> DHW    | 95      | —        | 33      | -        | ns       |

| 22       | Muxed Address Valid Time to E Rise<br>t <sub>AVM</sub> = PW <sub>EL</sub> – (t <sub>ASD</sub> + 90 ns)                          | (Note 1a) | <sup>t</sup> a∨M    | 265     | —        | 78      |          | ns       |

| 24       | Muxed Address Valid Time to AS Fall<br>t <sub>ASL</sub> = PW <sub>ASH</sub> - 70 ns                                             |           | <sup>t</sup> ASL    | 150     | —        | 25      |          | ns       |

| 25       | Muxed Address Hold Time<br>t <sub>AHL</sub> = 1/8 t <sub>cyc</sub> – 30 ns                                                      | (Note 1b) | <sup>t</sup> AHL    | 95      | —        | 33      |          | ns       |

| 26       | Delay Time, E to AS Rise<br>t <sub>ASD</sub> = 1/8 t <sub>cyc</sub> – 5 ns                                                      | (Note 1a) | tASD                | 120     | —        | 58      |          | ns       |

| 27       | Pulse Width, AS High<br>PW <sub>ASH</sub> <del>=</del> 1/4 t <sub>cyc</sub> – 30 ns                                             |           | PWASH               | 220     |          | 95      |          | ns       |

| 28       | Delay Time, AS to E Rise<br>t <sub>ASED</sub> = 1/8 t <sub>cyc</sub> – 5 ns                                                     | (Note 1b) | <sup>t</sup> ASED   | 120     | —        | 58      | _        | ns       |

| 29       | MPU Address Access Time<br>tACCA = t <sub>cyc</sub> - (PW <sub>EL</sub> - t <sub>AVM</sub> ) - t <sub>DSR</sub> -t <sub>f</sub> | (Note 1a) | <sup>t</sup> ACCA   | 735     | —        | 298     |          | ns       |

| 35       | MPU Access Time<br>tACCE = PWEH - tDSR                                                                                          |           | <sup>t</sup> ACCE   |         | 440      | —       | 190      | ns       |

| 36       | Muxed Address Delay<br>(Previous Cycle MPU Read)<br>t <sub>MAD</sub> = t <sub>ASD</sub> + 30 ns                                 | (Note 1a) | <sup>t</sup> MAD    | 150     | _        | 88      |          | ns       |

۲

NOTES:

Input clocks with duty cycles other than 50% affect bus performance. Timing parameters affected by input clock duty cycle are identified by (a) and (b). To recalculate the approximate bus timing values, substitute the following expressions in place of 1/8 t<sub>cyc</sub> in the above formulas, where applicable:

(a) (1-DC) × 1/4 t<sub>cyc</sub>

(b) DC × 1/4 t<sub>cyc</sub>

Where:

DC is the decimal value of duty cycle percentage (high time).

All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless otherwise noted.

| MOTOROLA | SUPPLEMENT TO APPENDIX A   | MC68L11D3             |

|----------|----------------------------|-----------------------|

| A-10     | ELECTRICAL CHARACTERISTICS | <b>TECHNICAL DATA</b> |

NOTE: Measurement points shown are 20% and 70% of  $\mathrm{V}_{\mathrm{DD}}.$

Figure A–9. Multiplexed Expansion Bus Timing Diagram

| MC68L11D3      | SUPPLEMENT TO APPENDIX A   | MOTOROLA |

|----------------|----------------------------|----------|

| TECHNICAL DATA | ELECTRICAL CHARACTERISTICS | A–11     |

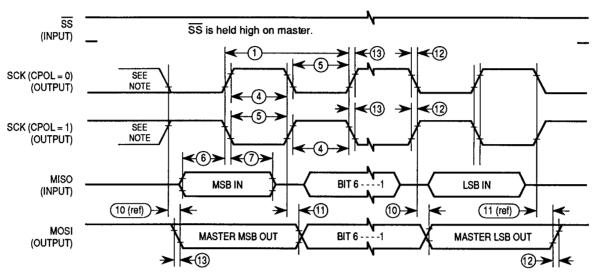

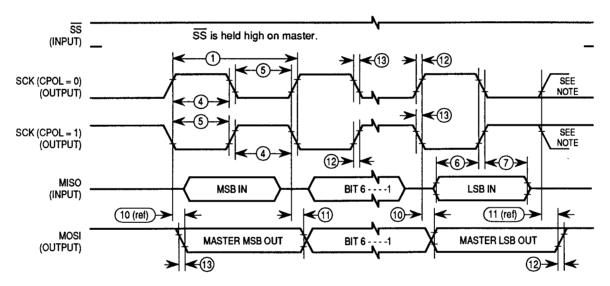

| Num | Characteristic                                                                                                                                                | Symbol                                         | 1.0         | MHz        | 2.0 MHz    |            | Unit                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------|------------|------------|------------|------------------------|

|     |                                                                                                                                                               |                                                | Min         | Max        | Min        | Max        |                        |

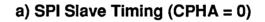

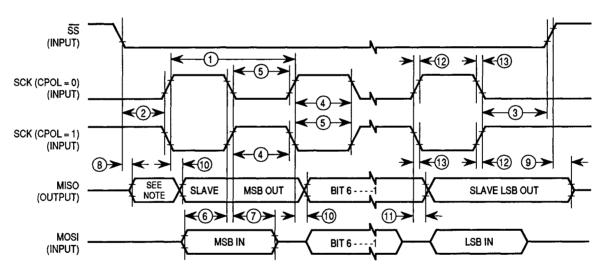

|     | Operating Frequency<br>Master<br>Slave                                                                                                                        | f <sub>op(m)</sub><br>f <sub>op(s)</sub>       | dc<br>dc    | 0.5<br>1.0 | dc<br>dc   | 0.5<br>2.0 | f <sub>op</sub><br>MHz |

| 1   | Cycle Time<br>Master<br>Slave                                                                                                                                 | <sup>t</sup> cyc(m)<br>t <sub>cyc(s)</sub>     | 2.0<br>1000 | _          | 2.0<br>500 |            | t <sub>cyc</sub><br>ns |

| 2   | Enable Lead Time<br>Master (Note 2)<br>Slave                                                                                                                  | <sup>t</sup> lead(m)<br><sup>t</sup> lead(s)   | <br>500     | _          | <br>250    |            | ns<br>ns               |

| 3   | Enable Lag Time<br>Master (Note 2)<br>Slave                                                                                                                   | <sup>t</sup> lag(m)<br><sup>t</sup> lag(s)     | 500         |            | 250        |            | ns<br>ns               |

| 4   | Clock (SCK) High Time<br>Master<br>Slave                                                                                                                      | <sup>t</sup> w(SCKH)m<br><sup>t</sup> w(SCKH)s | 680<br>380  | _          | 340<br>190 | _          | ns<br>ns               |

| 5   | Clock (SCK) Low Time<br>Master<br>Slave                                                                                                                       | <sup>t</sup> w(SCKL)m<br><sup>t</sup> w(SCKL)s | 680<br>380  |            | 340<br>190 | _          | ns<br>ns               |

| 6   | Data Setup Time (Inputs)<br>Master<br>Slave                                                                                                                   | t <sub>su(m)</sub><br>t <sub>su(s)</sub>       | 100<br>100  | _          | 100<br>100 |            | ns<br>ns               |

| 7   | Data Hold Time (Inputs)<br>Master<br>Slave                                                                                                                    | <sup>t</sup> h(m)<br>t <sub>h(s)</sub>         | 100<br>100  | -          | 100<br>100 | _          | ns<br>ns               |

| 8   | Access Time<br>(Time to Data Active from High-Imp. State)<br>Slave                                                                                            | ta                                             | 0           | 120        | o          | 120        | ns                     |

| 9   | Disable Time<br>(Hold Time to High-Impedance State)<br>Slave                                                                                                  | t <sub>dis</sub>                               | _           | 240        | _          | 240        | ns                     |

| 10  | Data Valid (After Enable Edge) (Note 3)                                                                                                                       | t <sub>v(s)</sub>                              | —           | 240        | _          | 240        | ns                     |

| 11  | Data Hold Time (Outputs) (After Enable Edge)                                                                                                                  | tho                                            | 0           | —          | 0          | _          | ns                     |

| 12  | Rise Time (20% V <sub>DD</sub> to 70% V <sub>DD</sub> , C <sub>L</sub> = 200 pF)<br>SPI Outputs (SCK, MOSI, and MISO)<br>SPI Inputs (SCK, MOSI, MISO, and SS) | t <sub>m</sub><br>t <sub>rs</sub>              | _           | 100<br>2.0 | _          | 100<br>2.0 | ns<br>μs               |

| 13  | Fall Time (70% V <sub>DD</sub> to 20% V <sub>DD</sub> , C <sub>L</sub> = 200 pF)<br>SPI Outputs (SCK, MOSI, and MISO)<br>SPI Inputs (SCK, MOSI, MISO, and SS) | t <sub>fm</sub><br>t <sub>fs</sub>             | _           | 100<br>2.0 | _          | 100<br>2.0 | ns<br>µs               |

•

# Table A–7a. Serial Peripheral Interface Timing

$V_{DD}$  = 3.0 Vdc to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$

NOTES:

1. All timing is shown with respect to 20%  $V_{\text{DD}}$  and 70%  $V_{\text{DD}}$ , unless otherwise noted.

2. Signal production depends on software.

3. Assumes 100 pF load on all SPI pins.

| MOTOROLA | SUPPLEMENT TO APPENDIX A   | MC68L11D3             |

|----------|----------------------------|-----------------------|

| A–12     | ELECTRICAL CHARACTERISTICS | <b>TECHNICAL DATA</b> |

NOTE: This first clock edge is generated internally but is not seen at the SCK pin.

NOTE: This last clock edge is generated internally but is not seen at the SCK pin.

b) SPI Master Timing (CPHA = 1)

Figure A-10. SPI Timing Diagram (1 of 2)

| MC68L11D3      | SUPPLEMENT TO APPENDIX A   | MOTOROLA |

|----------------|----------------------------|----------|

| TECHNICAL DATA | ELECTRICAL CHARACTERISTICS | A–13     |

NOTE: Not defined but normally MSB of character just received.

NOTE: Not defined but normally LSB of character previously transmitted.

b) SPI Slave Timing (CPHA = 1)

Figure A-10. SPI Timing Diagram (2 of 2)

| MOTOROLA | SUPPLEMENT TO APPENDIX A   | MC68L11D3             |

|----------|----------------------------|-----------------------|

| A–14     | ELECTRICAL CHARACTERISTICS | <b>TECHNICAL DATA</b> |

| MC68L11D3      | SUPPLEMENT TO APPENDIX A   | MOTOROLA |

|----------------|----------------------------|----------|

| TECHNICAL DATA | ELECTRICAL CHARACTERISTICS | A–15     |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and Ary is an eregistered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Literature Distribution Centers:

٥

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England. JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan.

ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

1ATX31103-0 PRINTED IN USA 6/92 IMPERIAL LITHO 86084 12,000 MCU YGACAA

4