**16-BIT SCRATCH PAD MEMORY CELL** WITH GATED INPUTS

# **MEMORIES**

# MC5484L\* MC7484L,P\*

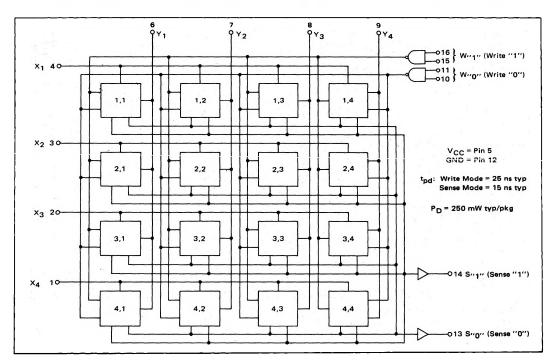

This 16-Bit memory cell serves as the basic building block for scratch pad memory systems having cycle times of less than 100 ns. The basic cell provides 16 words of one-bit memory operating in the non-destructive readout (NDRO) mode.

The memory contains 16 flip-flops arranged in a fourby-four matrix. A single bit of the matrix is selected by

driving one of four X select lines and one of four Y select lines above the select threshold. Two sense amplifiers are shared by all 16 bits and provide a double rail output from the selected bit. The sense output of many devices can be "wired ORed" together since the output stage does not have a pullup resistor or network. Two gated write amplifiers allow a "1" or a "0" to be written into a selected bit.

# - OPERATING SEQUENCE -

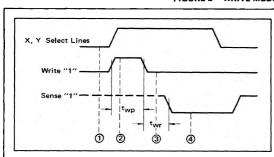

### FIGURE 1 - READ MODE TIMING DIAGRAM

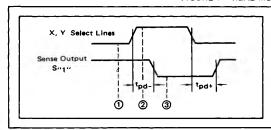

- (1) All X and Y selection lines and both write inputs are low (less than +0.8 V).

- (2) Desired bit selected by driving the appropriate X and Y select lines more positive than +2.1 V.

- 3 After the turn-on delay time (tpd-), the S"1" output will be low (less than +0.45 V) and the S"0" output will be high (more than +2.5 V), providing that a "1" is stored in the selected bit.

<sup>\*</sup>L suffix = 16-pin dual in-line ceramic package (Case 620).

P suffix = 16-pin dual in-line plastic package (Case 612).

FIGURE 2 - WRITE MODE TIMING DIAGRAM

- (less than +0.8 V).

- ② Bit location selected by driving the appropriate X and Y select lines more positive than +2.1 V. To write a "1", drive the write "1" input more positive than +2.1 V for a minimum time of 25 ns (t<sub>wp</sub>).

- 3 Write "1" line returned to low state.

- The stored bit can be read after the write recovery time (t<sub>Wr</sub>) of 60 ns. (The sense output is in an indeterminate state between steps 2 and 4.)

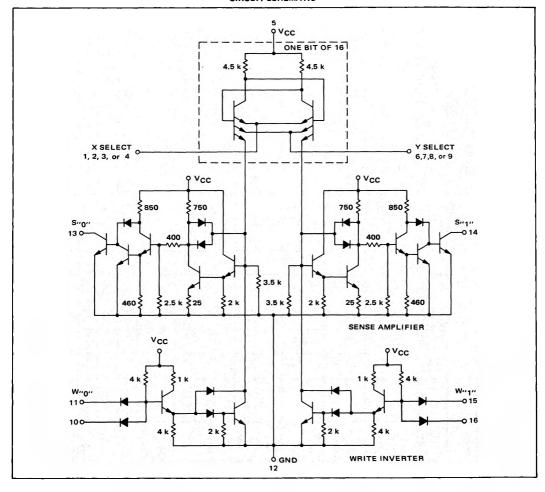

### CIRCUIT SCHEMATIC

# ELECTRICAL CHARACTERISTICS

Test procedures are shown for only one bit. Other bits are tested in the same manner. In addition, test procedures are

| manner. In addition test procedures are                     | test proc   | edures a | are        |                                     |               |            |                                  |              |     |          |     | TES      | ST CURRE | NT/VO  | TAGE    | ALUES          | TEST CURRENT/VOLTAGE VALUES (A)I Temperatures)    | tures  |      |      |      |                                          |

|-------------------------------------------------------------|-------------|----------|------------|-------------------------------------|---------------|------------|----------------------------------|--------------|-----|----------|-----|----------|----------|--------|---------|----------------|---------------------------------------------------|--------|------|------|------|------------------------------------------|

| shown for only one Write input of each                      | Write inpu  | ut of ea | ch.        |                                     |               |            |                                  |              |     | Ą        | H   |          |          |        | >       | Volts          |                                                   |        |      |      |      |                                          |

| level. The other Write inputs are tested in the same manner | rite inputs | are test | peq        |                                     |               |            |                                  |              | OSI | *        | 'XY | Vin 1    | Vin 2    | V in 3 | ٧F      | V <sub>R</sub> | £,                                                | Vth W  | Nout | VCCL | VCCH |                                          |

|                                                             |             |          |            |                                     |               |            | •                                | MC5484       | 40  | 1.0      | 3.0 | 8.0      | 0.1      | 0      | 0       | 4.5            | 2.1                                               | 2.0    | 20.2 | -    | 5.5  |                                          |

|                                                             |             |          |            |                                     |               |            | -                                | MC7484       | 20  | 1.0      | 3.0 | $\vdash$ | 1.0      | 1.0    | 0       | 4.5            | 2.1                                               | 2.0    | 5.0  | 4.75 | 5.25 |                                          |

|                                                             |             | Ē        | Z T        | MC5484 Test Limits<br>-55 to +126°C | Limits<br>5°C | MC         | MC7484 Test Limits<br>0 to +70°C | Limits       |     |          |     | TEST C   | URRENT   | VOLTA  | GE APPL | IED TO P       | TEST CURRENT/VOLTAGE APPLIED TO PINS LISTED BELOW | BELOW  |      |      |      |                                          |

| Characteristic                                              | Symbol      | Test     | Min        | Max                                 | Unit          | Min        | Max                              | Unit         | .DS | 3        | 'XY | Vin 1    | Vin 2    | Vin 3  | ٧<br>۲  | × ×            | *>                                                | **     | Vout | VCCL | VCCH | Ond                                      |

| Input                                                       |             |          |            |                                     |               |            |                                  |              |     | $\vdash$ |     |          |          | -      |         |                |                                                   |        |      |      |      |                                          |

| Address Lines                                               | <u>u</u>    | -        | ı          | =                                   | mAdc          | 1          | F                                | mAdc         | 1   | 1        | -   | ,        | 1        | ,      | -       | 6,7,8,9        | 1                                                 | 1      | 1    | 1    | S    | 2,3,4,10,11,12,15,16                     |

|                                                             |             | 9        | •          | -                                   | mAdc          |            | ÷                                | mAdc         | -   | -        | -   | 1        | 1        | ,      | 7       | 1,2,3,4        | -                                                 | ,      | 1    | _    | 8    | 7,8,9,10,11,12,15,16                     |

| Write Inputs                                                |             | 5<br>5   | 1 1        | -1.60                               | mAdc<br>mAdc  | 1 1        | -1.60                            | mAdc<br>mAdc | 0.0 | 1 1      | 1 1 | 1 1      | 1 1      | 1 1    | 5 5     | Li             | 1 1                                               | 1.1    | 1 1  | 1.1  | លស   | 1,2,3,4,6,7,8,9,12,15,16                 |

| Leakage Current<br>Address Lines                            | ы           | - 9      | 1.1        | 0.4                                 | mAdc<br>mAdc  | 1.1        | 0.4                              | mAdc<br>mAdc | 1.1 | 11       | 11  | 1 1      | 1 1      | 1 1    | 11      | - o            | 1.1                                               | 10     | 1.1  | 11   | សស   | 2,3,4,6,7,8,9,10,11,12,15,16             |

| Write Inputs                                                |             | 5 2      | 1 1        | 0.0                                 | mAdc<br>mAdc  | 1 1        | 0.1                              | mAdc<br>mAdc | 1 1 | 1 1      | 1 1 | 1 1      | 1 1      | 1 1    | 1.1     | 5 t            | 1 1                                               | . ,    | 1 1  | 1 /  | ខេត  | 1,2,3,4,6,7,8,9,12,15,16                 |

| Breakdown Voltage<br>Address Lines                          | BVin        | - 0      | 5.5<br>5.5 | 1.1                                 | op op         | 5.5<br>5.5 | 1.1                              | V V V        | 1.1 | 1 1      | - w | , ,      | 11       | 11     | 1.1     | 1 1            | 1 1                                               | 1 1    | 1.1  | 11   | മം   | 2,34,6,7,8,9,10,11,12,15,16              |

| Write Inputs                                                |             | 5 &      | 5.5        | 1 1                                 | 9 ×           | 5.5        | 1.1                              | op op        |     | 5 75     | 1 1 | 10       | 1.1      |        | 1 1     | 1:1            | 1 1                                               | ı į    | 1 1  | 11   | សស   | 1,2,3,4,6,7,8,9,12,15,16                 |

| Output (Note 1) Output Voltage                              | *           |          |            |                                     |               |            |                                  |              |     |          |     |          |          |        |         |                | 9                                                 | 1<br>7 |      | u    |      | 72478013                                 |

| Logic "0" Level                                             | Vout 'C'    | 2        | 1          | 0.45                                | Vdc           | 1          | 0.45                             | Vďc          | 4   | 1        | 1   |          | 1        |        | 1       | 1              | 1,6                                               | į      | 1    | 2    | 1    | 2,3,4,7,8,9,10,11,12,15,16               |

| Write "O" Inhibit                                           | :           | ,        | ¥          | 1                                   | -             | 1          | ,                                |              |     | <u></u>  | 1   | 1,6      | -        | 1      | 15,16   | 10,11          | 1                                                 | 1      | '    | 2    | 1    | 2,3,4,7,8,9,12                           |

| Logic "O" Level                                             | Vout "0"    | 14       | -          | 0.45                                | Vdc           | -          | 0.45                             | Vdc          | 14  | -        | -   | -        | +        | -      | -       | 1              | 1,6                                               | 1      | '    | 2    | 6 -  | 2,3,4,7,8,9,10,11,12,15,16               |

| Write "0"                                                   | :           | ,        | -          | -                                   | - '           | -          | -                                | -            | -   | -        |     | -        | 1        | 5,16   |         | -              | 1,6                                               | 10,11  |      | 5    | 1    | 2,3,4,7,8,9,12                           |

| Logic "0" Level                                             | Yout "O"    | 13       | 4          | 0.45                                | Vdc           |            | 0.45                             | Vdc          | 13  | -        | _   | -        | -        | _      |         | _              | 1,6                                               | 1      | 1    | 5    | 1    | 2,3,4,7,8,9,10,11,12,15,16               |

| Write "1" Inhibit                                           | :           | -        | -          | -                                   | -             | 1.         | ì                                | ļ            | -   | 1        | 1   | 1,6      | 1        | -      | 10,11   | 16.16          | 1                                                 |        | 1.   | 2    | 1    | 2,3,4,7,8,9,12                           |

| Logic "O" Level                                             | Vout '0'    | 13       | 1          | 0.45                                | Vđc           | ŀ          | 0.45                             | Vdc          | 5   | 1        | 1   | 1        | ,        |        | (       | ,              | 1,6                                               | 1      | 1    | 2    | 1    | 2,3,4,7,8,9,10,11,12,15,16               |

| Write "1"                                                   | : 1         | 1 3      | ı          | 1 96                                | - 5           |            | 1 8                              | 1 3          | 1   | 1        | 1   | +        | -        | 10,11  | 1       | ı              | 1,6                                               | 15,16  | L    | S    | ſ    | 2,3,4,7,8,9,12                           |

| Leakage Current<br>Write "1"                                | :           | !        | '          | 3                                   | 3             | 1          | }                                |              | :   | -        | -   | -        | +-       | 10.11  | ,       |                | 1,6                                               | 15.16  | 1    | , u  | i    | 2.34.7.89.12                             |

| Leakage Current                                             | OLK         | 4        | 1          | 0.25                                | mAde          | -          | 0.25                             | mAdc         | ,   |          | ,   | ,        | 1,6      | 1      | ,       | ,              | ,                                                 | 1      | 4    | ء    | 1    | 2,3,4,7,8,9,10,11,12,15,16               |

| Write "C"                                                   |             | Ľ        | 1          | 1                                   | 1             | -          | ľ                                | ,            | ,   | ļ,       | 1   | ,        | -        | 91,51  | ,       | 1              | 1,6                                               | 10,11  | ١    | 2    | ĵ    | 2,3,4,7,8,9,12                           |

| Leakage Current                                             | lock        | 13       | r.         | 0.25                                | mAdc          | 1          | 0.25                             | mAdc         | ı   | 1        | ı   | ,        | 1,6      |        | ,       | 1              | 1                                                 |        | ೭    | ŝ    | ŷ    | 2,3,4,7,8,9,10,11,12,15,16               |

| Write "1"                                                   | )<br>:      | ,        | 1          | '                                   | -             | 1          | -                                | '            | ,   |          | ,   |          | ı        |        | ,       | 15,16          | 1,6,7,8,9                                         | ,      | ı,   | s    | 1    | 2,3,4,10,11,12                           |

| Leakage Current                                             | OLK         | 13       | ı          | 0.25                                | mAdc          | -          | 0.25                             | mAdc         | ,   | -        | -   | ,        | -        | -      | ,       | 1              | 1,6,7,8,9                                         | 1      | 13   | s    | 1    | 2,3,4,10,11,12,15,16                     |

| Write "O"                                                   | :           | ,        | ı          | ,                                   | -             | 1          | 1                                | ,            | ı   | 1        | -   | -        | -        | -      | _       | 10,11          | 1,6,7,8,9                                         | 1      | 1    | 2    | -    | 2,3,4,12,15,16                           |

| Leakage Current                                             | יסרע        | 14       | -          | 0.25                                | mAdc          | 1          | 0.25                             | mA.dc        | 1   | -        | -   | -        | ı        | _      | ,       | 1              | 1,6,7,8,9                                         | 1      | 14   | 2    | 1    | 2,3,4,10,11,12,15,16                     |

| Power Requirements<br>(Total Device)<br>Power Supply Drain  | Odj         | 20       | _          | 78#                                 | mAdc          |            | 91#                              | mAdc         | 1   | 1        |     | -        | 1        | 1      |         | ,              | 1                                                 | 1      | 1    | 1    | ď    | 1,2,3,4,6,7,8,9,10,<br>11,12,13,14,15,16 |

Note 1. Output logic "0" voltage and leakage purrent measurements are made as part of a functional test of a memory,

\*\* Indicates preconditioning procedures for the subsequent test. All power supply and input voltages must be

maintained between tests.

# Tested only at 25°C.

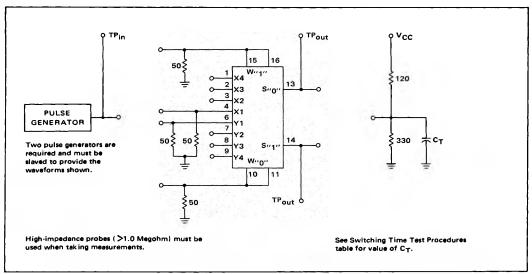

## SWITCHING TIME TEST CIRCUIT

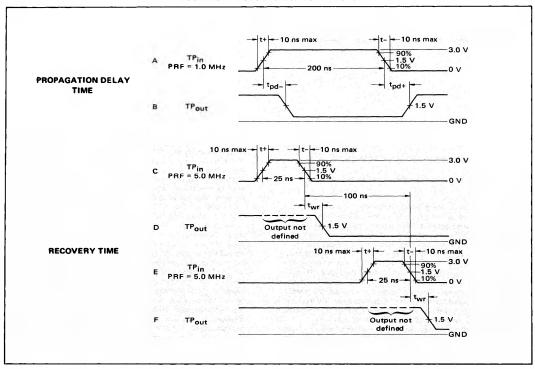

### **VOLTAGE WAVEFORMS AND DEFINITIONS**

### SWITCHING TIME TEST PROCEDURES

(Letters shown in test columns refer to waveforms)

|                                                                        | 7                 | Pin           |         |                     |                     |         | 10      | nput P              | in                  |                     |            |            | Output                   |            |     | Li               | mits             |

|------------------------------------------------------------------------|-------------------|---------------|---------|---------------------|---------------------|---------|---------|---------------------|---------------------|---------------------|------------|------------|--------------------------|------------|-----|------------------|------------------|

| Test                                                                   | Symbol            | Under<br>Test | 4<br>×1 | 3<br>X <sub>2</sub> | 2<br>X <sub>3</sub> | 1<br>X4 | 6<br>Y1 | 7<br>Y <sub>2</sub> | 8<br>Y <sub>3</sub> | 9<br>Y <sub>4</sub> | 10<br>Wo   | 15<br>W"1" | 13<br>S <sub>''0''</sub> |            | CT* | MC5484<br>ns max | MC7484<br>ns max |

| Turn-Off Delay Time                                                    | •••               | _             | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V   | 3.0 ∨   | 3.0 V               | 3.0 V               | 3.0 V               | Gnd        | 3.0 V      | _                        | Ī <u>-</u> | _   | -                |                  |

| (Address Lines to                                                      | •••               | = 1           | 3.0 V   | Gnd                 | Gnd                 | Gnd     | 3.0 V   | Gnd                 | Gnd                 | Gnd                 | 3.0 V      | Gnd        | 1                        | _          | ı   |                  |                  |

| Sense "0" Output)                                                      | tpd+              | 13            | A       | Gnd                 | Gnd                 | Gnd     | Α       | Gnd                 | Gnd                 | Gnd                 | Gnd        | Gnd        | В                        | -          | 15  | 25               | 25               |

|                                                                        | tpd+              | 13            | Α       | Gnd                 | Gnd                 | Gnd     | A       | Gnd                 | Gnd                 | Gnd                 | Gnd        | Gnd        | В                        | -          | 200 | 35               | 35               |

| Turn-Off Delay Time                                                    |                   | -             | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V   | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | 3.0 V      | Gnd        | -                        | -          | -   | -                | -                |

| (Address Lines to                                                      | •••               |               | 3.0 V   | Gnd                 | Gnd                 | Gnd     | 3.0 V   | Gnd                 | Gnd                 | Gnd                 | Gnd        | 3.0 V      | -                        | <u> </u>   | -   |                  |                  |

| Sense "1" Output)                                                      | tpd+              | 14            | A       | Gnd                 | Gnd                 | Gnd     | Α       | Gnd                 | Gnd                 | Gnd                 | Gnd        | Gnd        | _                        | В          | 15  | 25               | 25               |

|                                                                        | tpd+              | 14            | A       | Gnd                 | Gnd                 | Gnd     | A       | Gnd                 | Gnd                 | Gnd                 | Gnd        | Gnd        | _                        | В          | 200 | 35               | 35               |

| Turn-On Delay Time                                                     | •••               | -             | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V   | 3.0 V   | 3.0 V               | 3.0 ∨               | 3.0 V               | Gnd        | 3.0 V      | -                        | -          | -   |                  |                  |

| (Address Lines to                                                      | •••               | -             | 3.0 V   | Gnd                 | Gnd                 | Gnd     | 3.0 V   | Gnd                 | Gnd                 | Gnd                 | 3.0 V      | Gnd        | _                        | =          | _   | _                |                  |

| Sense "0" Output)                                                      | tpd-              | 13            | A       | Gnd                 | Gnd                 | Gnd     | A       | Gnd                 | Gnd                 | Gnd                 | Gnd        | Gnd        | В                        | -          | 15  | 45               | 45               |

|                                                                        | tpd-              | 13            | A       | Gnd                 | Gnd                 | Gnd     | A       | Gnd                 | Gnd                 | Gnd                 | Gnd        | Gnd        | В                        | Ι-         | 200 | 55               | 55               |

| Turn-On Delay Time                                                     | ···               | _             | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V   | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | 3.0 V      | Gnd        | _                        | Ι-         | -   | -                |                  |

| (Address Lines to                                                      | •••               | -             | 3.0 V   | Gnd                 | Gnd                 | Gnd     | 3.0 V   | Gnd                 | Gnd                 | Gnd                 | Gnd        | 3.0 V      | _                        | -          | _   |                  |                  |

| Sense "1" Output)                                                      | t <sub>pd</sub> - | 14            | Α       | Gnd                 | Gnd                 | Gnd     | A       | Gnd                 | Gnd                 | Gnd                 | Gnd        | Gnd        | _                        | В          | 15  | 45               | 45               |

|                                                                        | tpd-              | 14            | Α       | Gnd                 | Gnd                 | Gnd     | A       | Gnd                 | Gnd                 | Gnd                 | Gnd        | Gnd        | -                        | В          | 200 | 55               | 55               |

| Turn-Off Delay Time                                                    | 1                 |               | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V   | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | Gnd        | 3.0 V      | _                        | _          | _   | _                | _                |

| (4 Bits) (Address Lines                                                | •••               |               | 3.0 V   | Gnd                 | Gnd                 | Gnd     | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | 3.0 V      | Gnd        | _                        | -          | _   | _                | _                |

| to Sense "O" Output)                                                   | tpd+              | 13            | Α       | Gnd                 | Gnd                 | Gnd     | A       | A                   | Α                   | A                   | Gnd        | Gnd        | В                        | -          | 15  | 30               | 30               |

| Turn-Off Delay Time<br>(4 Bits) (Address Lines<br>to Sense "1" Output) | •••               | _             | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V   | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | 3.0 V      | Gnd        | _                        | _          | _   |                  |                  |

|                                                                        | ••                | -             | 3.0 V   | Gnd                 | Gnd                 | Gnd     | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | Gnd        | 3.0 V      |                          | -          | _   | _                |                  |

|                                                                        | tpd+              | 14            | Α       | Gnd                 | Gnd                 | Gnd     | A       | A                   | A                   | A                   | Gnd        | Gnd        | -                        | В          | 15  | 30               | 30               |

| Write Recovery Time                                                    | twr               | 14            | 3.0 V   | Gnd                 | Gnd                 | Gnd     | 3.0 ∨   | Gnd                 | Gnd                 | Gnd                 | E          | С          | _                        | Б          | 15  | 60               | 60               |

|                                                                        |                   | 13            | 3.0 V   | Gnd                 | Gnd                 | Gnd     | 3.0 V   | Gnd                 | Gnd                 | Gnd                 | E          | С          | F                        | -          | 15  | 60               | 60               |

| <del></del>                                                            |                   |               |         |                     |                     |         |         |                     |                     |                     |            |            |                          |            |     | ns min           | ns min           |

| Write Pulse Width                                                      | twp               | - 1           |         |                     |                     |         | Tes     | ted du              | ring t <sub>v</sub> | vr tests            | <b>i</b> . |            |                          |            |     | 25               | 25               |

<sup>\*</sup>Capacitance value for load of the Switching Time Test Circuit

## **OPERATING CHARACTERISTICS**

Sixteen flip-flops are arranged in a 4-by-4 matrix with each flip-flop representing one bit of 16 words. Each flip-flop, consisting of two cross-coupled triple-emitter transistors, is used to store one bit. Memory status of a particular bit is determined by sensing which of the two flip-flop transistors is conducting. One emitter of each of these transistors serves as the sensing output. All 16 of the logical "1" sensing outputs are connected to the sense logic "1" amplifier input, and all 16 of the logical "0" sensing outputs are connected to the sense logic "0" amplifier input. The remaining emitters on each transistor provides the matrix connections required for the X- and Y-address lines. Address line inputs are normally held at logic "0" and currents from all conducting flip-flop transistors flow out of these address lines.

To address a flip-flop both the X- and Y-address lines associated with that flip-flop are taken to a logic "1" voltage. Due to the matrix nature of the circuit, at least one address line of all flip-flops except the one being addressed will continue to remain at a logic "0" level and no change will occur on those flip-flops. But, in the ad-

dressed flip-flop, the current in the conducting transistor diverts from the address lines to the appropriate sense line and then to one of the sense amplifiers. Thus, either the sense amplifier associated with a logic "1" or the sense amplifier associated with a logic "0" is activated. When this occurs, the output of the activated sense amplifier drops from a logic "1" to a logic "0" level. The memory is non-destructive as the states of the flip-flops are not disturbed during sensing.

To store new information in a flip-flop, it is necessary to address it and apply logic "1" voltage to the appropriate write amplifier input. The output of the write amplifier responds by dropping to a logic "0" level. Since all logic "0" sense lines are connected to the output of the logic "0" write amplifier and all logic "1" sense lines are connected to the output of the logic "1" write amplifier, a logic "0" voltage on the output of a write amplifier will apply the same voltage to emitters of all flip-flop transistors connected to that amplifier. In all flip-flops except the one being addressed, this low voltage has no effect since at least one other emitter on each of the flip-flop transistors is held low by the address lines. But two possibilities exist with the flip-flop that is addressed. The flip-flop may already be in the desired state, in which case no change occurs. But if the flip-flop must be changed from one state to the other, the low voltage applied to the emitter of the transistor which is not conducting turns that transistor on, causing the other transistor to turn off.

<sup>\*\*</sup>Preconditioning procedures for subsequent test.

### TYPICAL APPLICATIONS

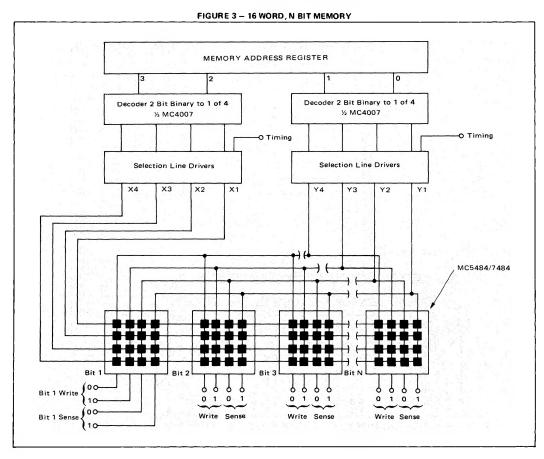

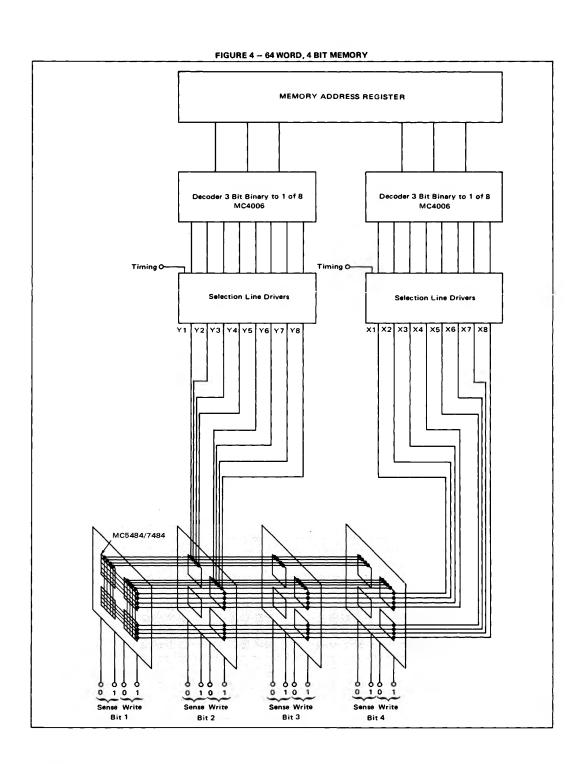

A fast scratch pad memory offers the system designer several design alternatives. Temporary memory with a greater storage capacity than simple registers can be distributed throughout a system. The basic technique for expanding bit capacity is shown in Figure 3; Figure 4 illustrates a method for expanding word capacity.

Optimum design of the selection line drivers depends on the specific system application. The maximum load presented to the drivers by the selection lines is a function of the sequence used to address the memory. The desired logic swing and noise immunity should also be considered when designing the drivers. Each of the 16 flip-flops draws a maximum dc supply current of 2.75 mA (for V<sub>CC</sub> = 5.0 Vdc). The total current flowing in all 16 flip-flops, and consequently the summed current in the eight selection lines, is 44 mA. (Each selection line is tested for a maximum of 11 mA).

Consider the sequence involved in selecting the four bits  $X_1Y_1$ ,  $X_1Y_2$ ,  $X_1Y_3$ , and  $X_1Y_4$  simultaneously. If the four Y select lines are enabled before the  $X_1$  line then each of the four X lines must carry the full current from four cells, i.e., 11 mA. The Y drivers must also have the capability of sinking 11 mA if the four X drivers

are enabled before a Y driver. However, if the memory accessing sequence specifies that only a single bit may be selected at a time and, consequently, that only one of the X (or Y) selection lines may be high at a time, then the driver requirements can be relaxed somewhat. This is possible because of current sharing in the multiemitters of the storage flip-flop transistors. If the voltages at the emitters of the "on" transistor differ by no more than approximately 100 mV, then each emitter will carry an appreciable portion of the transistor current. The saturation characteristics of the drivers determine the emitter potentials and, therefore, the division of cell current among the various drivers. Since the VOL of the driver will increase if the collector current increases, the selection currents will be almost evenly distributed among the drivers if the driver saturation characteristics are reasonably uniform. If operation is restricted to a single X selection line and a single Y selection line and current sharing is assumed, then each select line must be capable of carrying the full current from a single cell plus approximately one half of the current from three cells. Each line must, therefore, carry:

### 11/4 + (3) (1/2) (11/4) = 6.88 mA.

Since the dc output levels of the driver transistors determine the noise immunity of the selection line, the system noise environment and the desired noise immunity should enter into the driver selection.