# 8-Input NAND Gate

# **High-Performance Silicon-Gate CMOS**

The MC74HC30 is identical in pinout to the LS30. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.

#### **Features**

- Output Drive Capability: 10 LSTTL Loads

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 2 to 6 V

- Low Input Current: 1 μA

- High Noise Immunity Characteristic of CMOS Devices

- These are Pb-Free Devices

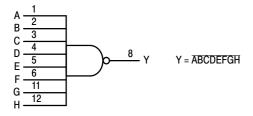

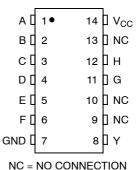

PINS 9, 10, 13 = NO CONNECTION PIN 14 =  $V_{CC}$  PIN 7 = GND

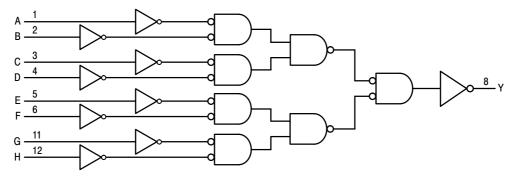

Figure 1. Logic Diagram

## ON Semiconductor®

http://onsemi.com

## MARKING DIAGRAMS

SOIC-14 D SUFFIX CASE 751A

TSSOP-14 DT SUFFIX CASE 948G

A = Assembly Location

WL, L = Wafer Lot

YY, Y = Year

WW, W = Work Week

G or = Pb-Free Package

(Note: Microdot may be in either location)

#### **PIN ASSIGNMENT**

## **FUNCTION TABLE**

| Inputs A through H   | Output<br>Y |

|----------------------|-------------|

| All inputs H         | L           |

| One or more inputs L | H           |

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 3 of this data sheet.

#### **MAXIMUM RATINGS**

| Symbol           | Parameter                                       |                                      | Value                         | Unit |

|------------------|-------------------------------------------------|--------------------------------------|-------------------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage (Referenced to GND)           | -0.5 to +7.0                         | V                             |      |

| V <sub>in</sub>  | DC Input Voltage (Referenced to GND)            |                                      | -1.5 to V <sub>CC</sub> + 1.5 | V    |

| V <sub>out</sub> | DC Output Voltage (Referenced to GND)           | -0.5 to V <sub>CC</sub> + 0.5        | V                             |      |

| I <sub>in</sub>  | DC Input Current, per Pin                       | ±20                                  | mA                            |      |

| l <sub>out</sub> | DC Output Current, per Pin                      | DC Output Current, per Pin           |                               |      |

| I <sub>CC</sub>  | DC Supply Current, V <sub>CC</sub> and GND Pins | urrent, V <sub>CC</sub> and GND Pins |                               | mA   |

| P <sub>D</sub>   | l •                                             | Package<br>Package                   | 500<br>TBD                    | mW   |

| T <sub>stg</sub> | Storage Temperature                             |                                      | -65 to +150                   | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range GND  $\leq$  ( $V_{in}$  or  $V_{out}$ )  $\leq$   $V_{CC}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or  $V_{CC}$ ). Unused outputs must be left open.

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol                             | Parameter                                            |                                                                            | Min         | Max                | Unit |

|------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------|-------------|--------------------|------|

| V <sub>CC</sub>                    | DC Supply Voltage (Referenced to GND)                |                                                                            | 2.0         | 6.0                | V    |

| V <sub>in</sub> , V <sub>out</sub> | DC Input Voltage, Output Voltage (Referenced to GND) |                                                                            | 0           | V <sub>CC</sub>    | V    |

| T <sub>A</sub>                     | Operating Temperature, All Package Types             |                                                                            | -55         | +125               | °C   |

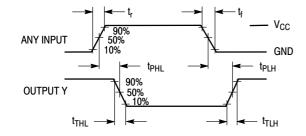

| t <sub>r</sub> , t <sub>f</sub>    | (Figure 2)                                           | $V_{CC} = 2.0 \text{ V}$ $V_{CC} = 4.5 \text{ V}$ $V_{CC} = 6.0 \text{ V}$ | 0<br>0<br>0 | 1000<br>500<br>400 | ns   |

## DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)

|                 |                                                   |                                                                                                                                                                                |                      | Guaranteed Limit   |                    | mit                |      |

|-----------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|--------------------|--------------------|------|

| Symbol          | Parameter                                         | Test Conditions                                                                                                                                                                | V <sub>CC</sub><br>V | – 55 to<br>25°C    | ≤ <b>85</b> °C     | ≤ 125°C            | Unit |

| V <sub>IH</sub> | Minimum High-Level Input<br>Voltage               | $V_{out}$ = 0.1 V or $V_{CC}$ – 0.1 V $ I_{out}  \le 20 \mu A$                                                                                                                 | 2.0<br>4.5<br>6.0    | 1.5<br>3.15<br>4.2 | 1.5<br>3.15<br>4.2 | 1.5<br>3.15<br>4.2 | V    |

| V <sub>IL</sub> | Maximum Low-Level Input<br>Voltage                | $V_{out}$ = 0.1 V or $V_{CC}$ – 0.1 V $ I_{out}  \le 20 \mu A$                                                                                                                 | 2.0<br>4.5<br>6.0    | 0.3<br>0.9<br>1.2  | 0.3<br>0.9<br>1.2  | 0.3<br>0.9<br>1.2  | V    |

| V <sub>OH</sub> | Minimum High-Level Output<br>Voltage              | $V_{in} = V_{IH} \text{ or } V_{IL}$<br>$ I_{out}  \le 20  \mu\text{A}$                                                                                                        | 2.0<br>4.5<br>6.0    | 1.9<br>4.4<br>5.9  | 1.9<br>4.4<br>5.9  | 1.9<br>4.4<br>5.9  | V    |

|                 |                                                   | $V_{in} = V_{IH} \text{ or } V_{IL} \qquad \begin{vmatrix} I_{out} \end{vmatrix} \le 4.0 \text{ mA} \\ \begin{vmatrix} I_{out} \end{vmatrix} \le 5.2 \text{ mA} \end{vmatrix}$ | 4.5<br>6.0           | 3.98<br>5.48       | 3.84<br>5.34       | 3.70<br>5.20       |      |

| V <sub>OL</sub> | Maximum Low-Level Output<br>Voltage               | $V_{in} = V_{IH} \text{ or } V_{IL}$<br>$ I_{out}  \le 20  \mu\text{A}$                                                                                                        | 2.0<br>4.5<br>6.0    | 0.1<br>0.1<br>0.1  | 0.1<br>0.1<br>0.1  | 0.1<br>0.1<br>0.1  | V    |

|                 |                                                   | $V_{in} = V_{IH} \text{ or } V_{IL} \qquad \begin{vmatrix} I_{out} \end{vmatrix} \le 4.0 \text{ mA} \\ \begin{vmatrix} I_{out} \end{vmatrix} \le 5.2 \text{ mA} \end{vmatrix}$ | 4.5<br>6.0           | 0.26<br>0.26       | 0.33<br>0.33       | 0.40<br>0.40       |      |

| I <sub>in</sub> | Maximum Input Leakage Current                     | V <sub>in</sub> = V <sub>CC</sub> or GND                                                                                                                                       | 6.0                  | ± 0.1              | ± 1.0              | ± 1.0              | μΑ   |

| I <sub>CC</sub> | Maximum Quiescent Supply<br>Current (per Package) | $V_{in} = V_{CC}$ or GND $I_{out} = 0 \mu A$                                                                                                                                   | 6.0                  | 2                  | 20                 | 40                 | μΑ   |

## AC ELECTRICAL CHARACTERISTICS ( $C_L$ = 50 pF, Input $t_r$ = $t_f$ = 6 ns)

|                                        |                                                                    |                      | Guaranteed Limit |                 |                 |      |

|----------------------------------------|--------------------------------------------------------------------|----------------------|------------------|-----------------|-----------------|------|

| Symbol                                 | Parameter                                                          | V <sub>CC</sub><br>V | – 55 to<br>25°C  | ≤ <b>85</b> °C  | ≤ 125°C         | Unit |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Maximum Propagation Delay, Any Input to Output Y (Figures 2 and 3) | 2.0<br>4.5<br>6.0    | 175<br>35<br>30  | 220<br>44<br>37 | 265<br>53<br>45 | ns   |

| t <sub>TLH</sub> ,<br>t <sub>THL</sub> | Maximum Output Transition Time, Any Output (Figures 2 and 3)       | 2.0<br>4.5<br>6.0    | 75<br>15<br>13   | 95<br>19<br>16  | 110<br>22<br>19 | ns   |

| C <sub>in</sub>                        | Maximum Input Capacitance                                          | -                    | 10               | 10              | 10              | pF   |

| Ī |          |                                          | Typical @ 25°C, V <sub>CC</sub> = 5.0 V |    | l |

|---|----------|------------------------------------------|-----------------------------------------|----|---|

|   | $C_{PD}$ | Power Dissipation Capacitance (Per Gate) | 27                                      | pF |   |

<sup>\*</sup>Includes all probe and jig capacitance

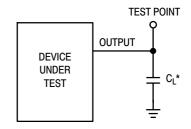

Figure 2. Switching Waveforms

Figure 3. Test Circuit

Figure 4. Expanded Logic Diagram

## **ORDERING INFORMATION**

| Device         | Package              | Shipping <sup>†</sup> |

|----------------|----------------------|-----------------------|

| MC74HC30ADG    | SOIC-14<br>(Pb-Free) | 55 Units/Rail         |

| MC74HC30ADR2G  | SOIC-14<br>(Pb-Free) | 2500/Tape & Reel      |

| MC74HC30ADTR2G | TSSOP-14*            |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. \*This package is inherently Pb-Free.

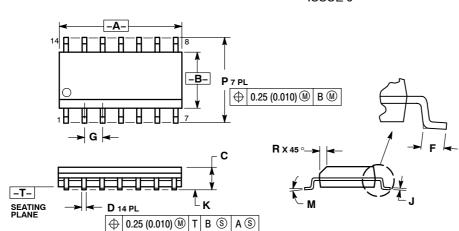

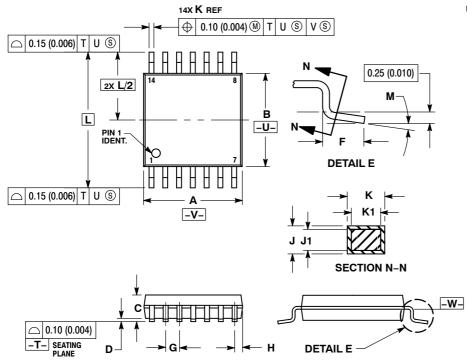

## PACKAGE DIMENSIONS

## SOIC-14 CASE 751A-03 **ISSUE J**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      | INC   | HES   |

|-----|-------------|------|-------|-------|

| DIM | MIN         | MAX  | MIN   | MAX   |

| Α   | 8.55        | 8.75 | 0.337 | 0.344 |

| В   | 3.80        | 4.00 | 0.150 | 0.157 |

| С   | 1.35        | 1.75 | 0.054 | 0.068 |

| D   | 0.35        | 0.49 | 0.014 | 0.019 |

| F   | 0.40        | 1.25 | 0.016 | 0.049 |

| G   | 1.27        | BSC  | 0.050 | BSC   |

| J   | 0.19        | 0.25 | 0.008 | 0.009 |

| K   | 0.10        | 0.25 | 0.004 | 0.009 |

| М   | 0 °         | 7°   | 0 °   | 7°    |

| P   | 5.80        | 6.20 | 0.228 | 0.244 |

| R   | 0.25        | 0.50 | 0.010 | 0.019 |

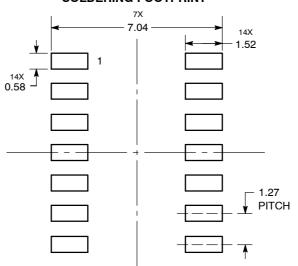

## **SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

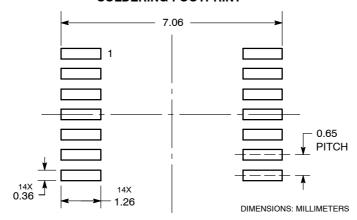

#### PACKAGE DIMENSIONS

## TSSOP-14 CASE 948G-01 **ISSUE B**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

5. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- REFERENCE ONLY.

7. DIMENSION A AND B ARE TO BE

| <del>DETERMINED AT DATUM PLANE -W</del> |        |        |           |       |  |

|-----------------------------------------|--------|--------|-----------|-------|--|

|                                         | MILLIN | IETERS | INC       | HES   |  |

| DIM                                     | MIN    | MAX    | MIN       | MAX   |  |

| Α                                       | 4.90   | 5.10   | 0.193     | 0.200 |  |

| В                                       | 4.30   | 4.50   | 0.169     | 0.177 |  |

| С                                       | -      | 1.20   |           | 0.047 |  |

| D                                       | 0.05   | 0.15   | 0.002     | 0.006 |  |

| F                                       | 0.50   | 0.75   | 0.020     | 0.030 |  |

| G                                       | 0.65   | BSC    | 0.026 BSC |       |  |

| Н                                       | 0.50   | 0.60   | 0.020     | 0.024 |  |

| J                                       | 0.09   | 0.20   | 0.004     | 0.008 |  |

| J1                                      | 0.09   | 0.16   | 0.004     | 0.006 |  |

| K                                       | 0.19   | 0.30   | 0.007     | 0.012 |  |

| K1                                      | 0.19   | 0.25   | 0.007     | 0.010 |  |

| L                                       | 6.40   | BSC    | 0.252     | BSC   |  |

| М                                       | 0°     | 8 °    | 0°        | 8 °   |  |

## **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5773–3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative