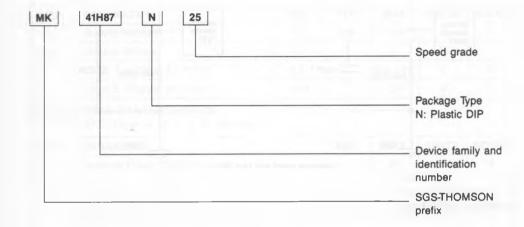

# SGS-THOMSON MICROELECTRONICS

### MK41H87(N)-25/35/45

### 64K × 1 CMOS STATIC RAM

ADVANCE INFORMATION

- 25, 35, AND 45 NS ADDRESS ACCESS TIME

- EQUAL ACCESS AND CYCLE TIMES

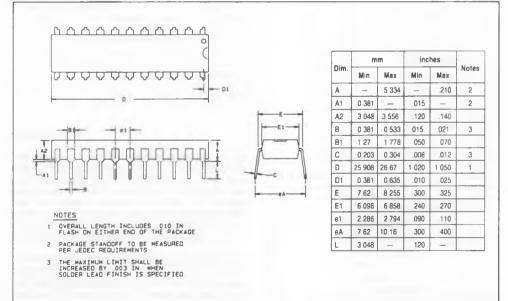

- 22-PIN, 300 MIL PLASTIC DIP

- ALL INPUTS AND OUTPUTS TTL COMPATIBLE. LOW CAPACITANCE, AND PROTECTED AGAINST STATIC DISCHARGE

- JEDEC STANDARD PINOUT

#### MK41H87 TRUTH TABLE

| ĈĒ | WE | Mode     | Q        | Power   |

|----|----|----------|----------|---------|

| н  | X  | Deselect | High Z   | Standby |

| L  | L  | Write    | High Z   | Active  |

| L  | н  | Read     | Data Out | Active  |

#### DESCRIPTION

The MK41H87 features fully static operation requiring no external clocks or timing strobes, and equal address access and cycle times. The MK41H87 requires only a single +5V ± 10 percent power supply, and it is fully TTL compatible.

The MK41H87 has a Chip Enable power down feature which automatically reduces power dissipation when the CE pin is brought inactive (high). Standby Power can be further reduced by holding the Address and CE pins at full supply rail voltages.

#### **OPERATIONS**

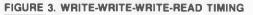

#### READ MODE

The MK41H87 is in the Read Mode whenever WE (Write Enable) is high and CE (Chip Enable) is low, providing a ripple-through access to data from one of 65.536 locations in the static storage array. Valid data will be available at the Data Output pin (Q) witbin tAA after the last address input signal is stable, providing that the CE access time is satisfied. If CE access time is not met, data access will be measured from the limiting parameter (t<sub>CA</sub>) rather

#### **PIN NAMES**

An - A15 - Address CE - Chip Enable WE - Write Enable GND - Ground

- V<sub>CC</sub> + 5 volts

- D Data In

- Q Data Out

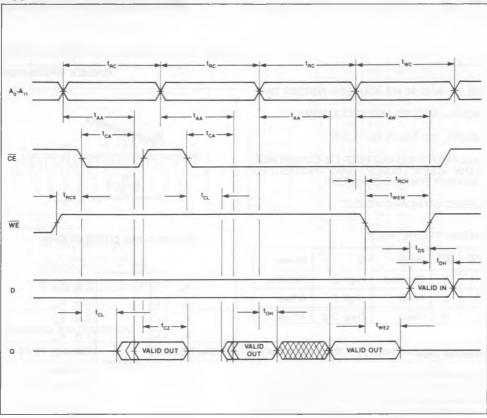

than the address. The state of the Data Output pin is controlled by the CE and WE control signals. The Q may be in an indeterminate state at t<sub>CL</sub>, but the Q will always have valid data at tAA.

MK41H87(N)-25/35/45

#### READ CYCLE TIMING AC ELECTRICAL CHARACTERISTICS $(0^{\circ}C \le T_A \le 70^{\circ}C)$ (V<sub>CC</sub> = 5.0 V ± 10 percent)

|                  |                          | MK41 | MK41H87-25 |     | H87-35 | MK41H87-45 |     |       |       |

|------------------|--------------------------|------|------------|-----|--------|------------|-----|-------|-------|

| SYM              | PARAMETER                | MIN  | MAX        | MIN | MAX    | MIN        | MAX | UNITS | NOTES |

| t <sub>RC</sub>  | Read Cycle Time          | 25   |            | 35  |        | 45         |     | ns    |       |

| t <sub>AA</sub>  | Address Access Time      |      | 25         |     | 35     |            | 45  | ns    | 1     |

| t <sub>CL</sub>  | Chip Enable to Low-Z     | 5    |            | 5   |        | 5          |     | ns    | 2     |

| t <sub>CA</sub>  | Chip Enable Access Time  |      | 25         |     | 35     |            | 45  | ns    | 1     |

| t <sub>RCS</sub> | Read Command Setup Time  | 0    |            | 0   |        | 0          |     | ns    |       |

| t <sub>RCH</sub> | Read Command Hold Time   | 0    |            | 0   |        | 0          |     | ns    |       |

| t <sub>он</sub>  | Valid Data Out Hold Time | 3    |            | 3   |        | 3          |     | ns    | 1     |

| tcz              | Chip Enable to High-Z    |      | 10         |     | 12     |            | 15  | ns    | 2     |

| twez             | Write Enable to High-Z   |      | 12         |     | 14     |            | 17  | ns    | 2     |

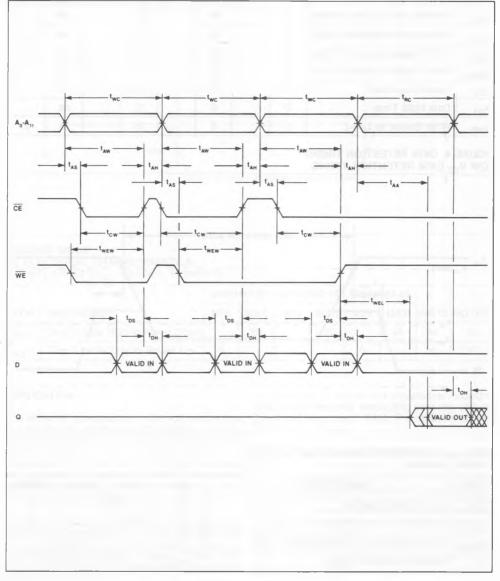

#### WRITE MODE

The MK41H87 is in the Write Mode whenever the WE and CE inputs are in the low state. CE or WE must be high during address transitions. Addresses must be held valid throughout a write cycle. The Write begins with the concurrence of a low on WE and CE. Therefore,  $t_{\rm AS}$  is referenced to the latter

occurring edge of  $\overline{CE}$  or  $\overline{WE}$ . If the output is enabled ( $\overline{CE}$  is low), then  $\overline{WE}$  will return the output to high impedance within t<sub>WEZ</sub> of its falling edge. Data-In must remain valid t<sub>DH</sub> after the rising edge of  $\overline{CE}$  or  $\overline{WE}$ .

#### WRITE CYCLE TIMING AC ELECTRICAL CHARACTERISTICS

$(0^{\circ}C \le T_A \le 70^{\circ}C) (V_{CC} = 5.0 \text{ V} \pm 10 \text{ percent})$

|                  |                                 | MK41H87-25 |     | MK41H87-35 |     | MK41H87-45 |     |       |       |

|------------------|---------------------------------|------------|-----|------------|-----|------------|-----|-------|-------|

| SYM              | PARAMETER                       | MIN        | MAX | MIN        | MAX | MIN        | MAX | UNITS | NOTES |

| twc              | Write Cycle Time                | 25         |     | 35         |     | 45         |     | ns    |       |

| t <sub>AS</sub>  | Address Setup Time              | 0          |     | 0          |     | 0          |     | ns    |       |

| t <sub>AW</sub>  | Address Valid to End of Write   | 20         |     | 30         |     | 40         |     | ns    |       |

| t <sub>AH</sub>  | Address Hold after End of Write | 0          |     | 0          |     | 0          |     | ns    |       |

| t <sub>cw</sub>  | Chip Enable to End of Write     | 20         |     | 30         |     | 40         |     | ns    |       |

| twew             | Write Enable to End of Write    | 20         |     | 25         |     | 30         |     | ns    |       |

| t <sub>DS</sub>  | Data Setup Time                 | 20         |     | 25         |     | 35         |     | ns    |       |

| t <sub>DH</sub>  | Data Hold Time                  | 0          |     | 0          |     | 0          |     | ns    |       |

| t <sub>WEL</sub> | Write Enable to Low-Z           | 5          |     | 5          |     | 5          |     | ns    | 2     |

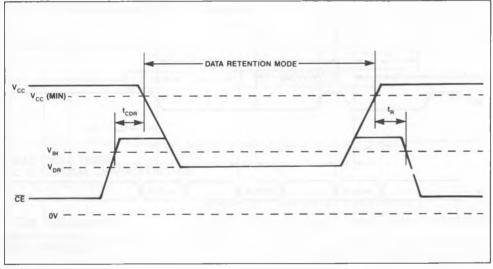

### FIGURE 4. DATA RETENTION TIMING LOW $V_{\rm CC}$ DATA RETENTION TIMING

## LOW V<sub>CC</sub> DATA RETENTION CHARACTERISTICS (0°C $\leq$ T\_A $\leq$ 70°C)

| SYM              | PARAMETERS                              | MIN             | MAX                   | UNIT | NOTES |

|------------------|-----------------------------------------|-----------------|-----------------------|------|-------|

| VDR              | V <sub>CC</sub> for Data Retention      | 2.0             | V <sub>CC</sub> (min) | V    | 6     |

| ICCDR            | Data Retention Power Supply Current     | -               | 500                   | μΑ   | 6     |

| 1 <sub>CDR</sub> | Chip Deselection to Data Retention Time | 0               |                       | ns   |       |

| t <sub>R</sub>   | Operation Recovery Time                 | t <sub>RC</sub> | -                     | ns   |       |

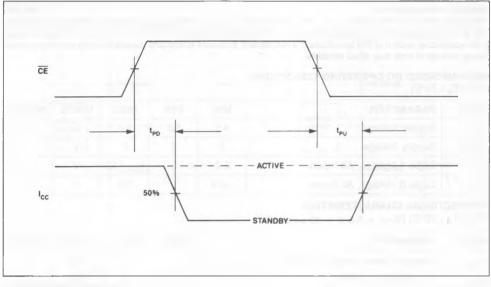

#### STANDBY MODE

The MK41H87 is in Standby Mode whenever  $\overline{CE}$  is held at or above V<sub>IH</sub>.

#### FIGURE 5. STANDBY MODE TIMING

#### STANDBY MODE AC ELECTRICAL CHARACTERISTICS

| $(0^{\circ}C \le I_A \le 70^{\circ}C) (V_{CC} = 5.0 \text{ V} \pm 10 \text{ percent}$ |

|---------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------|

|                 |                                | MK41 | 187-25 | MK41 | 187-35 | MK41H | 187-45 |       |       |

|-----------------|--------------------------------|------|--------|------|--------|-------|--------|-------|-------|

| SYM             | PARAMETER                      | MIN  | MAX    | MIN  | MAX    | MIN   | MAX    | UNITS | NOTES |

| t <sub>PD</sub> | Chip Enable High to Power Down |      | 25     |      | 35     |       | 45     | ns    | 10    |

| t <sub>PU</sub> | Chip Enable Low to Power Up    | 0    |        | 0    |        | 0     |        | ns    | 10    |

#### APPLICATION

The MK41H87 operates from a 5.0 volt supply. It is compatible with all standard TTL families on all inputs and outputs. The device should share a solid ground plane with any other devices interfaced with it, particularly TTL devices. Additionally, because the outputs can drive rail-to-rail into high impedance loads, the 41H87 can also interface to 5 volt CMOS on all inputs and outputs.

Since very high frequency current transients will be associated with the operation of the MK41H87, power line inductance must be minimized on the circuit board power distribution network. Power and ground trace gridding or separate power planes can be employed to reduce line inductance. Additionally, a high frequency decoupling capacitor should be placed next to each RAM. The capacitor should be 0.1  $\mu$ F or larger.

Though often times not thought of as such, the traces on a memory board are basically unterminated, low impedance transmission lines. As such they are subject to signal reflections manifested as noise, undershoots and excessive ringing. Series termination in close proximity to the TTL drivers can improve driver/signal path impedance matching. While experimentation most often proves to be the only practical approach to selection of series resistors, values in the range of 10 to 33 ohms often prove most suitable.

#### **ABSOLUTE MAXIMUM RATINGS**\*

| Voltage on any pin relative to GND                                                                             |

|----------------------------------------------------------------------------------------------------------------|

| Ambient Operating Temperature (T <sub>A</sub> )                                                                |

| Ambient Storage Temperature (Plastic)                                                                          |

| Ambient Storage Temperature (Ceramic)                                                                          |

| Total Device Power Dissipation                                                                                 |

| Output Current per Pin                                                                                         |

| *Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. |

This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$(0^{\circ}C \le T_A \le 70^{\circ}C)$

| SYM             | PARAMETER                   | MIN  | ТҮР | MAX                  | UNITS | NOTES |

|-----------------|-----------------------------|------|-----|----------------------|-------|-------|

| V <sub>CC</sub> | Supply Voltage              | 4.5  | 5.0 | 5.5                  | V     | 3     |

| GND             | Supply Voltage              | 0    | 0   | 0                    | V     |       |

| VIH             | Logic 1 Voltage, All Inputs | 2.2  |     | V <sub>CC</sub> +1.0 | V     | 3     |

| VIL             | Logic 0 Voltage, All Inputs | -0.3 |     | 0.8                  | V     | 3     |

#### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}C \le T_A \le 70^{\circ}C) (V_{CC} = 5.0 \text{ V} \pm 10 \text{ percent})$

| SYM                                                               | PARAMETER                                         | MIN | MAX | UNITS | NOTES |

|-------------------------------------------------------------------|---------------------------------------------------|-----|-----|-------|-------|

| I <sub>CC1</sub>                                                  | Average Power Supply Current                      |     | 70  | mA    | 4     |

| I <sub>CC2</sub> TTL Standby Current                              |                                                   |     | 8   | mA    | 5     |

| loca                                                              | CMOS Standby Current                              |     | 1.5 | mA    | 6     |

| I <sub>IL</sub>                                                   | Input Leakage Current (Any Input Pin)             | -1  | +1  | μΑ    | 7     |

| IOL                                                               | Output Leakage Current (Any Output Pin)           | -10 | +10 | μΑ    | 8     |

| V <sub>OH</sub> Output Logic 1 Voltage (I <sub>OUT</sub> = -4 mA) |                                                   | 2.4 |     | V     | 3     |

| VOL                                                               | Output Logic 0 Voltage (I <sub>OUT</sub> = +8 mA) |     | 0.4 | V     | 3     |

#### CAPACITANCE

$(T_A = 25 \,^{\circ}C, f = 1.0 \,\text{MHz})$

| SYM            | PARAMETER                 | ТҮР | MAX | UNITS | NOTES |

|----------------|---------------------------|-----|-----|-------|-------|

| C <sub>1</sub> | Capacitance on input pins | 4   | 5   | pF    | 9     |

| C <sub>2</sub> | Capacitance on DQ pins    | 8   | 10  | pF    | 5,9   |

#### NOTES

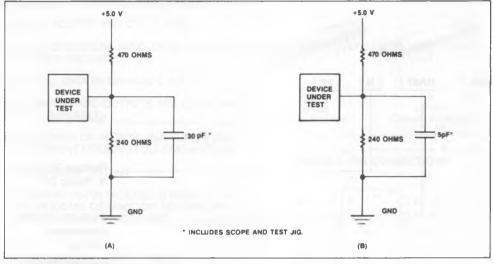

- 1. Measured with load shown in Figure 6(A).

- 2. Measured with load shown in Figure 6(B).

- 3. All voltages referenced to GND.

- 4.  $I_{CC1}$  is measured as the average AC current with  $V_{CC}$ =  $V_{CC}$  (max) and with the outputs open circuit. tcycle = min. duty cycle 100%.

- 5. CE = VIH, All Other Inputs = Don't Care.

- 7. Input leakage current specifications are valid for all V<sub>IN</sub> such that 0 V < V<sub>IN</sub> < V<sub>CC</sub>. Measured at V<sub>CC</sub> = V<sub>CC</sub> (max).

- 8. Output leakage current specifications are valid for all V<sub>OUT</sub> such that 0 V < V<sub>OUT</sub> < V<sub>CC</sub>,  $\overline{CE/CS} = V_{IH}$  and V<sub>CC</sub> in valid operating range.

- 9. Capacitances are sampled and not 100% tested.

- 10. Guaranteed, but not 100% tested.

#### AC TEST CONDITIONS

| Input Levels                                   | 0 V 0 |

|------------------------------------------------|-------|

| Transition Times                               |       |

| Input and Output Signal Timing Reference Level | 5 V   |

| Ambient Temperature                            | ာင    |

| V <sub>CC</sub>                                | ent   |

#### FIGURE 6. OUTPUT LOAD CIRCUITS

#### 22 PIN "N" PACKAGE

#### MK41H87(N)-25/35/45

#### ORDERING INFORMATION

| PART NUMBER | ACCESS TIME | PACKAGE TYPE               | TEMPERATURE RANGE |

|-------------|-------------|----------------------------|-------------------|

| MK41H87N-25 | 25 ns       | 22 pin 300 mil Plastic DIP | 0°C to 70°C       |

| MK41H87N-35 | 35 ns       | 22 pin 300 mil Plastic DIP | 0°C to 70°C       |

| MK41H87N-45 | 45 ns       | 22 pin 300 mil Plastic DIP | 0°C to 70°C       |