PRELIMINARY

## PROCESSED TO MIL-STD-883, METHOD 5004, CLASS B, 16,384 x 1-BIT STATIC RAM MKB4167(P)-870/885/80

## **FEATURES**

| □ -55 to +125° | C operating ter | nperature range |

|----------------|-----------------|-----------------|

|----------------|-----------------|-----------------|

☐ Industry standard 20 pin 300 mil DIP

□ Scaled POLY 5<sup>TM</sup> technology

□ Fully TTL compatible

□ Density upgrade over the 2147

☐ Chip select power down feature

☐ Access time equal to cycle time

| Part<br>Number | Access<br>Time | Cycle<br>Time | Active<br>Max | Standby<br>Max |

|----------------|----------------|---------------|---------------|----------------|

| MKB4167-870    | 70 ns          | 70 ns         | 660 mW        | 220 mW         |

| MKB4167-885    | 85 ns          | 85 ns         | 660 mW        | 220 mW         |

| MKB4167-80     | 100 ns         | 100 ns        | 660 mW        | 220 mW         |

#### DESCRIPTION

The MKB4167 is a high performance 16K x 1 fully static RAM suited for either high speed cache memories or for slower main memory applications. The low standby power allows maximum packing density with the JEDEC Type F chip carrier or the 300 mil wide DIP.

This static RAM offers a cycle time equal to its access time and has fully TTL compatible inputs and outputs resulting in a part that fits easily into a wide range of applications.

#### **DEVICE OPERATION**

The MKB4167 is a fully static Random Access Memory which accesses one of its 16,384 address locations based upon the value presented at its 14 address input pins. This power gated part will function in either a ripple through fashion when the Chip Select  $(\overline{CS})$  line is held active (low) or as a clocked part with the  $\overline{CS}$  selecting the device. When the  $\overline{CS}$  returns high the output is placed in a high impedance or

disabled mode and the power drops to a fraction of its active level.

A charge pump is employed on the MKB4167 giving the user two notable advantages. The function of the charge pump is to negatively bias the substrate giving sufficient operating margin internally which allows a single 5 V power supply to be used. Since the charge pump applies a negative

#### **PIN CONNECTIONS**

Figure 1

#### **TRUTH TABLE**

| CS | WE | Mode         | Output           | Power   |

|----|----|--------------|------------------|---------|

| Н  | х  | Not Selected | High Z           | Standby |

| L  | L  | Write        | High Z           | Active  |

| L  | Н  | Read         | D <sub>OUT</sub> | Active  |

#### **PIN NAMES**

| A <sub>0</sub> - A <sub>13</sub> | Address Inputs |

|----------------------------------|----------------|

| CS                               | Chip Select    |

| D <sub>IN</sub>                  | Data Input     |

| D <sub>OUT</sub>                 | Data Output    |

| V <sub>SS</sub>                  | Ground         |

|                                  | Power (+5 V)   |

| V <sub>CC</sub><br>WE            | Write Enable   |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to V <sub>SS</sub> | 2.0 V to +7 V  |

|------------------------------------------------|----------------|

| Operating temperature (T <sub>C</sub> )        | 55°C to +125°C |

| Storage temperature (Ambient)                  | 65°C to +150°C |

| DC output current                              |                |

| Power dissipation                              |                |

<sup>\*</sup>Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **RECOMMENDED DC OPERATING CONDITIONS<sup>1,10</sup>**

$(-55^{\circ}C \le T_C \le +125^{\circ}C)$

| SYM             | PARAMETER                    | MIN  | TYP | MAX                | UNITS | NOTES |

|-----------------|------------------------------|------|-----|--------------------|-------|-------|

| V <sub>cc</sub> | Supply Voltage               | 4.5  | 5.0 | 5.5                | V     | 1     |

| V <sub>SS</sub> | Supply Voltage               | 0    | 0   | 0                  | V     | 1     |

| V <sub>IH</sub> | Logic "1" Voltage All Inputs | 2.0  | _   | V <sub>CC</sub> +1 | V     | 1     |

| V <sub>IL</sub> | Logic "0" Voltage All Inputs | -2.5 | -   | 0.8                | V     | 1     |

## DC ELECTRICAL CHARACTERISTICS<sup>1,10</sup>

$(-55^{\circ}C \le T_C \le +125^{\circ}C) (V_{CC} = 5.0 \text{ V} \pm 10\%)$

|                 |                                                              | MKB41 | 67-870 | MKB4 | 167-885 | MKB4167-80 |     |       |       |

|-----------------|--------------------------------------------------------------|-------|--------|------|---------|------------|-----|-------|-------|

| SYM             | PARAMETER                                                    | MIN   | MAX    | MIN  | MAX     | MIN        | MAX | UNITS | NOTES |

| I <sub>cc</sub> | Operating Current AC (t <sub>RC</sub> = t <sub>RC</sub> min) |       | 120    |      | 120     |            | 120 | mA    | 9     |

| I <sub>cc</sub> | Operating Current (t <sub>C</sub> = 125°C)                   |       | 90     |      | 90      |            | 90  | mA    | 9,11  |

| I <sub>SB</sub> | Standby Current (CS ≥ V <sub>IH</sub> )                      |       | 40     |      | 40      |            | 40  | mA    |       |

| I <sub>L</sub>  | Input Leakage Current (Any Input)                            |       | 10     |      | 10      |            | 10  | μА    | 3,12  |

| I <sub>OL</sub> | Output Leakage Current                                       |       | 50     |      | 50      |            | 50  | μА    | 2     |

| V <sub>OH</sub> | Output Logic "1" Voltage I <sub>OUT</sub> = -4 mA            | 2.4   |        | 2.4  |         | 2.4        |     | ٧     |       |

| V <sub>OL</sub> | Output Logic "0"<br>Voltage I <sub>OUT</sub> = 8 mA          |       | 0.4    |      | 0.4     |            | 0.4 | ٧     |       |

## RECOMMENDED AC OPERATING CONDITIONS AND ELECTRICAL CHARACTERISTICS<sup>10</sup>

$(-55^{\circ}\text{C} \le \text{T}_{\text{C}} \le +125^{\circ}\text{C}) \text{ (V}_{\text{CC}} = 5.0 \text{ V} \pm 10\%)$

## **READ CYCLE TIMING**

|                  |                                   | MKB4167-870 MKB4167-885 |     |     |     | MKB4167-80 |     |       |       |

|------------------|-----------------------------------|-------------------------|-----|-----|-----|------------|-----|-------|-------|

| SYM              | PARAMETER                         | MIN                     | MAX | MIN | MAX | MIN        | MAX | UNITS | NOTES |

| t <sub>RC</sub>  | Read Cycle Time                   | 70                      |     | 85  |     | 100        |     | ns    |       |

| t <sub>AA</sub>  | Address Access Time               |                         | 70  |     | 85  |            | 100 | ns    | 6     |

| t <sub>CSA</sub> | Chip Select Access Time           |                         | 70  |     | 85  |            | 100 | ns    | 6     |

| t <sub>OH</sub>  | Output Hold From Address Change   | 5                       |     | 5   |     | 5          |     | ns    |       |

| t <sub>LZ</sub>  | Chip Selection to Output Low Z    | 10                      |     | 10  |     | 10         |     | ns    |       |

| t <sub>HZ</sub>  | Chip Deselection to Output High Z | 0                       | 30  | 0   | 35  | 0          | 40  | ns    | 7     |

| t <sub>PU</sub>  | Chip Selection to Power Up Time   | 0                       |     | 0   |     | 0          |     | ns    |       |

| t <sub>PD</sub>  | Chip Deselection to Power Down    |                         | 50  |     | 60  |            | 70  | ns    |       |

#### WRITE CYCLE TIMING

| ·                |                                        | MKB41 | 167-870 | MKB41 | 67-885 | MKB4 | 167-80 |       |       |

|------------------|----------------------------------------|-------|---------|-------|--------|------|--------|-------|-------|

| SYM              | PARAMETER                              | MIN   | MAX     | MIN   | MAX    | MIN  | MAX    | UNITS | NOTES |

| t <sub>WC</sub>  | Write Cycle Time                       | 70    |         | 85    |        | 100  |        | ns    |       |

| t <sub>CW</sub>  | Chip Select to End of Write            | 60    |         | 75    |        | 85   |        | ns    |       |

| t <sub>AW</sub>  | Address Valid to End of Write          | 60    |         | 75    |        | 85   |        | ns    |       |

| t <sub>AS1</sub> | Address Setup Time WE Controlled Cycle | 10    |         | 10    |        | 10   |        | ns    |       |

| t <sub>AS2</sub> | Address Setup Time CS Controlled Cycle | 0     |         | 0     |        | 0    |        | ns    |       |

| t <sub>WP</sub>  | Write Pulse Width                      | 40    |         | 55    |        | 65   |        | ns    |       |

| t <sub>WR</sub>  | Write Recovery Time                    | 0     |         | 0     |        | 0    |        | ns    |       |

| t <sub>DW</sub>  | Data Valid to End of Write             | 30    |         | 35    |        | 40   |        | ns    |       |

| t <sub>DH</sub>  | Data Hold Time                         | 10    |         | 10    |        | 10   |        | ns    |       |

| t <sub>WZ</sub>  | Write Enable to Output in High Z       | 0     | 35      | 0     | 45     | 0    | 50     | ns    | 7     |

| t <sub>OW</sub>  | Output Active From End of Write        | 0     |         | 0     |        | 0    |        | ns    |       |

## CAPACITANCE<sup>1</sup>

(–55°C  $\leq$   $T_{C}$   $\leq$  +125°C) (V  $_{CC}$  = +5.0 V  $\pm$  10%)

| SYM              | PARAMETER          | MAX | UNITS | NOTES |

|------------------|--------------------|-----|-------|-------|

| C <sub>IN</sub>  | Input Capacitance  | 5   | pF    | 8     |

| C <sub>OUT</sub> | Output Capacitance | 6   | pF    | 8,9   |

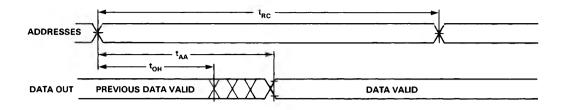

## **READ CYCLE NUMBER 1 (5,6)**

Figure 2

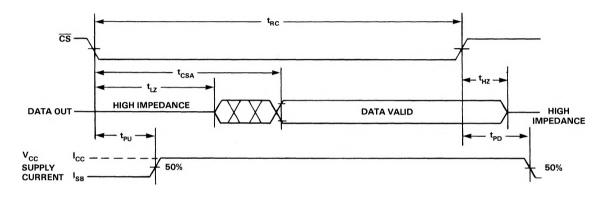

## **READ CYCLE NUMBER 2 (5,7)**

Figure 3

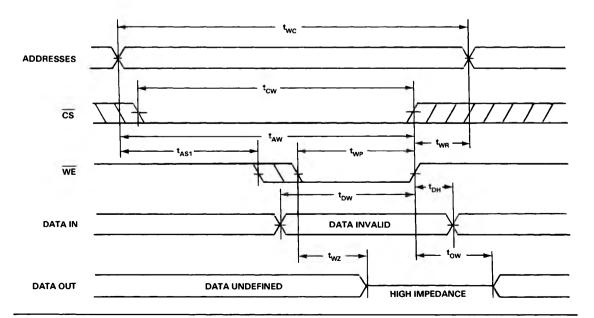

# WRITE CYCLE NUMBER 1 (WE CONTROLLED)

Figure 4

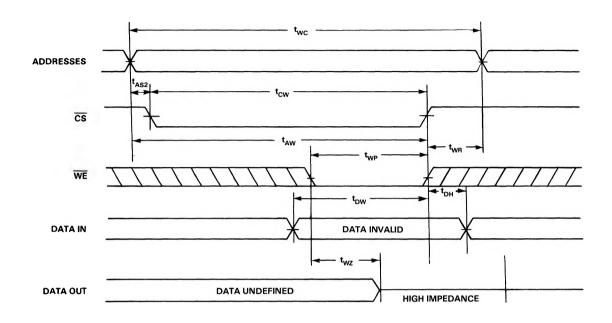

## **WRITE CYCLE NUMBER 2** (CS CONTROLLED)

Figure 5

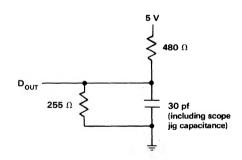

## A.C. TEST CONDITIONS

Input Levels ...... 0 V to 3.0 V Transition Times......5 ns Input timing reference level ......1.5 V Output timing reference levels....0.8 V - 2.0 V Output load ......See figure

#### **OUTPUT LOAD**

#### NOTES:

- 1. All voltages referenced to  $V_{SS}$ . 2.  $\overline{CS} = V_{IH}$ ,  $V_{CC} = MAX$ ,  $V_{OUT} = V_{SS}$  to 4.5 V. 3.  $V_{CC} = MAX$ . Also  $0 \le V_{IN} \le V_{CC}$ .

- 4. tHZ and tWZ defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 5. WE is high for Read Cycles.

- 6. Device is continuously selected CS ≤ V<sub>IL</sub>.

7. Addresses valid prior to or coincident with CS transition low.

- 8. Effective capacitance calculated from the equation C = I $\Delta t$  with  $\Delta V$  = 3 volts  $\overline{\Delta V}$

- and power supplies at nominal levels. This parameter is sample tested only

- 9. Output buffer is deselected.

- 10. A minimum of 2 ms is required following the application of  $V_{CC}$  (+5 V) before proper device operation is achieved.

- 11. Power consumption decreases with increasing temperature.

bias to the substrate, it also allows large negative values to exist on the inputs without the fear of damaging the device. Large negative spikes have other drawbacks though, as discussed in the application section. To allow the charge pump sufficient start up time, 2 ms is required following the application of  $V_{\rm CC}$  prior to device operation.

### Read Cycle

A read cycle occurs whenever WE is high and the part is selected. Access time is measured from either the falling edge of CS or from the stable address.

The read cycle number 1 waveform shown in Figure 2 demonstrates the fully static operation of this part when  $\overline{\text{CS}}$  is held active. The output retains the previous valid data for  $t_{\text{OH}}$ , after which it is indeterminate until  $t_{\text{AA}}$ . The output will remain valid until there is a transition on the address inputs and another read cycle occurs.

Operation as shown in read cycle 2 (Figure 3) will take advantage of the power gating feature. If the addresses become stable prior to or as  $\overline{\text{CS}}$  falls operation is as shown for read cycle 2. The output changes from a high impedance mode after  $t_{\text{LZ}}$  and becomes indeterminate until  $t_{\text{CEA}}$  when it is valid.

Once the cycle is ended by the rising edge of  $\overline{\text{CS}}$ , the output becomes undefined. T<sub>PD</sub> later the part is in the standby mode.

#### Write Cycle

A write cycle is initiated by the later of  $\overline{CS}$  or  $\overline{WE}$  going low and is terminated by the rising edge of  $\overline{CS}$  or  $\overline{WE}$ . The output remains in a high impedance mode during a write cycle.

A write enable ( $\overline{WE}$ ) controlled write cycle is shown in Figure 4. The addresses must be valid for  $t_{ASI}$  prior to the falling edge of  $\overline{WE}$  and remain valid for  $t_{WR}$  after  $\overline{WE}$  has gone high. If these times are not met, the contents of other cells may be altered. The data in valid is referenced to the rising edge of  $\overline{WE}$ . Once  $\overline{WE}$  goes high, the output again goes active and a read cycle may begin.

A  $\overline{\text{CS}}$  controlled write cycle is shown in Figure 5. In this cycle, timing is referred to the rising edge of  $\overline{\text{CS}}$ , and both the addresses and  $\overline{\text{WE}}$  may change following that time. Note that the data must remain valid for  $t_{DH}$ .

## **POWER SUPPLY GRIDDING**

All high speed NMOS devices share the trait that their current consumption is composed of high frequency transients. Proper device operation depends on both the use of decoupling capacitors and low impedance printed circuit board paths for both  $V_{CC}$  and  $V_{SS}$ .

When a designer has the ability to take advantage of multilayer board construction for separate  $V_{SS}$  and  $V_{CC}$  power planes on optimal low inductance path for power distribution can be had. If a two layer approach is chosen, some care in the design to fully grid  $V_{CC}$  and  $V_{SS}$  on both sides of the board will give quite satisfactory results. Regardless of the approach taken, a high frequency decoupling capacitor (0.1  $\mu$ f) should be placed next to each device with larger tantalum capacitors for each row of devices. These efforts will help reduce the ringing on  $V_{CC}$  and  $V_{SS}$  due to the long inductive path between the power supply and the device.

#### LINE TERMINATION

To take advantage of high speed memories, high speed TTL drivers are often used. Unfortunately, a printed circuit board trace terminating into a MOS input behaves line an unterminated transmission line. Ringing is the natural result with the potentially destructive voltage levels and noise induced into neighboring PC traces. While the MKB4167 with its charge pump can withstand –2.0 V on any input, such large negative spikes result in a noisy board.

Series termination is a method to dampen these reflections in an easy to implement fashion. By placing a 30  $\Omega$  to 5  $\Omega$  resistor at the TTL driver's output, the effective impedance of the driver has been raised to more closely match the impedance of the PC trace. These printed circuit board design ideas are explained in more detail in the Memory Data Book And Designers Guide.