# MM54C929/MM74C929, MM54C930/MM74C930 1024-Bit Static Silicon Gate CMOS RAMs

#### **General Description**

The MM54C929/MM74C929 and the MM54C930/ MM74C930 1024 x 1 random access read/write memories are manufactured using silicon-gate CMOS technology. These RAMs are specifically designed to operate from standard 54/74 TTL power supplies; all inputs and outputs are TTL compatible. Data output is the same polarity as data input. Internal latches store the address inputs and data output. Chip select input CS1 serves as a chip strobe, controlling address and data latching. The Data-In and Data-Out terminals can be tied together for common I/O applications. Complete address decoding, 3-chip select functions (MM54C930/MM74C930) and TRI-STATE® output allow easy memory expansion and organization. The MM54C929/MM74C929 differs from the MM54C930/MM74C930 only in that CS1, CS2 and CS3 are internally connected together, providing a single chip-select input CS.

Versatility, high speed, and low power make these RAMs ideal elements for use in many microprocessor, minicomputer and main-frame-memory applications.

#### **Features**

- Fast access—250 ns max

- TRI-STATE outputs

- Low power—10 µA max standby

- On-chip registers

- Single 5V supply

- Inputs and output TTL compatible

- Data retained with V<sub>CC</sub> as low as 2V

- Can be operated common I/O

#### **Connection Diagrams**

# Dual-In-Line Package | Total | Total

TOP VIEW

# Logic Symbols

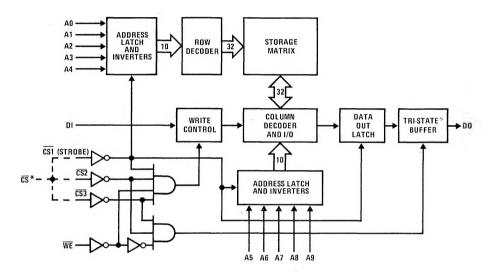

#### **Functional Description**

Address inputs are clocked into the input latches by the falling edge of chip strobe CS1; set-up and hold times must be observed on these input signals (see timing diagram). The true and complement address information is fed to the row and column decoders which select one of the 1024-bit locations. The addressed bit is fed, via a sense amplifier, to the output register and TRI-STATE® buffer. The information is latched into the output register on the rising edge of chip strobe CS1. The output is in a high impedance state when the chip is not selected (CS2 or CS3 high) or when writing (WE low). Output buffer control is independent of chip strobe CS1.

#### Reduced-Voltage Operation

These memories will retain data with reduced V<sub>CC</sub> and hence are useful for battery-backup data storage. Certain precautions must be observed as V<sub>CC</sub> is reduced: (1) input voltages must remain between the V<sub>CC</sub> and ground of the RAM or supply latch-up can occur, (2) WRITE mode must be avoided, (3) during power-up of V<sub>CC</sub>, strobe ( $\overline{\text{CS}}$  for the MM74C929 and  $\overline{\text{CS1}}$  for the MM74C930) logic state must be maintained (either GND or V<sub>CC</sub>) while address control lines stabilize.

## Logic Diagram\*

<sup>\*</sup>The MM74C930 has 3 chip selects CS1, CS2 and CS3. The MM74C929 has these internally connected together providing a single chip select input CS.

FIGURE 1

#### **Absolute Maximum Ratings**

Supply Voltage, VCC Voltage at Any Pin -0.3V to  $V_{CC} + 0.3V$ -65°C to +150°C Storage Temperature Range

Operating Temperature Range MM54C929, MM54C930

MM74C929, MM74C930 -40°C to +85°C MM74C929-3, MM74C930-3 0°C to +70°C Package Dissipation 500 mW

Lead Temperature (Soldering 10 seconds)

DC Electrical Characteristics  $V_{CC} = 5V \pm 10\%$ ,  $T_A = Operating Range$ , unless otherwise noted

300° C

-55°C to +125°C

| SYMBOL           | PARAMETER                          | CONDITIONS                                         |                      | MM54C929,<br>MM54C930 |                      | MM74C929,<br>MM74C930 |                      | MM74C929-3,<br>MM74C930-3<br>(NOTE 1) |    |

|------------------|------------------------------------|----------------------------------------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|---------------------------------------|----|

|                  |                                    |                                                    | MIN                  | MAX                   | MłN                  | MAX                   | MIN                  | MAX                                   |    |

| VIH              | Logical "1" Input Voltage          |                                                    | V <sub>CC</sub> -2.0 | Vcc                   | V <sub>CC</sub> -2.0 | Vcс                   | V <sub>CC</sub> -2.0 | vcc                                   | v  |

| VIL              | Logical "0" Input Voltage          |                                                    | 0                    | 0.8                   | 0                    | 0.8                   | 0.                   | 8.0                                   | v  |

| V <sub>OH1</sub> | Logical "1" Output Voltage         | IOH = 1 mA                                         | 2.4                  |                       | 2.4                  | - 0                   | 2.4                  |                                       | v  |

| V <sub>OH2</sub> | Logical "1" Output Voltage         | I <sub>OUT</sub> = 0                               | V <sub>CC</sub> -0.1 |                       | V <sub>CC</sub> -0.1 |                       | V <sub>CC</sub> -0.1 |                                       | v  |

| V <sub>OL1</sub> | Logical "0" Output Voltage         | IOL = 2.0 mA                                       |                      | 0.4                   |                      | 0.4                   |                      | 0.4                                   | v  |

| V <sub>OL2</sub> | Logical "0" Output Voltage         | I <sub>OUT</sub> = 0                               |                      | 0.01                  |                      | 0.01                  | 1                    | 0.01                                  | v  |

| IIL              | Input Leakage                      | $0V \le V_{IN} \le V_{CC}$                         | -1.0                 | 1.0                   | -1.0                 | 1.0                   | -1.0                 | 1.0                                   | μΑ |

| 10               | Output Leakage                     | $0V \le V_O \le V_{CC}$ , (Note 2)                 | -1.0                 | 1.0                   | -1.0                 | 1.0                   | -1.0                 | 1.0                                   | μΑ |

| · Icc            | Supply Leakage Current             | $V_{IN} = V_{CC}$ , $V_{O} = 0V$                   |                      | 20                    |                      | 10                    |                      | 100                                   | μΑ |

| $v_{DR}$         | V <sub>CC</sub> for Data Retention | (Note 3)                                           | 2.0                  |                       | 2.0                  |                       | 2.0                  |                                       | v  |

| IDR              | ICC for Data Retention             | $V_{CC} = 2V, T_A = 25^{\circ}C, (Note 2)^{\circ}$ | *                    | 0.01                  |                      | 0.01                  |                      | 0.1                                   | μΑ |

|                  |                                    |                                                    |                      | (typ)                 |                      | (typ)                 |                      | (typ)                                 | L  |

Note 1:  $V_{CC} = 5V \pm 5\%$ . Note 2:  $\overline{CS2} = \overline{CS3} = V_{CC}$  or  $\overline{CS} = V_{CC}$ . Note 3:  $\overline{CS2}$  or  $\overline{CS3}$  or  $\overline{CS} = V_{CC} - 2V$  or = 2V, whichever is greater.

## AC Electrical Characteristics V<sub>CC</sub> = 5V ±10%, T<sub>A</sub> = Operating Range, unless otherwise noted

| SYMBOL               | PARAMETER                      | MM54C929,<br>MM54C930 |     | MM74C929,<br>MM74C930 |     | MM74C929-3,<br>MM74C930-3<br>(NOTE 1) |     | UNITS |

|----------------------|--------------------------------|-----------------------|-----|-----------------------|-----|---------------------------------------|-----|-------|

|                      |                                | MIN                   | MAX | MIN                   | MAX | MIN                                   | MAX |       |

| tC                   | Cycle Time                     | 290                   |     | 255                   |     | 330                                   |     | ns    |

| tACC                 | Access Time From Address       |                       | 265 |                       | 240 |                                       | 315 | ns    |

| tACS,tACS1           | Access Time From CS, CS1       |                       | 250 |                       | 225 |                                       | 300 | ns    |

| tAS                  | Address Set-Up Time            | 15                    |     | 15                    |     | 15                                    |     | ns    |

| tAH                  | Address Hold Time              | 50                    |     | 50                    |     | 50                                    |     | ns    |

| tOE                  | Output Enable Time             |                       | 150 |                       | 130 |                                       | 130 | ns    |

| tOD                  | Output Disable Time            |                       | 150 |                       | 130 |                                       | 130 | ns    |

| tCS,tCS1<br>(Note 4) | CS, CS1 Pulse Width (Negative) | 150                   |     | 130                   |     | 165                                   |     | ns    |

| tCS,tCS1             | CS, CS1 Pulse Width (Positive) | 140                   |     | 125                   |     | 165                                   |     | ns    |

| twp                  | Write Pulse Width (Negative)   | 150                   |     | 130                   |     | 165                                   |     | ns    |

| tDS                  | Data Set-Up Time, (Note 5)     | 150                   |     | 140                   |     | 140                                   |     | ns    |

| tDH                  | Data Hold Time, (Note 5)       | 0                     |     | 0                     |     | 0                                     |     | ns    |

Note 4: Greater than minimum CS pulse width must be used when reading data from the MM54C929/MM74C929 to ensure that output TRI-STATING does not occur before data becomes valid. Writing has no such limitation.

Note 5: tos and toh are referenced to the low-to-high transition of CS1 or CS2 or CS3 or WE, whichever switches first, for the MM54C930/ MM74C930 and are referenced to the CS or WE low-to-high transition, whichever switches first, for the MM54C929/MM74C929.

## Capacitance (Note 6)

| SYI | MBOL | PARAMETER               | CONDITIONS                                            | MIN | MAX | UNITS |

|-----|------|-------------------------|-------------------------------------------------------|-----|-----|-------|

|     | CIN  | Input Capacitance       | V <sub>IN</sub> = 0, f = 1 MHz, T <sub>A</sub> = 25°C | 4   | 7   | ρF    |

|     | CO   | Output Capacitance      | V <sub>IN</sub> = 0, f = 1 MHz, T <sub>A</sub> = 25°C | 6   | 9   | pF    |

|     | CCS  | Chip Select Capacitance | MM54C929/MM74C929, MM74C929-3                         | 8   | 12  | pF    |

Note 6: Capacitance maximum is guaranteed by periodic testing.

#### **Truth Tables**

#### MM54C929/MM74C929

| cs | WE | DI | FUNCTION                        |

|----|----|----|---------------------------------|

| 1  | Х  | Х  | Output in Hi-Z State            |

| ×  | 0  | ×  | Output in Hi-Z State            |

| 0  | 0  | 0  | Write "0," Output in Hi-Z State |

| 0  | 0  | 1  | Write "1," Output in Hi-Z State |

| 0  | 1  | X  | Read Data, Output Enabled       |

X = Don't care

#### MM54C930/MM74C930

| CS1 | CS2 | CS3 | WE | DI | FUNCTION                        |

|-----|-----|-----|----|----|---------------------------------|

| ×   | 1   | Х   | X  | Х  | Output in Hi-Z State            |

| ×   | ×   | 1   | ×  | ×  | Output in Hi-Z State            |

| ×   | ×   | ×   | 0  | ×  | Output in Hi-Z State            |

| 0   | 0   | 0   | 0  | 0  | Write "0," Output in Hi-Z State |

| 0   | 0   | 0   | 0  | 1  | Write "1," Output in Hi-Z State |

| 0   | 0   | 0   | 1  | ×  | Read Data, Output Enabled       |

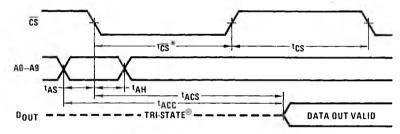

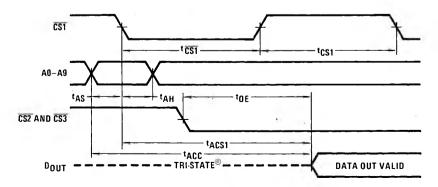

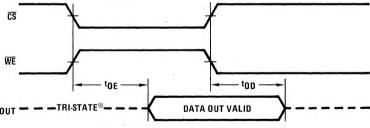

## **Switching Time Waveforms**

<sup>\*</sup>Greater than minimum  $\overline{\text{CS}}$  pulse width must be used when reading data from the MM54C929/MM74C929 to ensure that output TRI-STATING does not occur before data becomes valid. Writing has no such limitation, (Figure 4a).

FIGURE 2a. MM54C929/MM74C929 Read Cycle

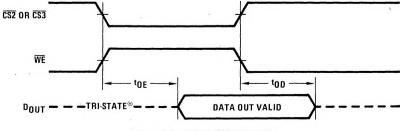

FIGURE 2b. MM54C930/MM74C930 Read Cycle

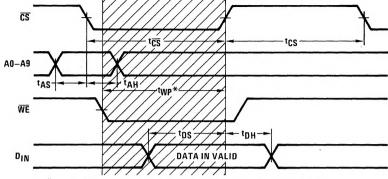

# Switching Time Waveforms (Continued)

<sup>\*</sup>twp (the Write Pulse width) is the time  $\overline{\text{CS}}$  and  $\overline{\text{WE}}$  are coincidentally low

FIGURE 3a. MM54C929/MM74C929 Write Cycle

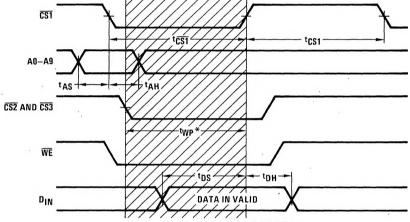

$<sup>{}^*</sup>t_{WP}$  (the Write Pulse width) is the time  $\overline{\text{CS1}}$ ,  $\overline{\text{CS2}}$ ,  $\overline{\text{CS3}}$  and  $\overline{\text{WE}}$  are coincidentally low

FIGURE 3b. MM54C930/MM74C930 Write Cycle

FIGURE 4a. MM54C929/MM74C929

FIGURE 4b. MM54C930/MM74C930

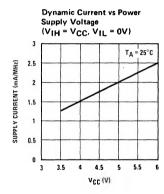

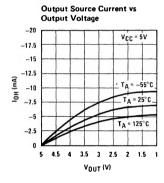

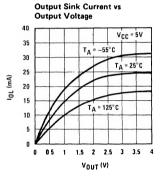

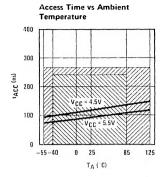

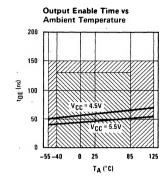

## Typical Performance Characteristics

Data-In Hold Time vs

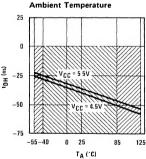

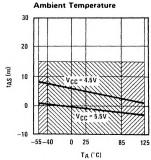

Address Hold Time vs Ambient Temperature

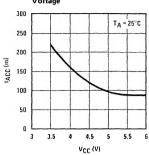

Access Time vs Power Supply Voltage

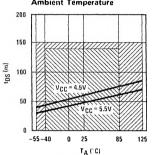

Data-In Set-Up Time vs Ambient Temperature

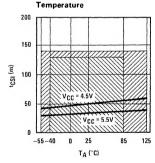

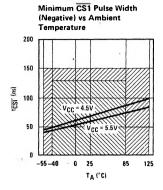

Minimum CSI Pulse Width (Positive) vs Ambient

Address Set-Up Time vs

# Typical Performance Characteristics (Continued)

Test Limit MM54C929, MM54C930

Test Limit MM74C929, MM74C930