# **Monolithic Diode Arrays Surface Mount Diode Arrays**

These diode arrays are multiple diode junctions fabricated by a planar process and mounted in integrated circuit packages for use in high-current, fast-switching core-driver applications. These arrays offer many of the advantages of integrated circuits such as high-density packaging and improved reliability. These advantages result from such factors as fewer glass-to-metal seals.

- Designed for Use in Computers and Peripheral Equipment

- Applications Include:

**Magnetic Cores** Thin-Film Memories Plated-Wire Memories

**Decoding or Encoding Applications**

#### **MAXIMUM RATINGS**

| Rating                            | Symbol           | Value       | Unit        |

|-----------------------------------|------------------|-------------|-------------|

| Peak Reverse Voltage              | V <sub>RM</sub>  | 50          | Vdc         |

| Steady-State Reverse Voltage      | v <sub>R</sub>   | 50          | Vdc         |

| Peak Forward Current 25°C         | IFM              | 500         | mAdc        |

| Continuous Forward Current        | lF               | 400         | mAdc        |

| Power Dissipation Derating Factor | PD               | 500<br>4.0  | mW<br>mW/°C |

| Operating Temperature             | TA               | -65 to +150 | °C          |

| Storage Temperature Range         | T <sub>stq</sub> | -65 to +150 | °C          |

**MMAD130 MMAD1103** MMAD1105 **MMAD1107** MMAD1109

**SO-14 PIN DIAGRAM**

Thermal Clad is a trademark of the Bergquist Company

REV 1

6367255 0090628 730 ■

© Motorola, Inc. 1997

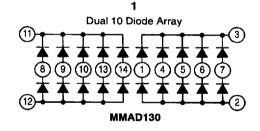

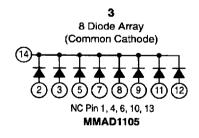

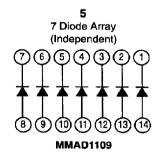

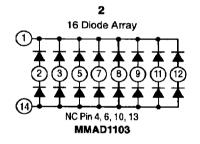

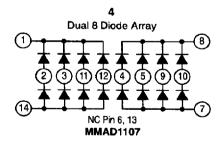

| Device Description |                              | Diagram |  |

|--------------------|------------------------------|---------|--|

| MMAD130            | Dual 10 Diode Array          | 1       |  |

| MMAD1103           | 16 Diode Array               | 2       |  |

| MMAD1105           | 8 Diode Array Common Cathode | 3       |  |

| MMAD1107           | Dual 8 Diode Array           | 4       |  |

| MMAD1109           | 7 Diode Array                | 5       |  |

#### ELECTRICAL CHARACTERISTICS (@ 25°C Free-Air Temperature)

| Characteristic                                                         |                   | Limit  |            |              |

|------------------------------------------------------------------------|-------------------|--------|------------|--------------|

|                                                                        | Symbol            | Min    | Max        | Unit         |

| Reverse Breakdown Voltage <sup>(1)</sup><br>(I <sub>R</sub> = 10 μAdc) | V <sub>(BR)</sub> | 50     |            | Vdc          |

| Static Reverse Current (V <sub>R</sub> = 40 Vdc)                       | l <sub>R</sub>    | _      | 0.1        | μ <b>Adc</b> |

| Static Forward Voltage (IF = 100 mAdc) (IF = 500 mAdc)(2)              | VF                | -<br>- | 1.2<br>1.6 | Vdc          |

| Peak Forward Voltage(3) (IF = 500 mAdc)                                | VFM               | _      | 5.0        | Vdc          |

### SWITCHING CHARACTERISTICS (@ 25°C Free-Air Temperature)

| Characteristic                                                                     | Symbol          | Typical Value | Unit |

|------------------------------------------------------------------------------------|-----------------|---------------|------|

| Forward Recovery Time (IF = 500 mAdc)                                              | <sup>t</sup> fr | 20            | ns   |

| Reverse Recovery Time (IF = 200 mA, IRM = 200 mA, RL = 100 $\Omega$ , Irr = 20 mA) | t <sub>rr</sub> | 8.0           | ns   |

#### NOTES:

- 1. This parameter must be measured using pulse techniques. PW = 100  $\mu$ s, duty cycle  $\leq$  20%.

- 2. This parameter is measured using pulse techniques. PW = 300 μs, duty cycle ≤ 2.0%. Read time is 90 μs from the leading edge of the pulse.

- 3. The initial instantaneous value is measured using pulse techniques. PW = 150 ns, duty cycle ≤ 2.0%, pulse rise time ≤ 10 ns. The total capacitance shunting the diode is 19 pF maximum and the equipment bandwidth is 80 MHz.

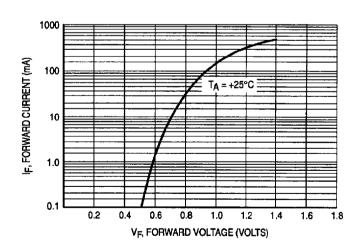

Figure 1. Typical Characteristics Static Forward Voltage

**■** 6367255 0090629 677 **■**

#### **TEST PROCEDURE FOR MULTIPLE DIODES**

#### 1.0. REVERSE BIAS TESTING

#### 1.1. LEAKAGE

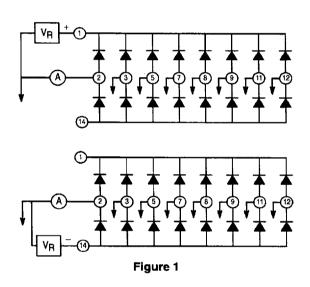

Regardless of device configuration type, when testing any reverse bias condition, the forcing power supply must be applied only to the uncommon terminal of the pair. As in Figure 1, this would be pins 1 and 14. This can be referred as the high side of the test circuit. The low side of the test circuit must be connected to the common terminal of the pair which in most testers is where the current measurement is taken. This method is used to eliminate the possibility of degrading the diode in that pair which is not under test. Diode arrays with multiple pairs such as the MMAD1103, also have leakage paths in the die between common terminals of the pairs. To isolate the device under test so that the leakage from the other pairs in the package do not affect the test result, the leakage current from the common terminals of the pairs not under test must be shunted to measurement common. Figure 1 shows the test configuration for both of these cases.

#### 1.2. BREAKDOWN

It is not recommended to test breakdown on these devices due to the possibility of degrading the device. Breakdown may be checked on a curve tracer but extreme caution should be used.

#### 2.0. FORWARD BIAS TESTING

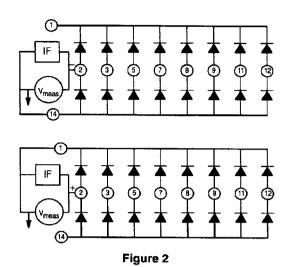

Diode arrays are designed with the pairs in parallel; therefore, care must be taken to prevent the other diodes in the array from affecting the measured value of the diode under test. Figure 2 illustrates the proper technique to measure only the correct value of the diode under test.

#### 2.1. KELVIN CONNECTION

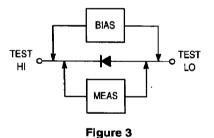

To achieve the best possible accuracy when testing bias currents over 10 mA, Kelvin connection to the leads of the device under test is mandatory. True Kelvin connection dictates that two test connections are made directly to the leads of the device. One is for power which is the bias supply, and the other is for sense which is for the measurement circuit. Kelvin connections are used to eliminate the effects of the connection resistance between the lead of the device and the contacts of the test handler and/or hand fixture. Figure 3 is an example of Kelvin connection.

#### 2.2. PULSE TESTING

When testing bias currents over 10 mA, pulse testing should be used to minimize thermal drift of the measured value. The pulse width of a pulse test is approximately 300  $\mu s$  to 380  $\mu s$ .

#### 3.0. TESTING PROTOCOL

#### 3.1. TEST TYPES

When testing in sequence all of the electrical characteristics, all reverse bias conditions should be tested before the forward bias conditions are tested.

## 3.2. BIASING MAGNITUDES

Tests of the same test type should be grouped together with the bias conditions in ascending order. For example:

VF @ 10 mA < 0.6 V

VF @ 50 mA < 0.8 V

VF @ 100 mA < 1 V

VF @ 500 mA < 1.5 V

**■ 6367255 0090630 399** |

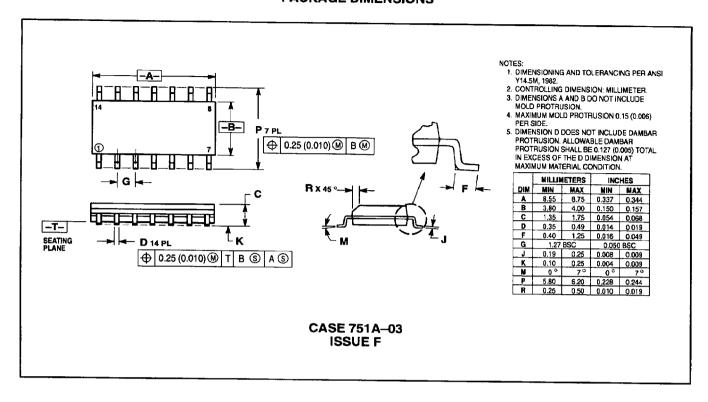

# INFORMATION FOR USING THE SO-14 SURFACE MOUNT PACKAGE

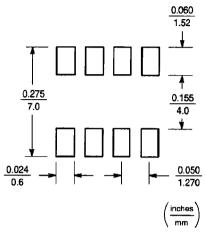

#### MINIMUM RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor packages must be the correct size to insure proper solder connection interface between the board and the package. With the correct pad geometry, the packages will self align when subjected to a solder reflow process.

SO-14

#### SO-14 POWER DISSIPATION

The power dissipation of the SO–14 is a function of the pad size. This can vary from the minimum pad size for soldering to a pad size given for maximum power dissipation. Power dissipation for a surface mount device is determined by  $T_{J(max)}$ , the maximum rated junction temperature of the die,  $R_{\theta,JA}$ , the thermal resistance from the device junction to ambient, and the operating temperature,  $T_A$ . Using the values provided on the data sheet for the SO–14 package,  $P_D$  can be calculated as follows:

$$P_D = \frac{T_{J(max)} - T_{A}}{R_{\theta,JA}}$$

The values for the equation are found in the maximum ratings table on the data sheet. Substituting these values into the equation for an ambient temperature T<sub>A</sub> of 25°C, one can calculate the power dissipation of the device which in this case is .5 watts.

$$P_D = \frac{150^{\circ}C - 25^{\circ}C}{250^{\circ}C/W} = .5 \text{ watts}$$

The 250°C/W for the SO–14 package assumes the use of the recommended footprint on a glass epoxy printed circuit board to achieve a power dissipation of .5 watts. There are other alternatives to achieving higher power dissipation from the SO–14 package. Another alternative would be to use a ceramic substrate or an aluminum core board such as Thermal Clad™. Using a board material such as Thermal Clad, an aluminum core board, the power dissipation can be doubled using the same footprint.

#### **SOLDERING PRECAUTIONS**

The melting temperature of solder is higher than the rated temperature of the device. When the entire device is heated to a high temperature, failure to complete soldering within a short time could result in device failure. Therefore, the following items should always be observed in order to minimize the thermal stress to which the devices are subjected.

- Always preheat the device.

- The delta temperature between the preheat and soldering should be 100°C or less.\*

- When preheating and soldering, the temperature of the leads and the case must not exceed the maximum temperature ratings as shown on the data sheet. When using infrared heating with the reflow soldering method, the difference shall be a maximum of 10°C.

- The soldering temperature and time shall not exceed 260°C for more than 10 seconds.

- When shifting from preheating to soldering, the maximum temperature gradient shall be 5°C or less.

- After soldering has been completed, the device should be allowed to cool naturally for at least three minutes.

Gradual cooling should be used as the use of forced cooling will increase the temperature gradient and result in latent failure due to mechanical stress.

- Mechanical stress or shock should not be applied during cooling.

- \* Soldering a device without preheating can cause excessive thermal shock and stress which can result in damage to the device.

**■** 6367255 0090631 225 **■**

4

Motorola Small-Signal Transistors, FETs and Diodes Device Data

# **PACKAGE DIMENSIONS**