# ■ MN102L62G

| Туре                               | MN102L62G<br>128 K<br>5 K                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| ROM (x8-bit / x16-bit)             |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| RAM (×8-bit / ×16-bit)             |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Package                            | LQFP100-P-1414 *Lead-free                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Minimum Instruction Execution Time | 100 ns (at 4.5 V to 5.5 V, 20 MHz)                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Interrupts                         | <ul> <li>RESET • Watchdog • Timer counter 0 to 5 • Timer counter 6 to 7</li> <li>• Timer counter 6 to 7 compare capture A • Timer counter 6 to 7 compare capture B</li> <li>• ATC transfer finish • External 0 to 4 • Serial ch.0, 1 transmission • Serial ch.0, 1 reception</li> <li>• NMI pin • A/D conversion finish</li> </ul>                      |  |  |  |  |  |  |

| Timer Counter                      | Timer counter 0: 8-bit × 1 (timer output, event count)  Clock source                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                    | Timer counter 1 : 8-bit × 1 (timer output, event count, A/D conversion start up)  Clock sourcesystem clock; 1/4 of low speed clock frequency; external clock; timer counter 0 output  Interrupt sourceunderflow of timer counter 1                                                                                                                      |  |  |  |  |  |  |

|                                    | Timer counter 2 to 3: 8-bit × 1 (timer output, event count, UART baud rate generator)  Clock source system clock; external clock; timer counter 0 output; timer counter 1, 2 output  Interrupt source underflow of timer counter 2, 3                                                                                                                   |  |  |  |  |  |  |

|                                    | Timer counter 4, 5: 8-bit × 1 (timer output, event count)  Clock source                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                    | Timer counter 6, 7: 16-bit × 1  (timer output, event count, input capture, output compare, PWM output, 2-phase encoder input)  Clock sourcesystem clock; external clock; timer counter 4, 5 output  Interrupt sourcecoincidence with compare capture A or at capture; coincidence with compare capture B or at capture; underflow of timer counter 6, 7 |  |  |  |  |  |  |

|                                    | Connectable timer counter 0 to 5                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Serial Interface                   | Serial 0:7, 8-bit × 1 (common use with UART, transfer direction of MSB/LSB selectable)  Clock source                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                    | Serial 1:7, 8-bit × 1 (common use with UART, transfer direction of MSB/LSB selectable)  Clock source                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                    | UART $\times$ 2 (common use with serial 0, 1)                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                                    | $I^2C \times 2$ (single master)                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| I/O Pins I/O                       | 80 • Common use : 16 (by 8 bits), 8 (by 4 bits), 56 (by bit)                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| A/D Inputs                         | 8-bit $\times$ 8-ch. (with S/H)                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| PWM                                | 16-bit × 2-ch.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Notes                              | Burst ROM inferface support, ATC (between serial 0ch and internal RAM) support                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

#### Electric Characteriatics

#### Supply current

| Parameter                | Symbol | Condition                                        | Limit |     |     | Unit  |

|--------------------------|--------|--------------------------------------------------|-------|-----|-----|-------|

| raidilletei              |        |                                                  | min   | typ | max | Oilit |

| Operating supply current | IDDopr | VI = VDD or VSS, output open                     |       |     | 75  | mA    |

|                          |        | f = 20 MHz , VDD = 5.0 V                         |       |     | 13  |       |

| Supply current at STOP   | IDDS   | Pin with pull-up resistor is open                |       | 50  |     | μA    |

|                          |        | all other input pins and Hi-Z state input/output |       |     |     |       |

| Supply current at HALT   | IDDH   | pins are simultaneously applied VDD or VSS level |       | 20  |     | A     |

|                          |        | f = 20 MHz , VDD = 5.0 V, output open            |       |     | 30  | mA    |

$(Ta = -40^{\circ}C \text{ to } +85^{\circ}C, VDD = 5.0 \text{ V}, VSS = 0 \text{ V})$

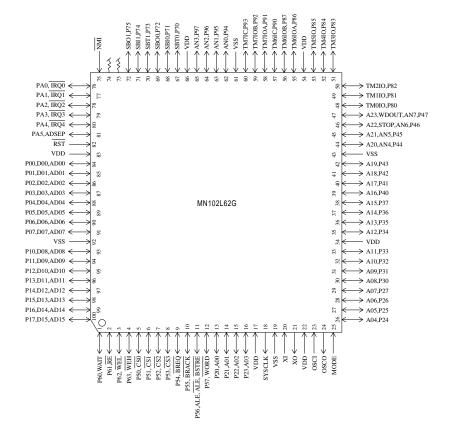

#### Pin Assignment

LQFP100-P-1414 \*Lead-free

### **Support Tool**

| In-circuit Emulator        | PX-ICE102L00 + PX-PRB102L25-LQFP100-P-1414 |                                  |  |

|----------------------------|--------------------------------------------|----------------------------------|--|

| EPROM Built-in Type        | Туре                                       | MN102LP25G                       |  |

|                            | ROM (× 8-bit / × 16-bit)                   | 128 K                            |  |

|                            | RAM (× 8-bit / × 16-bit)                   | 5 K                              |  |

|                            | Minimum instruction execution time         | 100 ns (4.5 V to 5.5 V , 20 MHz) |  |

|                            | Package                                    | LQFP100-P-1414 *Lead-free        |  |

| Flash Memory Built-in Type | Туре                                       | MN102LF25Z                       |  |

|                            | ROM (× 8-bit / × 16-bit)                   | 128 K                            |  |

|                            | RAM (× 8-bit / × 16-bit)                   | 3 K                              |  |

|                            | Minimum instruction execution time         | 100 ns (4.5 V to 5.5 V , 20 MHz) |  |

|                            | Package                                    | LQFP100-P-1414 *Lead-free        |  |

### MN102L62G □

## Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuits examples of the products. It neither warrants non-infringement of intellectual property right or any other rights owned by our company or a third party, nor grants any license.

- (3) We are not liable for the infringement of rights owned by a third party arising out of the use of the product or technologies as described in this material.

- (4) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (5) The products and product specifications described in this material are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (6) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage, and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (7) When using products for which damp-proof packing is required, observe the conditions (including shelf life and amount of time let standing of unsealed items) agreed upon when specification sheets are individually exchanged.

- (8) This material may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.